# ARTICLE OPEN

# Large-signal model of 2DFETs: compact modeling of terminal charges and intrinsic capacitances

Francisco Pasadas 61\*, Enrique G. Marin 62,3, Alejandro Toral-Lopez 62,4, Francisco G. Ruiz 62, Andrés Godoy 62,4, Saungeun Park5, Deji Akinwande5 and David Jiménez 61

We present a physics-based circuit-compatible model for double-gated two-dimensional semiconductor-based field-effect transistors, which provides explicit expressions for the drain current, terminal charges, and intrinsic capacitances. The drain current model is based on the drift-diffusion mechanism for the carrier transport and considers Fermi–Dirac statistics coupled with an appropriate field-effect approach. The terminal charge and intrinsic capacitance models are calculated adopting a Ward–Dutton linear charge partition scheme that guarantees charge conservation. It has been implemented in Verilog-A to make it compatible with standard circuit simulators. In order to benchmark the proposed modeling framework we also present experimental DC and high-frequency measurements of a purposely fabricated monolayer MoS<sub>2</sub>-FET showing excellent agreement between the model and the experiment and thus demonstrating the capabilities of the combined approach to predict the performance of 2DFETs.

npj 2D Materials and Applications (2019)3:47; https://doi.org/10.1038/s41699-019-0130-6

## **INTRODUCTION**

Since the emergence of graphene, over a surprisingly short period of time, an entire new family of two-dimensional materials (2DMs) has been discovered. Some of them are already used as channel materials in FETs, being promising candidates to augment silicon and III–V compound semiconductors via heterogeneous integration for advanced applications. In this context, the development of electrical models for 2D semiconductor-based FETs (2DFETs) is essential to: (1) interpret experimental results; (2) evaluate their expected digital/RF performance; (3) benchmark against existing technologies; and (4) eventually provide guidance for circuit design and circuit-level simulations.

Several compact models for three-terminal FETs based on graphene and related 2D materials (GRMs) have been recently published encompassing both static and dynamic regimes.<sup>2–10</sup> In particular, Suryavanshi et al.<sup>2</sup> proposed a semi-classical transport approach for the drain current combining the intrinsic FET behavior with models of the contact resistance, traps and impurities, quantum capacitance, fringing fields, high-field velocity saturation and self-heating. However, the dynamic regime is described using a charge model derived for bulk MOSFETs<sup>11</sup> that fails to capture the specific physics of the 2D channel, since it considers that the channel is always in a weak-inversion regime and therefore the channel charge can be assumed to be linearly distributed along the device. Wang et al.<sup>3</sup> reported on a compact model restricted to the static regime of graphene FETs and based on the "virtual-source" approach, valid for both the saturation and linear regions of device operation. Also based on the "virtualsource" approach, Rakheja et al.<sup>4</sup> studied quasi-ballistic graphene FETs. Nevertheless, they also employed the approximation derived for bulk MOSFETs<sup>11</sup> for the dynamic regime description even though the channel material considered is graphene. Jiménez early developed a model describing the drain current for single layer transition metal dichalcogenide (TMD) FETs based on surface potential and drift-diffusion approaches but the dynamic behavior of the TMD-FETs was not treated.<sup>5</sup> Also based on surface potential and drift-diffusion arguments, Parrish et al.<sup>6</sup> presented a compact model for graphene-based FETs for linear and non-linear circuits, but the dynamic regime description was roughly estimated by equally splitting the total gate capacitance between gate-drain and gate-source capacitances. A charge-based compact model for TMD-based FETs only valid for the static regime but simultaneously including interface traps, ambipolar current behavior, and negative capacitance was proposed by Yadav et al.<sup>7</sup> Taur et al.<sup>8</sup> presented an analytic drain current model for short-channel 2DFETs combining a subthreshold current model based on the solution to 2D Poisson's equation and a drift-diffusion approach to get an all-region static description. Rahman et al.<sup>9</sup> discussed a physics-based compact drain current model for monolayer TMD-FETs considering drift-diffusion transport description and the gradual channel approximation to analytically solve the Poisson's equation. Unfortunately, none of them faced the dynamic regime operation. Finally, Gholipour et al.<sup>10</sup> proposed a compact model that combines both the drift-diffusion and the Landauer-Buttiker approaches to properly describe the long- and short-channel FETs in flexible electronics, respectively. As a key feature, the mechanical bending is considered by linearly decreasing the channel material bandgap with respect to the applied strain. However, the capacitance model was roughly approximated by considering that the top (back) gate-drain and top (back) gatesource capacitances are just the geometrical top (back) gate capacitance. In summary, up to date the dynamic description of 2DFETs has been either roughly approximated or not specifically addressed for such devices. Our aim is to develop an accurate and physics-based compact model of the terminal charges and corresponding intrinsic capacitances of four-terminal (4T) 2DFETs valid for all operation regimes. In doing so, we present such a model together with the drain current equation, developed by

<sup>&</sup>lt;sup>1</sup>Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, 08193 Bellaterra (Cerdanyola del Vallès), Spain. <sup>2</sup>Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, 18071 Granada, Spain. <sup>3</sup>Dipartimento de Ingegneria dell'Informazione, Università di Pisa, 56122 Pisa, Italy. <sup>4</sup>Excellence Research Unit "Modeling Nature" (MNat), Universidad de Granada, 18071 Granada, Spain. <sup>5</sup>Department of Electrical and Computer Engineering, The University of Texas, Austin, TX 78758, USA. \*email: francisco.pasadas@uab.es

some of us,<sup>12</sup> based on drift-diffusion theory where the surface potential is the key magnitude of the model. So that, the combination of both approaches gives rise to a compact large-signal model suitable for commercial TCAD tools employed in the simulation of circuits based on 2DFETs. The model has been shown to reproduce with good agreement DC and high-frequency measurements of a fabricated *n*-type MoS<sub>2</sub>-based FET, and has been used to predict the output transient of a three-stage ring oscillator.

## **RESULTS**

Large-signal model of four-terminal 2DFETs

We first deal with the development of the large-signal model of 4T 2DFETs by the sequential formulation of the electrostatics, the drain current equation, the terminal charge model, and the corresponding intrinsic capacitance description.

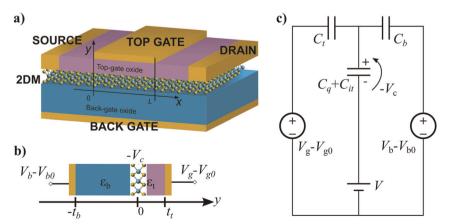

The cross-section of the considered dual-gated 2DFET is depicted in Fig. 1a. For the sake of brevity, we derive here the expressions for an n-type device (the extension to a p-type transistor can be obtained straightforwardly). Provided that the semiconductor bandgap is not too small, we can assume that  $p(x) \ll n(x)$  in all regimes of operation, where p(x) and n(x) are the hole and electron carrier densities, respectively. Upon application of 1D Gauss' law to the double-gate stack shown in Fig. 1b, the electrostatics can be described using the equivalent circuit depicted in Fig. 1c:

$$Q_{\rm net}(x) + Q_{\rm it}(x) = -C_{\rm t} \big( V_{\rm g} - V_{\rm g0} - V(x) + V_{\rm c}(x) \big) - C_{\rm b} (V_{\rm b} - V_{\rm b0} - V(x) + V_{\rm c}(x)), \label{eq:Qnet}$$

(1

where  $Q_{\rm net}(x)=q(p(x)-n(x))$  is the overall net mobile sheet charge density and q is the elementary charge.  $C_{\rm t}=\varepsilon_0\varepsilon_{\rm t}/t_{\rm t}$  ( $C_{\rm b}=\varepsilon_0\varepsilon_{\rm b}/t_{\rm b}$ ) is the top (back) oxide capacitance per unit area where  $\varepsilon_{\rm t}$  ( $\varepsilon_{\rm b}$ ) and  $t_{\rm t}$  ( $t_{\rm b}$ ) are the top (back) gate oxide relative permittivity and thickness, respectively; and  $V_{\rm g}-V_{\rm g0}$  ( $V_{\rm b}-V_{\rm b0}$ ) is the overdrive top (back) gate voltage. These latter quantities comprise workfunction differences between the gates and the 2D channel and any possible additional charges due to impurities or doping. The energy  $qV_{\rm c}(x)=E_{\rm c}(x)-E_{\rm F}(x)$  represents the shift of the quasi-Fermi level with respect to the conduction band edge and  $-qV(x)=E_{\rm F}(x)$  is the quasi-Fermi level along the channel. This latter quantity must fulfill the boundary conditions: (1)  $V(x=0)=V_{\rm s}$  (source voltage) at the source end; (2)  $V(x=L)=V_{\rm d}$  (drain voltage) at the drain end.

2D crystals are far from perfect and suffer from diverse nonidealities. In particular, interface traps are unavoidable in FETs, even for those processed by state-of-the-art CMOS technology, <sup>13</sup> impacting negatively the performance of 2DFETs. <sup>14</sup> Therefore, it is mandatory to include them in order to achieve an accurate predictive TCAD tool. For n-type devices, acceptor-like traps (which are negatively charged when occupied by electrons and are energetically located in the upper half of the bandgap<sup>15</sup>) contribute the most to the device electrical characteristics. Assuming the traps are situated at an effective energy  $E_{\rm it} = -qV_{\rm it}$  below the conduction band, the occupied trap density can be written as  $n_{\rm it} = N_{\rm it}/(1 + \exp(V_{\rm c} - V_{\rm it}/V_{\rm th}))$ , where  $N_{\rm it}$  is the effective trap density considered to be a delta function in energy. The trap charge density is then  $Q_{\rm it} = -qn_{\rm it}$  and the interface trap capacitance  $C_{\rm it}$  at the oxide–semiconductor interface (taken as a combination from both interfaces of the ultra-thin 2D channel) can be computed as:

$$C_{it} = \frac{dQ_{it}}{dV_c} = \frac{qN_{it}}{2V_{th}} \frac{1}{1 + \cosh\left(\frac{V_c - V_{it}}{V_{th}}\right)},$$

(2)

where  $V_{\rm th}=k_{\rm B}T/q$  is the thermal voltage,  $k_{\rm B}$  is the Boltzmann constant, and T is the temperature. The term  $C_{\rm it}$  adds to the quantum capacitance  $C_{\rm qr}$  as shown in Fig. 1c.

We can, thus, find an expression to calculate the overall net mobile sheet density assuming a parabolic dispersion relationship modeled in the effective mass approximation and using Fermi–Dirac statistics<sup>12</sup>:

$$Q_{\rm net}(x) = -qn(x) = -C_{\rm dq}V_{\rm th}u(V_{\rm c}); \quad u(V_{\rm c}) = \, \ln\Bigl(1 + e^{-\frac{V_{\rm c}}{V_{\rm th}}}\Bigr), \quad (3)$$

where  $C_{\rm dq}=q^2D_0$  is defined as the degenerated-quantum capacitance, which corresponds to the upper-limit achievable when the 2D carrier density becomes heavily degenerated.  $^{17}D_0=g_K(m^K/2\pi\hbar^2)+g_Q(m^Q/2\pi\hbar^2)\exp[-\Delta E_2/k_BT]$  is the 2D density of states, with  $\hbar$  being the reduced Planck's constant,  $g_K$  ( $g_Q$ ) the degeneracy factor and  $m^K$  ( $m^Q$ ) the conduction band effective mass at the K (Q) band valley. In most TMDs, the second conduction valley, labeled as Q valley, is non-negligible since the energy separation between the K and Q conduction valleys,  $\Delta E_2$ , is only around  $2k_BT$ . Thus, two conduction band valleys may participate in the transport process. The rest of valleys are, on the contrary, far away in energy to contribute to the electrical conduction,  $^{20}$  and hence can be neglected for practical purposes.

The quantum capacitance of the 2DM can be computed by evaluating  $C_q = dQ_{\rm net}/dV_{\rm c}$  resulting in:

$$C_q = C_{dq}(1 - e^{-u}).$$

(4)

Due to the complexity of Eq. (1) and considering the relation between  $Q_{\rm net}$  and  $V_{\rm c}$  given by Eq. (3), it is not possible to get an explicit expression for  $V_{\rm c}$  as a function of the applied bias. However, an iterative Verilog-A algorithm can be implemented to evaluate the chemical potential at the source and drain edges,

Fig. 1 a Cross-section of the 2DFET considered in the modeling framework. A 2DM plays the role of the active channel. b Scheme of the 2DM-based capacitor showing the relevant physical and electrical parameters. c Equivalent capacitive circuit of the 2DFET.

which are the relevant quantities determining the drain current. In doing so,  $V_{cs} = V_{c}|_{V=Vs}$  and  $V_{cd} = V_{c}|_{V=Vd}$  are obtained, respectively, from Eqs. (1) and (3) by a construct<sup>21,22</sup> which lets the circuit simulator to iteratively solve both equations during run-time.

In the diffusive regime, the drain current of a 2DFET can be accurately computed by the following compact expression<sup>12</sup>:

$$I_{ds} = \mu \frac{W}{L} C_{dq} V_{th}^2 \left[ \left( 1 + \frac{C_{dq}}{C_{tb}} \right) \left( \frac{u_s^2 - u_d^2}{2} \right) + (e^{-u_d} - e^{-u_s}) \right], \tag{5}$$

where  $u_{\rm s}=u(V_{\rm cs})$  and  $u_{\rm d}=u(V_{\rm cd})$ ;  $C_{\rm tb}=C_{\rm t}+C_{\rm b}$ ; W and L are the device width and length, respectively; and  $\mu$  is the carrier mobility which has been assumed to be dependent of the applied electric field, carrier density, and temperature as in ref. <sup>2</sup> Once we have a suitable expression for describing the static behavior of the device, the dynamic response must be analyzed to build a large-signal model. In doing so, the terminal currents in the time domain can be computed as:

$$i_k(t) = \frac{dQ_k}{dt} = C_{kg} \frac{dv_g}{dt} + C_{kd} \frac{dv_d}{dt} + C_{ks} \frac{dv_s}{dt} + C_{kb} \frac{dv_b}{dt}, \qquad (6)$$

where k stands for g, d, s, and b, i.e. top gate, drain, source and back-gate, respectively. The terminal currents, thus, can be obtained by either computing the time derivative of the corresponding terminal charge or by the weighted sum of the time derivative of the terminal voltages, where the weights are given by the intrinsic capacitances.

The intrinsic capacitances of FETs are modeled in terms of the terminal charges. Specifically, from the electrostatics given in Eq. (1) the following relations are derived<sup>23</sup>:

$$Q_{\rm gb} = Q_{\rm g} + Q_{\rm b} = -W \int_0^L Q_{\rm net}(x) dx,$$

(7)

$$Q_{\rm g} = Q_0 - \frac{WC_{\rm t}}{C_{\rm th}} \int_0^L Q_{\rm net}(x) \mathrm{d}x, \tag{8}$$

$$Q_{\rm b} = -Q_0 - \frac{WC_{\rm b}}{C_{\rm th}} \int_0^L Q_{\rm net}(x) \mathrm{d}x,\tag{9}$$

where  $Q_0 = WLC_tC_b(V_g - V_{g0} - V_b + V_{b0})/C_{tb}$ . The charge controlled by both the drain and source terminals is computed based on the Ward–Dutton's linear charge partition scheme,<sup>24</sup> which guarantees charge conservation:

$$Q_{\rm d} = W \int_0^L \frac{1}{L} Q_{\rm net}(x) dx, \tag{10}$$

$$Q_{\rm s} = -(Q_{\rm g} + Q_{\rm b} + Q_{\rm d}) = W \int_0^L (1 - \frac{x}{L}) Q_{\rm net}(x) dx.$$

(11)

The above expressions can be conveniently written using u as the integration variable, as it was done to model the drain current in Eq. (5). Based on the fact that the drain current is the same at any point x along the channel (i.e. we are under the *quasi-static* approximation framework), we get from the transport model the following equations needed to evaluate the charges in Eqs. (7)–(11):

$$dx = \frac{\mu W}{l_{ds}} Q_{tot}(u) \frac{dV}{dV_c} \frac{dV_c}{du} du$$

$$x = \frac{\mu W}{l_{ds}} \left[ \int_{u_s}^{u} Q_{tot}(u) \frac{dV}{dV_c} \frac{dV_c}{du} du \right].$$

(12)

Replacing Eq. (12) in Eqs. (7) and (10), the following compact expressions are obtained for the terminal charges  $Q_{ab}$  and  $Q_{d}$ :

$$\begin{split} Q_{\rm gb} &= Q_{\rm 2D} \frac{2 \left(3 C_{\rm tb} (e^{\mu_{\rm d}} (1+u_{\rm s}) - e^{\mu_{\rm s}} (1+u_{\rm d})) + e^{\mu_{\rm s}} e^{\mu_{\rm d}} \left(C_{\rm dq} + C_{\rm tb}\right) \left(u_{\rm d}^3 - u_{\rm s}^3\right)\right)}{6 C_{\rm tb} (e^{\mu_{\rm d}} - e^{\mu_{\rm s}}) + 3 e^{\mu_{\rm s}} e^{\mu_{\rm d}} \left(C_{\rm dq} + C_{\rm tb}\right) \left(u_{\rm d}^2 - u_{\rm s}^2\right)}, \\ Q_{\rm d} &\approx -Q_{\rm 2D} \frac{2}{15} \frac{3 u_{\rm s}^5 - 5 u_{\rm d}^3 u_{\rm s}^2 + 2 u_{\rm s}^5}{\left(u_{\rm d}^2 - u_{\rm s}^2\right)^2}, \end{split} \tag{13}$$

where  $Q_{2D} = WLC_{dq}V_{th}$ . Equation (13) can be replaced in Eqs. (8),

(9) and (11) to get the terminal charges  $Q_{\rm g}$ ,  $Q_{\rm b}$ , and  $Q_{\rm s}$ , respectively.  $Q_{\rm d}$  in Eq. (13) has been simplified by assuming that the term  ${\rm e}^{(2ud+2us)}$  is prevalent over other low-order terms, e.g.,  $e^{ud}$  and  $e^{us}$ .

Once the terminal charges are evaluated, a four-terminal FET can be modeled with 4 self-capacitances and 12 intrinsic transcapacitances given by:

$$C_{ij} = -\frac{\partial Q_i}{\partial V_j}$$

$i \neq j$   $C_{ij} = \frac{\partial Q_i}{\partial V_j}$   $i = j$   $i, j = g, d, s, b,$  (14)

where  $C_{ij}$  describes the dependence of the charge at terminal i with respect to a varying voltage applied to terminal j assuming that the voltage at any other terminal remains constant. Due to charge conservation and considering a reference-independent model, only nine independent capacitances are needed to describe the 4T device. In addition, taking advantage of the relations between the top- and back-gate capacitances, the computation of only four capacitances is enough; for instance,  $C_{gg}$ ,  $C_{ad}$ ,  $C_{dg}$ , and  $C_{dd}$  can be chosen as the independent set.

#### Model validation

In order to validate the presented model, we perform the DC and RF measurements of an experimental monolayer  $MoS_2$ -FET. The fabricated device consists of an n-type channel of a chemical vapor deposited (CVD)  $MoS_2$  monolayer transferred onto 285 nm intrinsic  $Si/SiO_2$  wafer. The 150-nm-long  $MoS_2$  channel is contacted with a stack of 2/70 nm Cr/Au and electrostatically controlled by an embedded gate formed by a 10-nm barrier of atomic layer deposited  $Al_2O_3$  and a gate metal stack consisting of 2/23 nm Ti/Au. More details on the fabrication and characterization process can be found in the Methods section. Table 1 summarizes the input parameters used for simulating the device under test. The extracted 2D semiconductor–metal contact resistance for the device is  $3.5 \ k\Omega \ \mu m$  and has been included in the simulation by connecting lumped resistors to the source and drain terminals.

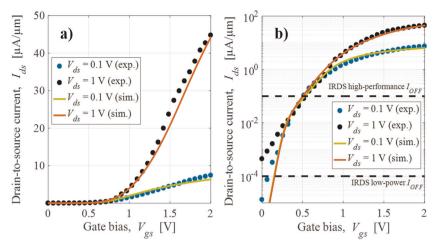

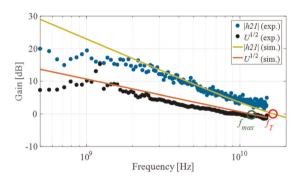

We first test our model by comparing the DC transfer characteristics (TCs) obtained at two different drain voltages. A good agreement between both, measurements and simulations, has been achieved as shown in Fig. 2. The model predicts the DC behavior accurately in all regimes of operation with current values ranging between  $10^{-3}$  up to  $10^2 \,\mu\text{A}/\mu\text{m}$ . However, the experimental device departs from the exponential trend for values in the limit of the IRDS specification for low-power applications, being the OFF current actually limited by the onset of hole current at negative  $V_{gs}$  (see Supplementary Notes and Supplementary Fig. S1 for a detailed discussion). This small mismatch, however, does not impact the dynamic operation prediction. Indeed, we have assessed the expected RF performance of such device in Fig. 3 by benchmarking the simulated small-signal current gain (h21) and unilateral power gain (U) against the results extracted from

| Table 1.          | Input parameters of the 2DFET under test. |                       |                                     |

|-------------------|-------------------------------------------|-----------------------|-------------------------------------|

| L                 | 150 nm                                    | $\mu_0$               | 21.2 cm <sup>2</sup> /Vs            |

| W                 | 10 µm                                     | $m^{K}$ <sup>26</sup> | 0.48 <i>m</i> <sub>0</sub>          |

| Lt                | 10 nm                                     | $m^{Q}$ <sup>26</sup> | 0.57 <i>m</i> <sub>0</sub>          |

| $L_{b}$           | 285 nm                                    | $m_0$                 | $9.11 \times 10^{-31} \mathrm{kg}$  |

| $\varepsilon_t$   | 9                                         | $g_{\kappa}^{27}$     | 2                                   |

| $\varepsilon_{b}$ | 3.9                                       | $g_Q^{27}$            | 6                                   |

| $V_{g0}$          | 0.42 V                                    | $\Delta E_2^{18}$     | 0.11 eV                             |

| $V_{\rm b0}$      | 0 V                                       | $N_{it}$              | $1.8 \times 10^{16}  \text{m}^{-2}$ |

| Т                 | 300 K                                     | $V_{\mathrm{it}}$     | 0.085 eV                            |

Fig. 2 Transfer characteristics for different drain voltages in **a** linear and **b** logarithmic scales. Simulations are plotted with solid lines, and experimental measured data with symbols. Dashed lines in **b** highlight both the IRDS high-performance and low-power I<sub>OFF</sub> current limits.

**Fig. 3** Simulated (solid line) and measured (symbols) RF performance of the MoS<sub>2</sub>-based FET described in Table 1 ( $V_{\rm gs}=4.4\,\rm V$ ;  $V_{\rm ds}=3.5\,\rm V$ ). The device shows a cut-off frequency  $f_{\rm T}=20.2\,\rm GHz$  and a maximum oscillation frequency  $f_{\rm max}=11.3\,\rm GHz$ .

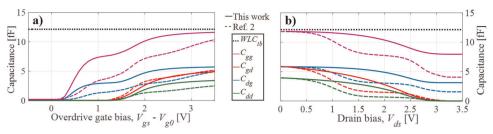

the experimental S-parameters (after de-embedding) measured in the range 0.1-15 GHz. Both, simulated h21 and U, are predicted with excellent agreement to the experimental measurements. In order to evaluate the RF performance, we calculate the intrinsic capacitances, plotted in Fig. 4 (solid lines). The relative error between the numerical solution of Eq. (14) by using the expressions in Eqs. (8)-(11) and the analytical computation of Eq. (14) by using the compact expressions in Eq. (13) is less than 2% for the bias window considered in Fig. 4. The results are presented together with the intrinsic capacitances relying on the well-known conventional charge model developed for bulk MOSFETs<sup>11</sup> and elsewhere used to model 2DFETs<sup>2</sup>. As can be seen, the latter is accurate only either when a low drain bias is applied or if the device is operated in the subthreshold regime (see Supplementary Notes and Supplementary Fig. S2 for more details).

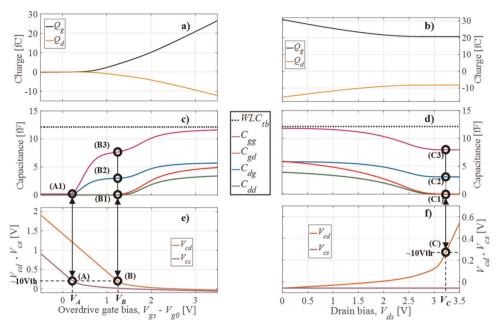

The trends in the intrinsic capacitances can be better understood looking at the overdrive gate and drain bias dependences of both gate  $(Q_{\rm g})$  and drain  $(Q_{\rm d})$  charges, which are depicted in Fig. 5a, b, respectively. Figure 5c, d shows the same bias dependence of a set of four independent intrinsic capacitances of the 4T 2DFET under test. As the device is an n-type transistor, we have also plotted the shift of the quasi-Fermi level with respect to the conduction band edge at both the drain/source sides (corresponding to the chemical potentials  $V_{\rm cd}$  and  $V_{\rm cs}$ ) in Fig. 5e, f. For the sake of clarity, we provide a separate discussion of the intrinsic capacitances according to the transistor operation regime.

Subthreshold regime (OFF operation): If both  $V_{\rm cd}$  and  $V_{\rm cs} > 10V_{\rm th}$ , then  $Q_{\rm g}$ ,  $Q_{\rm d} \sim 0$  (see Fig. 5a). Therefore the channel is empty of

carriers and the device operates in the OFF state. This situation happens for overdrive gate biases lower than the threshold voltage,  $V_A$ , according to Fig. 5e. Given the aforementioned conditions then  $C_{\rm gg} \approx C_{\rm t} C_{\rm b} W L / C_{\rm tb}$  and  $C_{\rm gd} \approx C_{\rm dg} \approx C_{\rm dd} \approx 0$ , see to the left of A1 point in Fig. 5c.

Saturation regime (ON operation): On the other hand, when  $V_{cd} > 10V_{th}$  while  $V_{cs} < 10V_{th}$ , the pinch-off is originated at the drain side. This situation is produced for overdrive gate biases between  $V_A$  and  $V_B$  in Fig. 5e ("A–B" section). Both  $C_{qq}$  ("A1–B3" section) and  $C_{dq}$  ("A1-B2" section) jump because the channel charge at the source side becomes very sensitive to the Fermi level location when it is close to the conduction band edge. However,  $C_{ad}$  and  $C_{dd}$  are negligible ("A1-B1" section) because the depletion region close to the drain prevents this terminal to control the channel charge. The saturation regime is also observed at the right column of Fig. 5 for drain biases higher than  $V_C$  (drain saturation voltage) in Fig. 5f (right of C point). The intrinsic capacitances  $C_{gg}$  (right of C3 point) and  $C_{dg}$  (right of C2 point), shown in Fig. 5d, decrease with respect to the linear regime (left of C point, explained below) because the channel is depleted at the drain side, so both  $Q_{\rm g}$  and  $Q_{\rm d}$  become less sensitive to  $V_{\rm qs}$  as compared to the linear regime. On the other hand,  $C_{qd}$  and  $C_{dd}$  are negligible (right of C1 point), as  $Q_g$  and  $Q_d$  cannot be controlled anymore by the drain terminal after the depletion of the channel drain side, which is confirmed in Fig. 5b.

Linear (ohmic) regime (ON operation): This regime takes place when both  $V_{\rm cd}$  and  $V_{\rm cs} < 10V_{\rm th}$ . This situation is produced for gate overdrive voltages higher than  $V_{\rm B}$  in Fig. 5e (right of B point), where the channel starts to leave the depletion scenario at the drain side. Then a jump is observed in  $C_{\rm gg}$  (right of B3 point),  $C_{\rm dg}$  (right of B2 point),  $C_{\rm gd}$  and  $C_{\rm dd}$  (right of B1 point) as a consequence of the recovered electrical connection between the channel and the drain terminal (see Fig. 5a, c). The linear regime can be also observed at the right column of Fig. 5 for drain biases lower than  $V_C$  (see Fig. 5f). The negative value of  $V_{\rm cs}$  means that the channel is degenerated at the source side for the specific bias considered in this study. In Fig. 5d, it can be seen that  $C_{\rm gg}$  (left of C3 point),  $C_{\rm dg}$  (left of C2 point),  $C_{\rm gd}$  and  $C_{\rm dd}$  (left of C1 point) decrease with  $V_{\rm ds}$  as the channel get closer to the drain depletion condition reached at  $V_{\rm ds} = V_C$ .

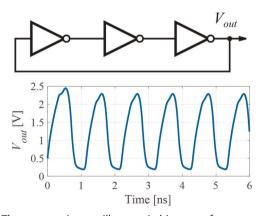

Finally, with the aim of showing the potential of the developed TCAD tool, a relevant circuit commonly used to evaluate the performance of a digital technology, namely, a ring oscillator (RO) is simulated. The design of a three-stage based RO encompasses both DC and transient simulations. Each device has been described by the parameters shown in Table 1 that have been demonstrated to accurately reproduce the fabricated MoS<sub>2</sub>-based

Fig. 4 Intrinsic capacitances versus **a** overdrive gate bias (at  $V_{ds} = 1 \text{ V}$ ) and **b** drain bias (at  $V_{gs} - V_{g0} = 3.4 \text{ V}$ ). Solid lines represent our model outcome and dashed lines show the data calculated using the model adopted in ref.<sup>2</sup>

**Fig. 5** Gate and drain charges versus **a** overdrive gate bias (at  $V_{ds} = 1 \text{ V}$ ) and **b** drain bias (at  $V_{gs} - V_{g0} = 3.4 \text{ V}$ ). Intrinsic capacitances versus **c** overdrive gate bias (at  $V_{ds} = 1 \text{ V}$ ) and **d** drain bias (at  $V_{gs} - V_{g0} = 3.4 \text{ V}$ ). Shift of the Fermi level with respect to the conduction band edge, namely, the chemical potential at the drain ( $V_{cd}$ ) and source ( $V_{cs}$ ) sides versus **e** overdrive gate bias (at  $V_{ds} = 1 \text{ V}$ ) and **f** drain bias (at  $V_{gs} - V_{g0} = 3.4 \text{ V}$ ).

**Fig. 6** Three-stage ring oscillator switching at a frequency around 1 GHz based on the 2DFETs described in Table 1. The supply bias is 3.5 V.

FET in Figs. 2 and 3. Specifically, we have designed the three-stage RO to oscillate at a specific frequency  $f_{\rm osc}=3^{1/2}/(2\pi R_{\rm dd}C)\approx 1$  GHz by using a resistor connected to each drain of  $R_{\rm dd}=20.4~{\rm k}\Omega$  and capacitors connected to the output of each stage with C=13.5 fF. In doing so, each single stage has been designed to show a

voltage gain of 3.7 at  $f_{\rm osc}$ , upon biasing it at  $V_{\rm gs} = 1.25$  V and  $V_{\rm ds} = 3.5$  V. Figure 6 shows how the technology assessed in this work provides a suitable switching characteristic around 1 GHz. The simulation predicts a distorted sinusoidal as the AC component goes over a large range of bias with imperfect linearity. It is worth noticing that a small-signal model (in contrast with a large-signal model) could not predict that feature. Supplementary Fig. S3 provides a comparison of the compact model outcome against experimental measurements of bilayer MoS $_2$  FETs $^{26}$  comprising the assessment of transfer characteristics, output characteristics, the performance of an inverter, and a five-stage ring oscillator based on such devices, the latter validating the large-signal prediction capability of the model.

# **DISCUSSION**

A physics-based large-signal compact model of four-terminal 2D semiconductor-based FETs, implemented in Verilog-A, has been presented. The model captures the terminal charges and capacitances covering all the operation regimes, so accurate time domain simulations and frequency response studies at the circuit level are feasible within the validity of the quasi-static approximation. The model can be incorporated to existing commercial circuit simulators enabling the simulation of digital and RF applications based on emerging 2D technologies. We have checked that the

model outcome is consistent with our experimental measurements of  $MoS_2$ -FET devices targeting RF applications. Finally, a design of a three-stage ring oscillator has been carried out to exhibit the potential of the TCAD tool presented and showing the feasibility of using this technology in switching applications in the gigahertz range.

#### **METHODS**

### **Fabrication**

The  ${\rm MoS}_2$  FET reported in this paper belongs to the same batch as the devices published in ref.  $^{27}$  by some of the authors. The fabrication process begins with patterning two embedded gate fingers on intrinsic  ${\rm Si/SiO}_2$  (>20 k $\Omega$  cm). Then, the embedded 150-nm gate metal stack consisting of 2/23 nm  ${\rm Ti/Au}$  was defined and deposited by using electron beam lithography (EBL) and e-beam evaporation. Large area atomic single layer CVD  ${\rm MoS}_2$ , grown by a standard vapor transfer process as described in ref.,  $^{27}$  was then transferred by poly(methyl methacrylate)-assisted wet transfer. Phosphoric acid etching was used to connect the embedded gate fingers and the gate pad. The active  ${\rm MoS}_2$  channel was etched using  ${\rm Cl}_2/{\rm O}_2$  plasma. Finally, source and drain (S/D) contacts consisting of 2/70 nm Cr/Au were patterned through a final EBL step.

#### Electrical measurements

The electrical DC characterization was done on a Cascade Microtech Summit 11000B-AP probe-station using an Agilent B1500A parameter analyzer. Microwave performance was characterized using an Agilent two-port vector network analyzer (VNA-E8361C). All measurements were taken at room temperature, in ambient atmosphere, and in the dark. The intrinsic microwave performance is obtained after de-embedding the measured data using OPEN and SHORT structures. The OPEN de-embedding was performed on the as-measured device-under-test by etching away the MoS<sub>2</sub> in the active regions. The SHORT de-embedding is subsequently carried out by depositing a strip of metal across the channel region, shorting out all pads.

### Circuit simulations

The developed large-signal model of 4T 2DFETs is implemented in Verilog-A and included as a separate module in Keysight© Advanced Design System (ADS), a popular electronic design automation software for RF and microwave applications. It calculates the electrostatics by iteratively solving Eqs. (1) and (3) during run-time using a construct,<sup>21,22</sup> and computes the static and dynamic response of the device by evaluating Eqs. (5) and (6), respectively, using the compact expressions derived in this work.

### **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## **CODE AVAILABILITY**

The large-signal model of 2DFETs implemented in Verilog-A is available from the corresponding author upon reasonable request.

Received: 2 July 2019; Accepted: 13 November 2019; Published online: 04 December 2019

#### **REFERENCES**

- Choi, W. et al. Recent development of two-dimensional transition metal dichalcogenides and their applications. *Mater. Today* 20, 116–130 (2017).

- Suryavanshi, S. V. & Pop, E. S2DS: physics-based compact model for circuit simulation of two-dimensional semiconductor devices including non-idealities. *J. Appl. Phys.* 120, 1–10 (2016).

- Han Wang, Hsu, Jing Kong, A., Antoniadis, D. A. & Palacios, T. Compact virtualsource current–voltage model for top- and back-gated graphene field-effect transistors. *IEEE Trans. Electron Devices* 58, 1523–1533 (2011).

- Rakheja, S. et al. An ambipolar virtual-source-based charge-current compact model for nanoscale graphene transistors. IEEE Trans. Nanotechnol. 13, 1005–1013 (2014).

- Jiménez, D. Drift-diffusion model for single layer transition metal dichalcogenide field-effect transistors. Appl. Phys. Lett. 101, 243501 (2012).

- Parrish, K. N., Ramón, M. E., Banerjee, S. K. & Akinwande, D. A Compact model for graphene FETs for linear and non-linear circuits. In 17th International Conference on Simulation of Semiconductor Processes and Devices. SISPAD, Denver, CO, USA, 75–78 (2012).

- Yadav, C., Rastogi, P., Zimmer, T. & Chauhan, Y. S. Charge-based modeling of transition metal dichalcogenide transistors including ambipolar, trapping, and negative capacitance effects. *IEEE Trans. Electron Devices* 65, 4202–4208 (2018).

- Taur, Y., Wu, J. & Min, J. A short-channel I-V model for 2-D MOSFETs. IEEE Trans. Electron Devices 63, 2550–2555 (2016).

- Rahman, E., Shadman, A., Ahmed, I., Khan, S. U. Z. & Khosru, Q. D. M. A physically based compact *I–V* model for monolayer TMDC channel MOSFET and DMFET biosensor. *Nanotechnology* 29, 235203 (2018).

- Gholipour, M., Chen, Y.-Y. & Chen, D. Compact modeling to device- and circuitlevel evaluation of flexible TMD field-effect transistors. *IEEE Trans. Comput. Des. Integr. Circuits Syst.* 37, 820–831 (2018).

- 11. Tsividis, Y. Operation and Modeling of the MOS Transistor (Oxford: Oxford University Press, New York, 1999).

- Marin, E. G., Bader, S. J. & Jena, D. A new holistic model of 2-D semiconductor FETs. IEEE Trans. Electron Devices 65, 1239–1245 (2018).

- 13. Grasser, T. Stochastic charge trapping in oxides: from random telegraph noise to bias temperature instabilities. *Microelectron. Reliab.* **52**, 39–70 (2012).

- Illarionov, Y. Y. et al. The role of charge trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN field-effect transistors. 2D Mater. 3, 035004 (2016).

- Knobloch, T. et al. A physical model for the hysteresis in MoS 2 transistors. IEEE J. Electron Devices Soc. 6, 972–978 (2018).

- Cao, W., Kang, J., Bertolazzi, S., Kis, A. & Banerjee, K. Can 2D-nanocrystals extend the lifetime of floating-gate transistor based nonvolatile memory? *IEEE Trans. Electron Devices* 61, 3456–3464 (2014).

- Ma, N. & Jena, D. Carrier statistics and quantum capacitance effects on mobility extraction in two-dimensional crystal semiconductor field-effect transistors. 2D Mater. 2, 015003 (2015).

- Kormányos, A. et al. k · p theory for two-dimensional transition metal dichalcogenide semiconductors. 2D Mater. 2, 022001 (2015).

- Rasmussen, F. A. & Thygesen, K. S. Computational 2D materials database: electronic structure of transition-metal dichalcogenides and oxides. *J. Phys. Chem. C* 119, 13169–13183 (2015)

- Kadantsev, E. S. & Hawrylak, P. Electronic structure of a single MoS2 monolayer. Solid State Commun. 152, 909–913 (2012).

- Landauer, G. M., Jiménez, D. & González, J. L. An accurate and Verilog-A compatible compact model for graphene field-effect transistors. *IEEE Trans. Nanotechnol.* 13, 895–904 (2014).

- Deng, J. D. J. & Wong, H.-S. P. A compact SPICE model for carbon-nanotube fieldeffect transistors including nonidealities and its application—Part I: model of the

intrinsic channel region. *IEEE Trans. Electron Devices* 54, 3186–3194 (2007).

- Pasadas, F. & Jiménez, D. Large-Signal model of graphene field-effect transistors

—Part I: Compact modeling of GFET intrinsic capacitances. IEEE Trans. Electron Devices 63, 2936–2941 (2016).

- Ward, D. E. & Dutton, R. W. A charge-oriented model for MOS transistor capacitances. *IEEE J. Solid-State Circuits* 13, 703–708 (1978).

- Pasadas, F. & Jimenez, D. Erratum to "large-signal model of graphene field-effect transistors—Part I: Compact modeling of GFET intrinsic capacitances" [Jul 16 2936-2941]. IEEE Trans. Electron Devices 66, 2459–2459 (2019).

- Wang, H. et al. Integrated circuits based on bilayer MoS 2 transistors. Nano Lett. 12, 4674–4680 (2012).

- Sanne, A. et al. Embedded gate CVD MoS2 microwave FETs. npj 2D Mater. Appl. 1, 26 (2017).

#### **ACKNOWLEDGEMENTS**

The authors would like to thank the financial support of Spanish Government under projects TEC2017-89955-P (MINECO/AEI/FEDER, UE), TEC2015-67462-C2-1-R (MINECO), and RTI2018-097876-B-C21 (MCIU/AEI/FEDER, UE). F.P. and D.J. also acknowledge the support from the European Union's Horizon 2020 Research and Innovation Program under Grant Agreement No. 785219 GrapheneCore2. A.G. acknowledges the funding by the Consejería de Economía, Conocimiento, Empresas y Universidad de la Junta de Andalucía and European Regional Development Fund (ERDF), ref. SOMM17/6109/UGR. E.G.M. gratefully acknowledges Juan de la Cierva Incorporación IJCI-2017-32297 (MINECO/AEI). A.T.-L. acknowledges the FPU program (FPU16/04043). D.A. acknowledges the Army Research Office for partial support of this work, and the NSF NASCENT ERC and NNCI programs.

#### **AUTHOR CONTRIBUTIONS**

F.P. and D.J. performed the development of the analytic model and the Verilog-A implementation. F.P., E.G.M., A.T.-L., and F.G.R. contributed to perform and interpreting the simulations. A.G. and D.J. overall supervised the compact model development and analyzed the results. S.P. performed the synthesis and characterization of the MoS<sub>2</sub> films, as well as performed the design conception, fabrication, and measurements of the MoS<sub>2</sub> transistors under the direction and supervision of D.A. F.P., and D.J. wrote the manuscript. F.P., E.G.M., F.G.R., A.G., D.A., and D.J. contributed to the scientific discussions. All authors revised and approved the final manuscript.

#### **COMPETING INTERESTS**

The authors declare no competing interests.

# **ADDITIONAL INFORMATION**

**Supplementary information** is available for this paper at https://doi.org/10.1038/s41699-019-0130-6.

Correspondence and requests for materials should be addressed to F.P.

**Reprints and permission information** is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2019