# Pyramidal architecture for stereo vision and motion estimation in real-time FPGA-based devices

Matteo Tomasi Departamento de Arquitectura y Tecnología de Computadores Universidad de Granada

> A thesis submitted for the degree of PhilosophiæDoctor (PhD) in Computer Science

> > May 2010

Editor: Editorial de la Universidad de Granada Autor: Matteo Tomasi D.L.: GR 3189-2010 ISBN: 978-84-693-4303-6

ii

# Declaration

Dr. Eduardo Ros Vidal, Catedrático de Universidad, y Dr. Javier Díaz Alonso, Profesor Ayudante Doctor de Universidad, ambos del Departamento de Arquitectura y Tecnología de Computadores de la Universidad de Granada,

CERTIFICAN:

Que la memoria titulada "Pyramidal architecture for stereo vision and motion estimation in real-time FPGA-based devices", ha sido realizada por D. Matteo Tomasi bajo nuestra dirección en el Departamento de Arquitectura y Tecnología de Computadores de la Universidad de Granada para optar al grado de Doctor por la Universidad de Granada.

Granada, 14 de Mayo 2010

Fdo. Eduardo Ros Vidal

Fdo. Javier Díaz Alonso

## Abstract

In this work, an exhaustive study for a low level vision engine is presented. Our hypothesis is based on recent development and advantages of FPGA devices (reduced power consumption, high processing capabilities) and the performance of new HDLs and synthesis tools. Thus we address with these powerful means the novel target of a low level vision engine on the same chip. The study aims to demonstrate that is possible the integration of multiple complex algorithms thanks to a proper adaptation and good design techniques. In particular we focus our architecture to a fine grain pipeline in opposition to the multi-core approach largely used in last architectures. Our approach benefits the power consumption and the size of the final implementation providing a very competitive system useful for industrial, robotic and research fields. For the first time is afforded a multi-scale and a multi-orientation optical flow and stereo on FPGA. The iterative nature of this approach degrades the processing speed but achieves an important accuracy and significantly enhances the working range. Final results in synthetic and real sequences demonstrate the competitive performance of the presented system.

To my family

# Acknowledgements

I would like to acknowledge all people that with more or less contribution helped me in these years. Without their presence my work it would be impossible. I would remember all of them but in few pages it is a very difficult task. For this reason I express a first enormous "THANKS" to all persons that in my opinion can be considered as a little brick for the building of this work. However it is important for me to mention some of them. In a special way I would like to acknowledge my thesis directors Edu and Javi for their charisma. They give me the possibility of a very fruitful research and they attend to me with patience. Thanks also to all the ATC department in special way to the "CIE" group. I would like to acknowledge all the DRIVSCO members for their example and great scientific contribution.

# Contents

| List of Figures v |      |        | vii                                                                                  |    |

|-------------------|------|--------|--------------------------------------------------------------------------------------|----|

| List of Tables    |      | 5      | ix                                                                                   |    |

| 1                 | Intr | oducti | ion                                                                                  | 1  |

|                   | 1.1  | Vision | Framework                                                                            | 2  |

|                   | 1.2  | Vision | processing platforms: State of the Art                                               | 3  |

|                   | 1.3  | Our co | ontribution                                                                          | 7  |

|                   | 1.4  | Projec | t Framework                                                                          | 9  |

|                   | 1.5  | Outlin | e                                                                                    | 9  |

| <b>2</b>          | Pre  | limina | ry study towards a Hardware implementation                                           | 11 |

|                   | 2.1  | Optica | al flow and stereo computational models review                                       | 11 |

|                   |      | 2.1.1  | Reference optical flow computation model                                             | 16 |

|                   |      | 2.1.2  | Reference binocular disparity computation model                                      | 18 |

|                   |      | 2.1.3  | Local features: magnitude, orientation and phase                                     | 19 |

|                   | 2.2  | Model  | modifications towards a hardware friendly implementation                             | 21 |

|                   |      | 2.2.1  | Optical flow model modifications for hardware implementation $% \mathcal{A}^{(n)}$ . | 21 |

|                   |      | 2.2.2  | Disparity model modifications for hardware implementation                            | 24 |

|                   |      | 2.2.3  | Local features model modifications for hardware implementation                       | 28 |

|                   | 2.3  | A hier | archical approach                                                                    | 30 |

|                   | 2.4  | Multi- | scale operation vs temporal oversampling approach $\ldots$                           | 32 |

|                   | 2.5  | Conclu | usions                                                                               | 35 |

# CONTENTS

| 3 | Ster                     | reo ano                                                                                                       | d Local Features architecture                                                                                                                 | 37                                                                                                                     |

|---|--------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   | 3.1                      | Abstra                                                                                                        | act                                                                                                                                           | 37                                                                                                                     |

|   | 3.2                      | Introd                                                                                                        | $uction \ldots \ldots$ | 38                                                                                                                     |

|   |                          | 3.2.1                                                                                                         | Algorithmic vs. RTL description                                                                                                               | 39                                                                                                                     |

|   | 3.3                      | Hardw                                                                                                         | vare architecture                                                                                                                             | 40                                                                                                                     |

|   |                          | 3.3.1                                                                                                         | Rectification and image pyramid                                                                                                               | 40                                                                                                                     |

|   |                          | 3.3.2                                                                                                         | Stereo core                                                                                                                                   | 42                                                                                                                     |

|   |                          | 3.3.3                                                                                                         | Multi-scale architecture                                                                                                                      | 43                                                                                                                     |

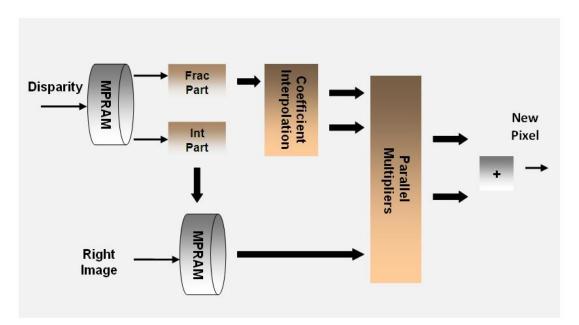

|   |                          | 3.3.4                                                                                                         | 1-D warping for disparity range extension                                                                                                     | 45                                                                                                                     |

|   |                          | 3.3.5                                                                                                         | Implementation and hardware utilization                                                                                                       | 46                                                                                                                     |

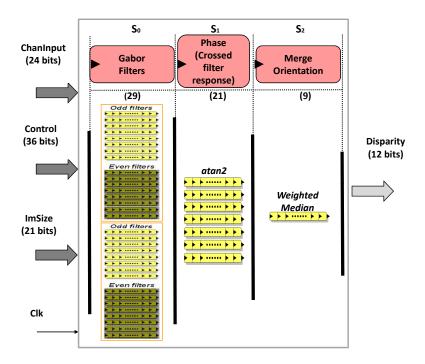

|   |                          | 3.3.6                                                                                                         | Local features integration                                                                                                                    | 47                                                                                                                     |

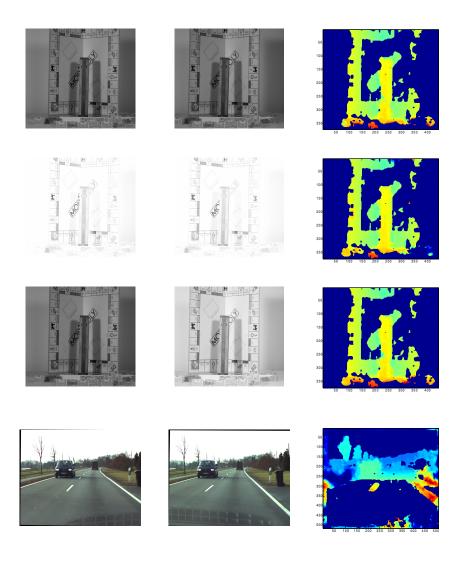

|   | 3.4                      | System                                                                                                        | n results                                                                                                                                     | 48                                                                                                                     |

|   |                          | 3.4.1                                                                                                         | System accuracy                                                                                                                               | 48                                                                                                                     |

|   |                          | 3.4.2                                                                                                         | Performance analysis                                                                                                                          | 49                                                                                                                     |

|   | 3.5                      | Conclu                                                                                                        | usions                                                                                                                                        | 52                                                                                                                     |

|   |                          |                                                                                                               |                                                                                                                                               |                                                                                                                        |

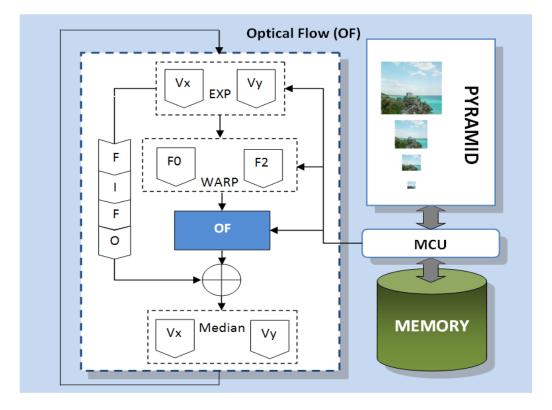

| 4 | Opt                      | ical Fl                                                                                                       | low architecture                                                                                                                              | 55                                                                                                                     |

| 4 | <b>Opt</b><br>4.1        |                                                                                                               | low architecture                                                                                                                              | <b>55</b><br>55                                                                                                        |

| 4 | -                        | Abstra                                                                                                        |                                                                                                                                               |                                                                                                                        |

| 4 | 4.1                      | Abstra<br>Introd                                                                                              | act                                                                                                                                           | 55                                                                                                                     |

| 4 | 4.1<br>4.2               | Abstra<br>Introd<br>Implei                                                                                    | act                                                                                                                                           | 55<br>55                                                                                                               |

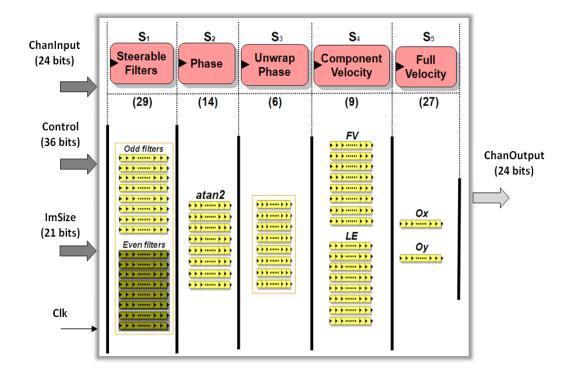

| 4 | 4.1<br>4.2<br>4.3        | Abstra<br>Introd<br>Implei                                                                                    | act                                                                                                                                           | 55<br>55<br>57                                                                                                         |

| 4 | 4.1<br>4.2<br>4.3        | Abstra<br>Introd<br>Implea<br>System                                                                          | act                                                                                                                                           | 55<br>55<br>57<br>57                                                                                                   |

| 4 | 4.1<br>4.2<br>4.3        | Abstra<br>Introd<br>Impler<br>Syster<br>4.4.1<br>4.4.2                                                        | act                                                                                                                                           | 55<br>55<br>57<br>57<br>59                                                                                             |

| 4 | 4.1<br>4.2<br>4.3        | Abstra<br>Introd<br>Impler<br>Syster<br>4.4.1<br>4.4.2                                                        | act                                                                                                                                           | 55<br>55<br>57<br>57<br>59<br>59                                                                                       |

| 4 | 4.1<br>4.2<br>4.3        | Abstra<br>Introd<br>Impler<br>Syster<br>4.4.1<br>4.4.2<br>4.4.3                                               | act                                                                                                                                           | 55<br>55<br>57<br>57<br>59<br>59<br>60                                                                                 |

| 4 | 4.1<br>4.2<br>4.3        | Abstra<br>Introd<br>Impler<br>Syster<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                                      | act                                                                                                                                           | 55<br>57<br>57<br>59<br>59<br>60<br>61                                                                                 |

| 4 | 4.1<br>4.2<br>4.3        | Abstra<br>Introd<br>Impler<br>Syster<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6                    | act                                                                                                                                           | <ol> <li>55</li> <li>55</li> <li>57</li> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> </ol>             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Abstra<br>Introd<br>Implen<br>Systen<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>Copro           | act                                                                                                                                           | <ol> <li>55</li> <li>55</li> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>62</li> </ol>                         |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Abstra<br>Introd<br>Implen<br>Systen<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>Copro<br>Archit | act                                                                                                                                           | <ol> <li>55</li> <li>55</li> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>61</li> <li>62</li> <li>62</li> </ol> |

## CONTENTS

| <b>5</b> | Low  | v level vision engine                                                                                            | 75  |

|----------|------|------------------------------------------------------------------------------------------------------------------|-----|

|          | 5.1  | Abstract                                                                                                         | 75  |

|          | 5.2  | Introduction                                                                                                     | 76  |

|          | 5.3  | Design strategies for a hardware implementation                                                                  | 77  |

|          |      | 5.3.1 Analysis of sharing capabilities                                                                           | 78  |

|          | 5.4  | System architecture exploration                                                                                  | 83  |

|          |      | 5.4.1 Balanced implementation                                                                                    | 84  |

|          |      | 5.4.2 Low cost version $\ldots$ | 88  |

|          |      | 5.4.3 High performance version                                                                                   | 88  |

|          | 5.5  | Case study: Implementation on a XircaV4                                                                          | 89  |

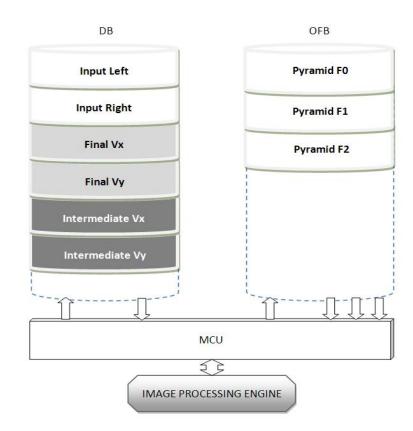

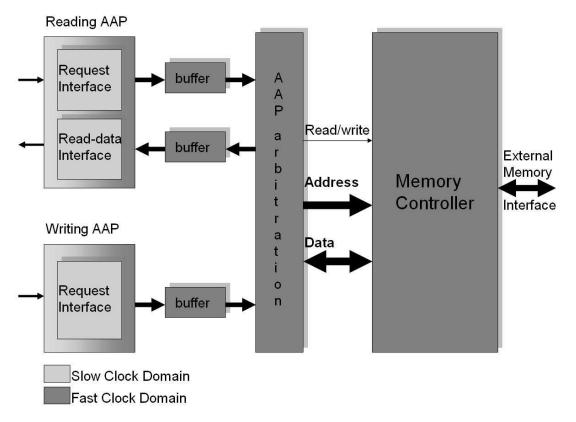

|          |      | 5.5.1 Memory organization and access scheduling                                                                  | 90  |

|          |      | 5.5.2 System performance                                                                                         | 90  |

|          |      | 5.5.3 Results in real and synthetic sequences                                                                    | 92  |

|          |      | 5.5.4 Results discussion and potential applications                                                              | 94  |

|          | 5.6  | Conclusions                                                                                                      | 95  |

| 6        | Disc | cussion                                                                                                          | 97  |

|          | 6.1  | General work motivation                                                                                          | 97  |

|          | 6.2  | Future works                                                                                                     | 98  |

|          | 6.3  | Publication of results                                                                                           | 99  |

|          | 6.4  | General Scientific Framework                                                                                     | 100 |

|          | 6.5  | Main contributions                                                                                               | 100 |

| 7        | Арр  | pendix A 1                                                                                                       | .03 |

|          | 7.1  | Optical Flow and Stereo regularization                                                                           | 103 |

|          | 7.2  | Regularization on Optical Flow                                                                                   | 103 |

|          | 7.3  |                                                                                                                  | 104 |

|          | 7.4  | Hardware implementation                                                                                          | 105 |

|          | 7.5  | Conclusions                                                                                                      | 106 |

| 8        | App  | pendix B 1                                                                                                       | 13  |

|          | 8.1  |                                                                                                                  | 113 |

|          | 8.2  | FPGA board                                                                                                       |     |

|          | 8.3  | Memory Controller Unit                                                                                           |     |

# CONTENTS

| 8.4     | Software interface | 15 |

|---------|--------------------|----|

| 8.5     | Camera set-up      | 17 |

| Bibliog | raphy 1            | 19 |

# List of Figures

| 1.1 | Vision Levels                                                  |

|-----|----------------------------------------------------------------|

| 1.2 | Development Stages                                             |

| 1.3 | Sharing strategy                                               |

| 1.4 | Project framework                                              |

| 2.1 | Optical Flow                                                   |

| 2.2 | Phase robustness                                               |

| 2.3 | Optical flow: warp on phase vs image                           |

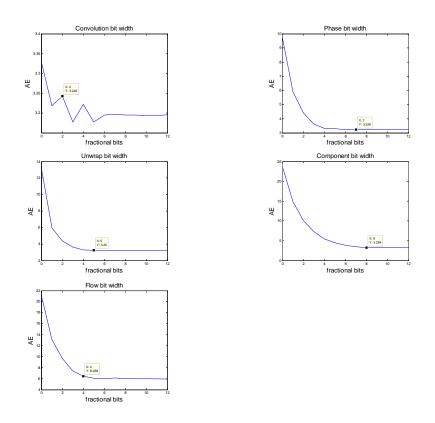

| 2.4 | Optical flow: bit width study 27                               |

| 2.5 | Stereo: warp on phase vs image                                 |

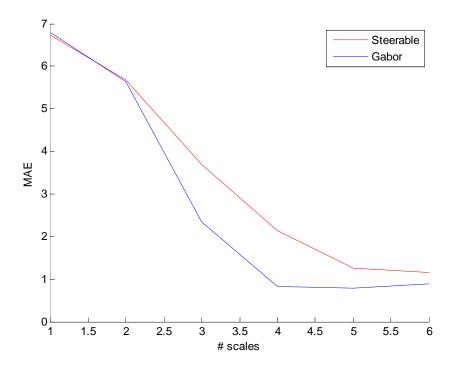

| 2.6 | Stereo: iteration Steerable vs Gabor                           |

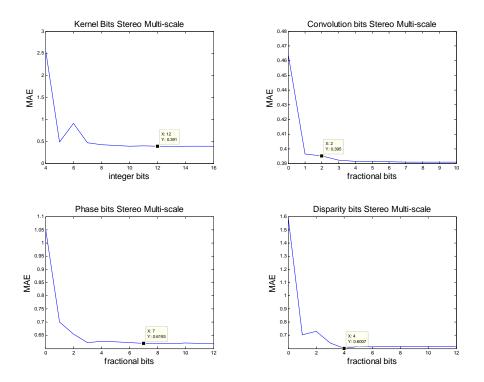

| 2.7 | Stereo: bit width study 30                                     |

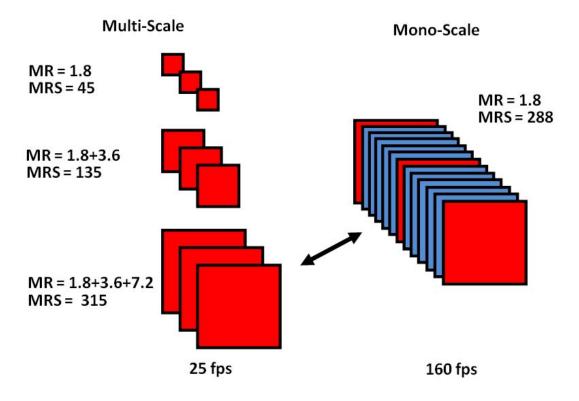

| 2.8 | Motion Range for multi-scale methods versus mono-scale ones 33 |

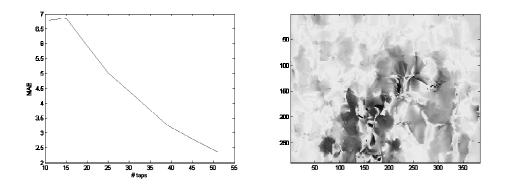

| 2.9 | MAE variation for different filter sizes                       |

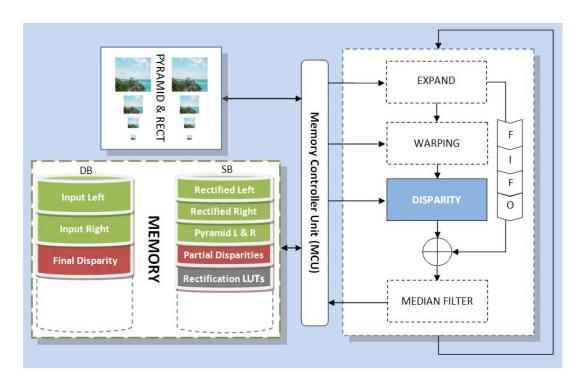

| 3.1 | Multi-scale architecture of the complete stereo system         |

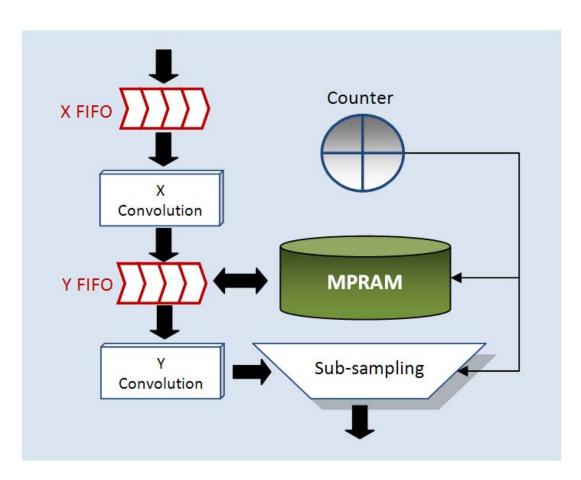

| 3.2 | Circuit architecture for the image reduction                   |

| 3.3 | Pipeline stages for a mono-scale system                        |

| 3.4 | Warping architecture for the stereo case                       |

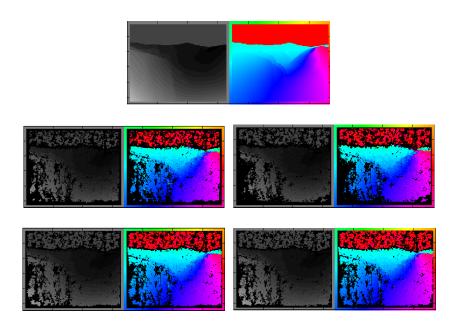

| 3.5 | Qualitative results of the stereo system                       |

| 4.1 | Optical flow system architecture                               |

| 4.2 | Optical flow processing core                                   |

| 4.3 | Screen capture of the optical flow application                 |

| 4.4 | Memory mapping for optical flow                                |

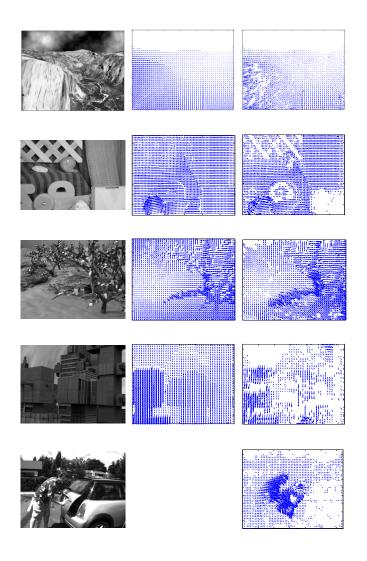

| 4.5 | Qualitative results for different Middlebury sequences         |

# LIST OF FIGURES

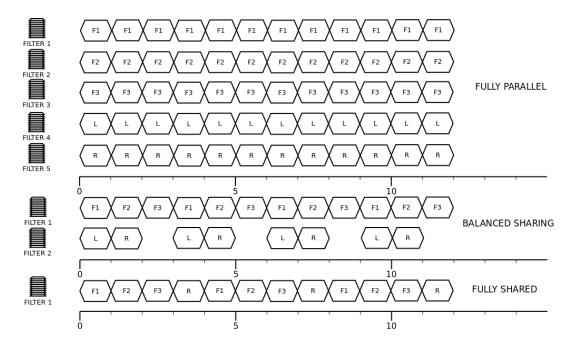

| 5.1 | Different sharing strategies are shown with a timing diagram. A fully        |     |

|-----|------------------------------------------------------------------------------|-----|

|     | parallel implementation provides one data per clock cycle throughput         |     |

|     | while the slower sequential approach achieves only one pixel in four         |     |

|     | clock cycles. The fully parallel architecture works for 3 temporal im-       |     |

|     | ages of optical flow and 2 images (left and right) for the stereo case. The  |     |

|     | local features could use the input from the middle frame of the flow and     |     |

|     | therefore no additional filter bank is required                              | 81  |

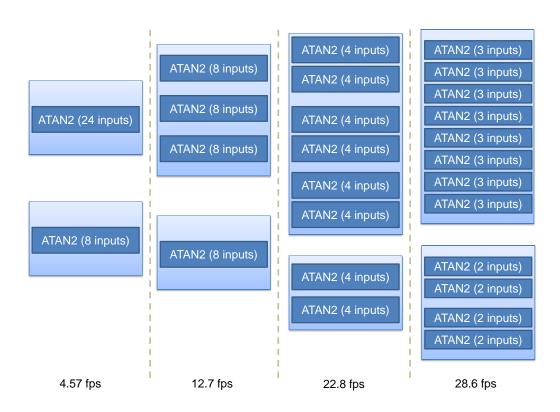

| 5.2 | Different sharing phase solutions: atan2 cores are the sames of stage 2      |     |

|     | in Fig. 3.3 for stereo and in Fig. 4.2 for optical flow. Frame rates for     |     |

|     | a 512x512 resolution are reported. Note that without sharing strategies      |     |

|     | the system uses 32 modules and achieves 57 fps                               | 83  |

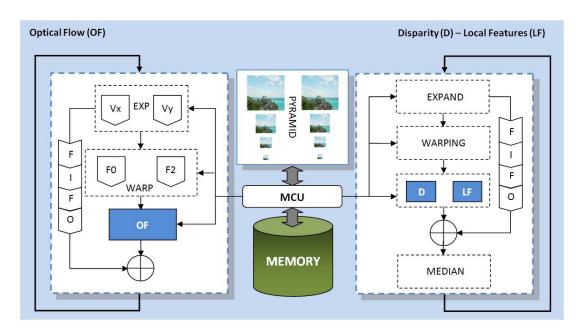

| 5.3 | Whole system architecture.                                                   | 86  |

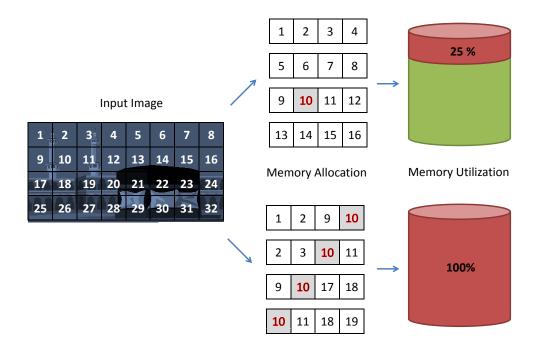

| 5.4 | Warping improvement. For each pixel of the input image we store in           |     |

|     | external memory all the values of its $2x2$ neighborhood. In the traditional |     |

|     | approach (upper part) consecutive pixels are stored. In the improved         |     |

|     | warping (bottom) the same pixel is repeated 4 times                          | 89  |

| 5.5 | Memory mapping for a XircaV4 platform. Note that an MCU is manda-            |     |

|     | tory for a parallel access to all this data                                  | 91  |

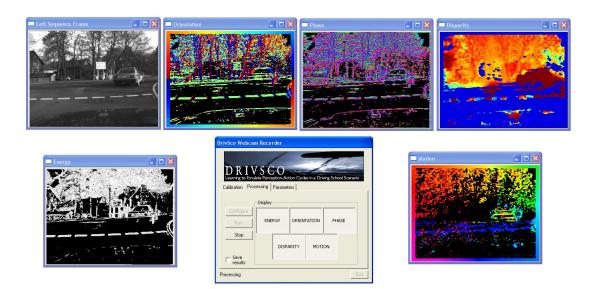

| 5.6 | Screen shot of software interface while running a full processing in a driv- |     |

|     | ing scenario. First row, left to right, input left image, local orientation, |     |

|     | phase information and stereo information. Second row, local energy, user     |     |

|     | interface and optical flow direction according to the color code at the im-  |     |

|     | age frame. Note that all these features are running simultaneously on        |     |

|     | the same chip.                                                               | 93  |

| 7.1 | Optical flow regularization: yosemite.                                       | 105 |

| 7.2 | Optical flow regularization: urban2.                                         | 106 |

| 7.3 | Optical flow regularization: real sequence                                   | 108 |

| 7.4 | Stereo regularization: Tsukuba                                               | 109 |

| 7.5 | Stereo regularization: Venus                                                 | 110 |

| 7.6 | Stereo regularization: real sequence.                                        | 111 |

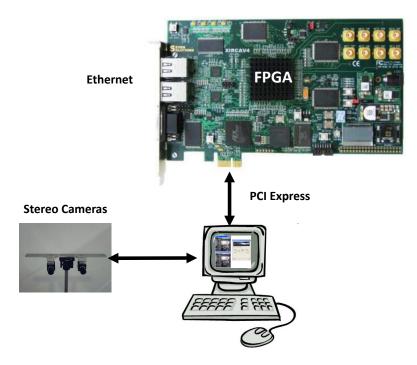

| 8.1 | Co-processing platform.                                                      | 114 |

| 8.2 | MCU interface scheme                                                         | 116 |

# List of Tables

| 2.1 | Comparison of warping techniques in optical flow (phase vs image) for         |    |

|-----|-------------------------------------------------------------------------------|----|

|     | "Yosemite" sequence                                                           | 22 |

| 2.2 | Accuracy loss due to the reduction of frames in the temporal window.          |    |

|     | The AE is expressed in degrees. Note that the density is also changed         | 24 |

| 2.3 | Percentages of accuracy loss and final model error for different model        |    |

|     | simplifications using the single scale approach and "Yosemite" synthetic      |    |

|     | sequence [1]. The % Lost is computed taking as reference the error ob-        |    |

|     | tained with the warping on images algorithm. AE stands for Angular            |    |

|     | Error as defined in [1] and is presented in the last column. The regular-     |    |

|     | ization includes a cascade of two 3x3 median filters at each scale output     |    |

|     | (see Appendix A).                                                             | 25 |

| 2.4 | Percentages of accuracy loss and final model error for different model        |    |

|     | simplifications using the multi scale approach with warping on images         |    |

|     | and the Yosemite synthetic sequence [1]                                       | 25 |

| 2.5 | Bit-depths of the input of each processing stage as described in Section      |    |

|     | 2.1.1. The first values represent the signed integer part and the second      |    |

|     | values, the fractional one. Output of S5 has [8 4] that is the representa-    |    |

|     | tion for the final optical flow values.                                       | 26 |

| 2.6 | Comparison of warping techniques in stereo (phase vs image) for "Tsukuba"     | _0 |

| 2.0 | sequence.                                                                     | 26 |

|     |                                                                               | 20 |

| 3.1 | HW resources for different system parts (functional blocks) in an $xcv4fx100$ |    |

|     | device                                                                        | 46 |

| 3.2 | Mean Absolute Error (MAE), standard deviation, density, and percent-          |    |

|     | age of error major than 1 for different image pairs                           | 49 |

# LIST OF TABLES

| 3.3 | Power consumption for stereo circuits in a Virtex 4 xc4vfx100: estimated with Xpower tool.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4 | Comparison with other approaches described in the literature. We indicate the throughput in MegaPixels per Second (MPPS) and the Point $\times$ Disparity per Second (PDS=MPPS X D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52 |

| 4.1 | Hardware use for a Virtex 4 xc4vfx100. We describe the recourses used<br>for different circuit parts. Here we compare three different architectures:<br>the first is the original implementation, the second is an alternative with<br>a sharing strategy and the third is a high-accuracy version with Ga-<br>bor filters. The table is divided into four different parts: total system<br>resources, hierarchical blocks and interface, mono-scale parts and total                                                                                                                                                                                                                   | GE |

| 4.2 | mono-scale cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65 |

| 7.2 | estimated with Xpower tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66 |

| 4.3 | Frames per second at different image sizes and number of scales. In<br>a mono-scale approach the system can process up to 186.26 fps using<br>images of 512x512, but this approach is limited in range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67 |

| 4.4 | Angular errors for different Middlebury sequences [2]. We use four scales                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00 |

| 4.5 | for all sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68 |

| 4.0 | mono-scale engine achieves 24.8 MPPS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69 |

| 5.1 | Computing resources and accuracy for different kinds of filter banks:<br>Steerable stands for the second order Gaussian derivatives steerable fil-<br>ters and Gabor for the Gabor filters. Hardware utilization is estimated<br>for a Xilinx Virtex xc4vfx100 [3] with the Agilent DK5 tools [4]. Ac-<br>curacy columns reports the optical flow Angular Error (AE) for the<br>"Yosemite" sequence and the stereo Mean Absolute Error (MAE) for the<br>"Tsukuba" sequence. In brackets we indicate the density. Hardware uti-<br>lization is referred to only one bank, depending on the algorithm (stereo<br>or optical flow) this will be approximately multiplied by the number of |    |

|     | input frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79 |

| 5.2 | Hardware utilization for different number of steerable shared filters. Re- |

|-----|----------------------------------------------------------------------------|

|     | sults are provided by DK synthesis tool for 4 orientations filters $82$    |

| 5.3 | Comparison for different platform implementations. Frame rates are for     |

|     | 512x512 resolutions and power consumption is estimated by Xpower tool.     |

|     | Errors are reported for "Tsukuba" and "Yosemite" sequences (further        |

|     | validations are in Chapters 3 and 4). Prices are taken from [5] 90         |

| 5.4 | Frames per second at different image size and number of scales (results    |

|     | experimentally measured with the balanced system running). Clock set       |

|     | to 42 MHz. A mono-scale processing will be faster but is not accurate      |

|     | for large/fast movements and significant disparities                       |

| 7.1 | Errors for the Yosemite sequence. HW Matlab model                          |

| 7.2 | Errors for the Urban2 sequence. HW Matlab model                            |

| 7.3 | Errors for the Tsukuba sequence. HW model                                  |

| 7.4 | Errors for the Venus sequence. HW model with 5 scales 107                  |

| 7.5 | Hardware utilization for two different implementations of a $3x3$ median   |

|     | filter. The design run in a Xilinx Virtex4 xc4vfx60. The edif netlist      |

|     | generated by the DK Suite 5                                                |

# 1

# Introduction

Historia magistra vitae est. Exploring the ancient theories, is possible to find in the old Greek philosophy some rudimental definitions or concepts of human vision interpretation. Aristotle in his book "On Sense and the Sensible" affirms that "Of the two last mentioned, seeing, regarded as a supply for the primary wants of life, and in its direct effects, is the superior sense; ... The faculty of seeing, thanks to the fact that all bodies are coloured, brings tidings of multitudes of distinctive qualities of all sorts; whence it is through this sense especially that we perceive the common sensibles, viz. figure, magnitude, motion, number ...". After these first preliminary steps, a lot of relevant philosophers and scientists have contributed to build many theories for the human vision system. This great and long history demonstrates how much important is for our life vision understanding. In day life, for example in a sport environment, all kind of trainer agrees with colleagues thinking that a good player has to be rapid in the vision of the game and in the interpretation of the play before the adversary. If we move to a more dramatic environment such as a driving scenario, a person driving in bad environmental or physical conditions need a very fast reaction to a sudden presence of an object in his way. The reaction will be faster if the processing capabilities need less time to understand the danger. Both cases depend strongly from the velocity of vision system. In a hunting scenario, also vision is critical and the major advantage resource of many natural hunters (such as eagles). With three simple citations we remark importance of vision, velocity and size. In this work we want to collect these three challenges in a single one: a fast and small vision engine. The realization of this ambitious task will take advantage of recent developments in technology and

#### 1. INTRODUCTION

research of these last years and it is possible only with an accurate and intelligent use of previous contributions. Despite the great advance of computational processing in general purpose machines we focus our attention on small embedded systems that can afford at the same time our three aims (low power consumption, high performance, and physical size). As we can see from everyday experience, our life is more and more rounded of small electronic devices powered with powerful and fast chips. In this work, we contribute to this research field adopting Field Programmable Gate Array (FPGA) devices and defining novel architectures of image processing.

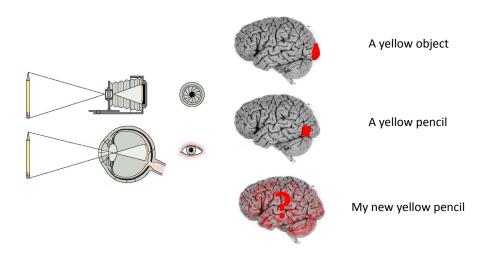

### 1.1 Vision Framework

One of most complex and perfect example of vision systems is the human sight. As reported by Kandel in his book [6] "Studies of artificial intelligence and of pattern recognition by computers have shown that the brain recognizes form, motion, depth, and color using strategies that no computer can achieve. Simply to look out into the world and recognize a face or enjoy a landscape requires an immense computational achievement more difficult than that required for solving logic problems or playing chess." Beginning with the firsts neural and biological studies, scientists have been attracted from this wonderful system that is the human "machine". Observing and understanding the nature mechanisms, researchers try to reproduce its functioning. Human vision system is not an exception. Following this philosophy has been born photography and video cameras and now a lot of vision algorithms are inspired by nature. At the moment the human visual system is not completely understood. We know that the complex process of vision and scene interpretation can be divided in different level of processing. As displayed in Fig. 1.1 and taking inspiration from neuroscience, a vision system can be divided into low-level, middle-level and high-level [7]. With respect with other processing parts of the brain we know that visual cortex occupy a significant area. For example in the macaque neocortex the 50% is dedicated to process the visual information while only the 11% is somatosensory cortex and 3% is auditory cortex. Furthermore as stated in [6] we know that among the different parts of visual cortex the biggest ones are the V1 and V2 (low level vision) that occupy over  $1100 \text{ mm}^2$ , while one of the smallest is the MT (middle temporal) that occupies only  $55 \text{ mm}^2$ . In an analogical way a visual system in computer vision requires a larger computational effort for the low-level part

with respect to the middle or high level. Despite a quite detailed information about lowlevel and middle-level vision in the human vision, we have not much information about high-level. The well-known binding problem is not clear yet and opens a complicate relationship with neural studies and psychological ones. In computer vision, researchers disagree about a common canonized division of roles among vision levels. [7] explains that if a representation is based on arrays of numerical data that correspond directly to image data (pixel-wise operations), it is low-level vision. Representations based on symbolic descriptions of extracted image events, or view-specific symbolic instantiations of stored models and knowledge are intermediate level [7, 8, 9]. Representations that are view or scene independent are high level. A high-level representation thus characterizes general models and knowledge, as well as view independent 3-D models and knowledge of the current environment.

Thus low-level vision represents the basis on which other levels build a scene understanding. Such complex vision systems are currently fascinating researchers and advances in technology benefits great improvements in the computer vision. Currently vision systems are of extreme importance in many application fields and our world is rounded of cameras and displays. Industrial processes use robotic platform eyes equipped to control chain productions. All public buildings get a vision system for security purposes and surveillance. Automotive industry is exploring the possibility of a new concept of sensor based on smart cameras that advice the driver of unexpected dangers [10]. Many other applications, as military [11] or medical, benefit of computer and machine vision [12].

#### 1.2 Vision processing platforms: State of the Art

Currently to afford the implementation of a vision system, different technologies are available. For research purposes and algorithm development, the faster and practical solution for a method validation is the high level programming in conventional general purpose processors. The processing power of these machines has grown up very quickly rising the Moore's law and the presence of many programming languages offers to the researcher a lot of possibilities for a rapid implementation. For instance, a very common platform for validation in engineering is the MATLAB environment. Imaging tools, information representation libraries for this language and the big efficiency with

#### 1. INTRODUCTION

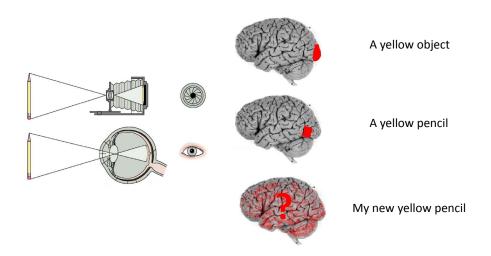

**Figure 1.1: Vision Levels** - Division of different vision levels (figure adapted from [6]). At low level (V1 and V2 regions of the human vision system) we process the whole image extracting cues: major effort. At middle level (V4, inferior temporal cortex) we associate a determinate object. At high level (binding problem) we recognize a specific object accessing to information external to the scene.

matrix operations allow a very short time of implementation and validation. Due to the time of realization this step can be considered the first one to address a faster implementation of a model.

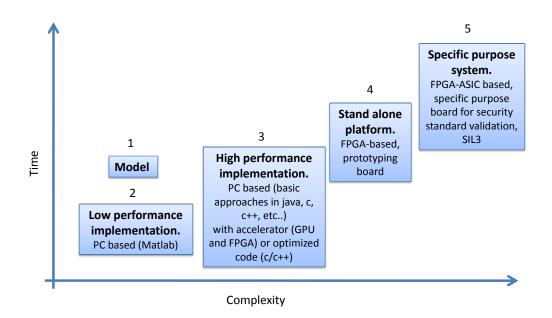

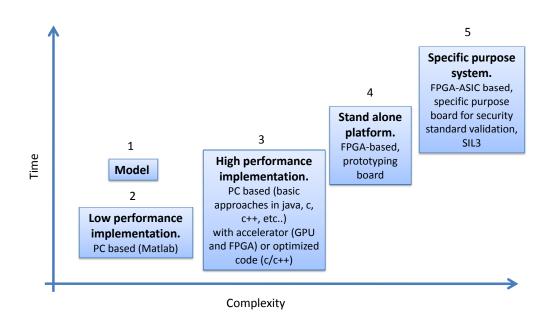

To speed up the code and going on to potential industrial products different steps are required (Fig.1.2). Depending on our purposes we can stop on every one of these steps. If we have no constraint in size and power we can stop the implementation to a PC based code but we can speed up the low performance implementation with a more optimized code like in [13] or adopt specific hardware accelerators such as Graphic Processing Units (GPU). In the first case the optimization adopted can follow different strategies: from a simple compiler optimization to a low level code (assembler). The second one is generally a C-like implementation with specific environments such

**Figure 1.2: Development Stages** - Different development steps for a vision system. Process begins with a simple high level language until the synthesis on a VLSI industrial product. Steps are situated in a complexity vs. time plot.

as CUDA [14] that vary depending from the hardware platform. Currently due to the game industry the technology of GPU has grown up enormously and this platforms use the best solutions in parallelism and memory accesses. A more optimized work in terms of size and power consumption is a prototyping board implementation, for example on an FPGA based platform. This approach achieves a very high level of parallelism in operations with a reduced clock frequency: about two orders of magnitude less than a conventional processor or a GPU device. It benefits the power consumption and the use in portable applications. The last and more complex step for an optimized implementation is the design of a specific purpose system. Starting from the prototyping board previously validated is possible to produce a VLSI chip for industrial purposes that can be adopted for specific portable applications and can abates costs with a large production. Depending on our target application we could stop at different design stages or continue towards more complex steps. For example if we are interested in

#### 1. INTRODUCTION

mobile robotics for research applications, a specific hardware platform provided with DSPs or FPGAs is the target choice and we can eliminate the optimization of the software code for commodity processor or the implementation on GPU that do not contribute to final work. Nevertheless, basic implementation using a simple language such as MATLAB, Octave or equivalent are appropriate. The last step (much more oriented to commercial purposes) needs an extra time for design and validation and involves other issues as system certification according to the target application and its respective Security Integrity Level (SIL). This last stage is a necessity of industry and generally is not addressed by most of the research fields. Currently, the literature presents different approaches for the diverse implementation steps presented. The first one (model in software) and the second one (optimized code and/or coprocessors boards) are the most active fields.

High performance has been achieved in accuracy for the many low level applications. Some contributions as [15] and [1] help us to understand the state of the art in the stereo and motion implementation approaches. Researchers contribute to the literature with the generation of diverse sets of images benchmark [2]. This valorous work allows an important validation for algorithms but, though we have reached a high level of accuracy for these synthetic benchmarks, new implementations are voted to an exasperate attempt to improve the actual level of accuracy with these benchmarks and do not address many of the practical aspects of the real world (real-time, illumination changes, unconstrained environments, etc). This problem is due to the evident difficulty of quantitative validation of real sequences. Current image correspondence techniques are mainly divided into two categories: local approaches and global approaches. Local (window-based) algorithms, where computation at a given point depends only on pixel values within a local spatial window, usually make smoothness assumptions for aggregating support implicitly. In order to increase the accuracy of estimations, particularly along depth borders, state-of-the-art algorithms deploy a variable support to compute the local matching cost rather than using, as in the traditional approaches, a fixed squared window. Conversely, most global methods attempt to minimize an energy function computed on the whole image area by employing minimization strategies such as variational techniques, Markov Random Field model, Graph Cuts (GC) approaches, Belief Propagation (BP), etc. [15, 16, 17]. Since this task turns out to be an NP-hard problem, the estimation is approximated by efficient strategies [15, 16, 17]. Moving towards an optimized implementation or a hardware specific architecture (right part of plot in Fig. 1.2) fewer contributions are presented in the literature. This means that the complexity of the implementation grows up significantly. We can find diverse GPU implementation of previous studied approaches but only some simple algorithms have been implemented in FPGA or DSPs processors. The reason for this actual tendency is the easier programming environment and the shorter "time to market" for commodity processors compared to DSP or FPGA based solutions. The evident problem of the utilization of standard PC based solutions is the power consumption and the considerable size unviable for many portable applications. For the other part an FPGA and DSPs implementation can afford a portable application and evolve into an industrial product. The comparison between DSPs and FPGAs shows that DSPs are better suited for low power applications whilst FPGAs are better option if the performance requirements are very high [18] or we plan to address the development of ASIC solutions. Works such as [19] and [20] represent very important contributions to the FPGA based vision on chip but at the same time lack of generic applicability. The main problems for existing FPGA approaches are the processing speed and the adaptation to large changes in the scene as in movements or in camera variations. Multi-scale approaches that can solve some of these problems present a high computational cost and are not hardware friendly. For this reason they are rarely adopted for hardware implementations. If we move to the last step of Fig. 1.2 we can find only few works as [21] that represent a very appreciable contribution for a specific purpose vision system on-chip.

### **1.3** Our contribution

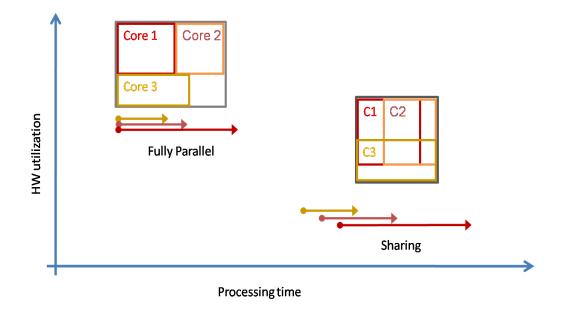

In this work we start from existing vision models. We study and validate these models adapting algorithms to a hardware implementation and analyzing error due to the utilization of fixed point arithmetic (quantization degradation). Previous works of the literature as [19] and [20] lead directly to the step 4 of Fig. 1.2 without passing through the optimized code or the GPU implementation. We introduce for the first time vision architectures of a very high complexity and design methodologies. Range problem of existing approaches are solved with a multi-scale implementation. Hardware unfriendly operations such as warping are included in architectures with up to 4 clock domains. We introduce and optimize fine sharing strategies and study the performance

#### 1. INTRODUCTION

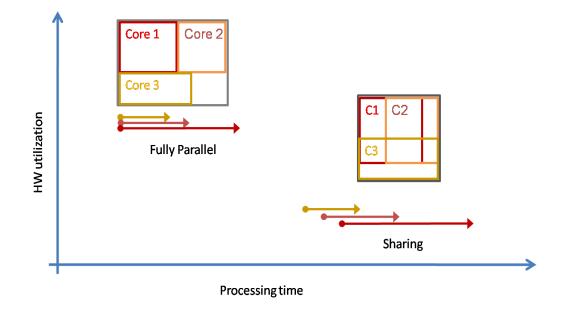

vs. hardware utilization trade-off. The general idea is to obtain a balanced throughput reduction and a parallel processing unit sharing as it is displayed in Fig. 1.3. Diverse chip implementations have been explored to validate the modularity and scalability of the architecture.

**Figure 1.3: Sharing strategy** - A fully parallel implementation (left) vs. a shared approach (right). With sharing we lose in throughput but save hardware recourse.

We study the adaptation of the design to the chip size and system requirements. Our minimum requirement is a real-time processing (25 frames per second) for an image resolution of 512x512 pixels. This work contributes to the advances in computer vision, especially in machine vision. We try to compare our approach with the state of the art providing quantitative results. Well-known benchmarks [2] with ground truth are used; furthermore we validate qualitatively the stability of the algorithm with real sequences exploring possible industrial applications as automotive.

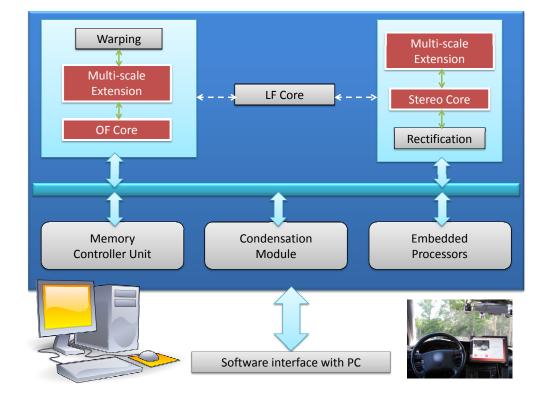

## 1.4 Project Framework

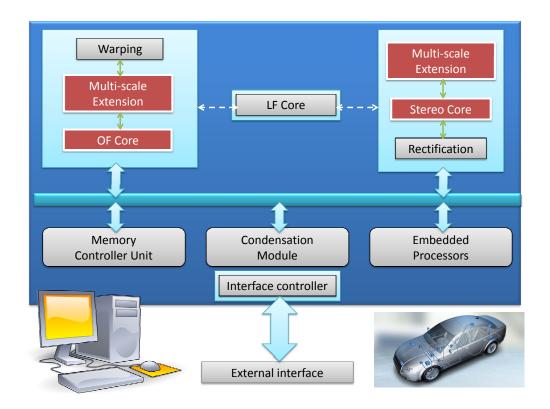

The low level vision system has been developed within the European project "Learning to emulate Perception-Action Cycles in a driving school scenario" (DRIVSCO) [22] in collaboration with six different universities. The goal of DRIVSCO is to devise, test and implement a strategy of how to combine adaptive learning mechanisms with conventional control, starting with a fully operational human-machine interfaced control system and arriving at a strongly improved, largely autonomous system after learning, that will act in a proactive way using different predictive mechanisms. The research group at the University of Granada was involved in the implementation of the processing engine on chip. Inside our group, five different persons contributed to this work. The final implementation includes the development of a co-processing system with a FPGA-based platform. As indicated in Fig. 1.4 the complete work is composed by:

- External interface controller for GPIO, PCI-Express, Ethernet (for communication with PC, vehicle, robot, etc..)

- Memory Controller Unit

- Processing cores (optical flow, stereo and local features)

- Condensation modules

- Embedded processors (particulary suited for middle-high level vision algorithms development)

Our work, presented in this thesis, focuses mainly in the vision processing cores and the multi-scale architecture. The work in group obviously means a crossed collaboration with other members especially in testing tasks and validation of algorithms and models.

## 1.5 Outline

We start this work with a brief description of the harmonic representation used by our vision algorithm and a hardware friendly adaptation of it. Technological constraints and real-time requirements compel us to specific algorithm simplifications. On chapter 2 we study these changes for each single vision modality that we estimate: stereo, motion and local features (magnitude, orientation and phase). Following chapters describe every

#### 1. INTRODUCTION

**Figure 1.4: Project framework.** - Block diagram of the DRIVSCO system developed by the Granada University group. Red parts have been addressed in this work. The system may be used as co-processor for a PC or as stand-alone platform (for example in a car).

single modality implementation and its multi-scale architecture. Chapter 3 presents a stereo architecture and chapter 4 an optical flow system. These two architecture architectures themselves represent a very important innovation for the state of the art. Furthermore another important step towards a vision system on chip is made in chapter 5 with the description of a large low level vision engine that includes all previous modalities in the same chip. A novel architecture and its design strategies are presented in this section. Further vision primitives can be easily incorporated in such system.

# Preliminary study towards a Hardware implementation

In this chapter we present a brief description of the original phase based algorithms used for our system development, ranking them with respect to other state of the art approaches. We remark here the stability of the phase information and compare it with other approaches. The original model complexity compels us to a specific hardware adaptation. This part aims to examine each of these hardware motivated modifications and how they affect the error. For this study we use a software simulation and leave the hardware evaluation for the following chapters. We repeat the study for every one of the single vision modalities that we have designed: disparity, optical flow and local features (magnitude, orientation and phase).

## 2.1 Optical flow and stereo computational models review

In order to address the initial goal of a high quality vision system, the preliminary stage is a proper study of the existent approaches and their possible adaptation for a hardware implementation. The method we are looking for has to possess a good trade-off between performance and computational cost. For example linear operation and well defined access to memory are hardware friendly operations. At the same time the algorithm has to provide an integrated framework for different vision modalities extracted based on the same features. In general optical flow methods can deal with a disparity computation with just some integration of epipolar constraint and a few modifications. Our goal is to find general methods with high potential sharing capabilities. Currently, exploring optical flow literature we can catalogue existing approaches as explained in [23] and add some novel techniques:

- Differential methods

- Local

- Global (typically variational approaches)

- Surface models

- Contour models

- Multi-constraint models

- Hierarchical approaches

- Frequency-based methods

- Orientation selective filtering

- Phase-based filtering

- Hierarchical approaches

- Correlation based methods

- Correlation-based matching

- Hierarchical approaches

- Multiple motion methods

- Line processes

- Mixed velocity distribution

- Parametric models

- Temporal refinements methods

Among existing methods the best solutions in terms of accuracy for single modality vision are global approaches such as the variational ones. Variational methods as [24] are hybrid (local-global) approaches and achieve very high accuracy. But due to its iterative nature (minimization of energy functional) they are difficult to implement in real-time using reconfigurable hardware (typically slow for iterations due to the low clock frequency). Nevertheless there are some implementations using commodity processor and sophisticated minimization methods [24] or GPU based implementations [25] that are able to achieve the real-time processing. Unfortunately, for embedded applications, these techniques are not affordable. Frequency based algorithms follow variational approaches in accuracy. They present a robust response to unconstrained and unstable scenarios. A software comparative between different approaches can help us to make a choice. Discarded the variational methods we can focus on the other ones. By exploiting, on a local basis the spectral information content of the image signal (amplitude and phase), it is possible to derive perceptual entities, useful to gain interpretative elements of the observed scene, such as edges/contours, motion, and binocular disparity. Although most of the classical algorithms available in the literature rely upon the amplitude information, in the last two decades alternative techniques based on phase measures have been asserted themselves. The importance of global (Fourier) phase has been first demonstrated with respect to image coding and representation, by comparing modulus-only and phase-only image reconstructions [26], [27], and has been confirmed also in case of the local phase spectrum [28]. On that ground, the popularity of the phase information, as a robust feature descriptor, has risen in relation with the numerous important properties that have been reported and analyzed [29, 30, 31, 32], such as: (1) the capability of measuring changes much smaller than the spatial quantization (giving sub-pixel accuracy without a sub-pixel representation of the image, due to its continuous nature); (2) the stability with respect to small geometric deformations of the input; and (3) - perhaps the most desirable property - the invariance with both mean luminance and contrast (e.g., with respect to smooth shading and lighting variations), which makes phase, in principle, robust against typical variations in image formation. For these reasons, during the recent past, the phase from local bandpass filtering has gained increasing interest in the Computer Vision community and has led to the development of a wide number of phase-based feature detection algorithms in different application domains [19, 29, 33, 34, 35]. The harmonic representation will be the base for a systematic phase-based interpretation of vision processing, by defining perceptual features on measures of phase properties. From this perspective, edge and contour information can come from phase-congruency, motion information can be derived from the phase-constancy assumption, while matching operations, such as those

# 2. PRELIMINARY STUDY TOWARDS A HARDWARE IMPLEMENTATION

used for disparity estimation, can be reduced to phase-difference measures. In order to motivate quantitatively the choice of a phase-based method we take for example the optical flow. Optical flow is the pattern of motion that results from the projection of object and induced scene motion on the retina of a, possibly moving, observer. It is represented by a vector field that contains a 2D velocity vector for every spatial location. The optical flow can be thought as the instantaneous positional velocity field (Gordon 1965) which associates with each element on the retina the instantaneous velocity of that element. Horn and Schunck [36] defined optical flow as follows: "The optical flow is a velocity field in the image which transforms one image into the next image in a sequence. As such it is not uniquely determined. The motion field, on the other hand, is a purely geometric concept, without any ambiguity it is the projection into the image of three-dimensional motion vectors." As described before, a lot of mathematical algorithms [29, 37, 38] try to find the velocity vectors that transform a frame of a sequence into the following one. One of the motivations for implementing a phase-based approach is its robustness against illumination changes that appears on real systems in unconstrained scenarios.

In order to demonstrate robustness of the phase-based method we have processed sequences with artificial illumination changes using several well known algorithms: Lukas and Kanade (local), Horn and Schunk (global) and a high accuracy model (that can be seen as an improved version of the Horn and Schunk one) that is based on the work of Brox et al. [39] and that we shall call as the variational method. We use a synthetic diverging sequence generated with a previous assigned ground truth as shown in Fig. 2.1. After the generation of the input sequence, we simulate the different local luminance. For each variation we measure the Angular Error (AE), the standard deviation (STD), and the density for valid values as described in [2]. In 2.2, we report the behavior of the system for the different variations (image artifacts). The variational method is based on [39] where, however, the data terms are based on the gradient and  $L^2$  norm of the gradient thus making the method more robust against illumination changes. Since the LK (Lukas and Kanade) and the HS (Horn and Schunk) methods are based on intensity levels we expect that they will not be robust with respect to illumination changes whereas the variational method should yield more stable results. Another version of this method based on the phase input achieves a further improvement. This confirms

our hypothesis on phase robustness applied to a different approach with a significantly higher computational complexity.

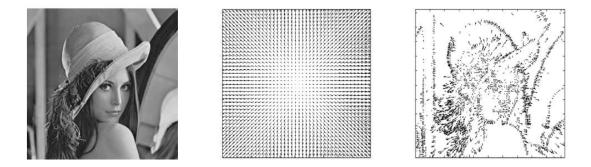

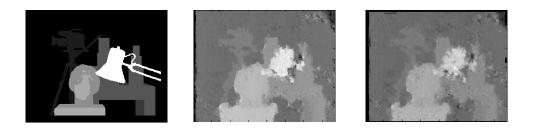

Figure 2.1: Optical Flow - Central frame of the input sequence (on the left), its correspondent ground truth (on the middle), and the optical flow computed in standard (original) conditions.

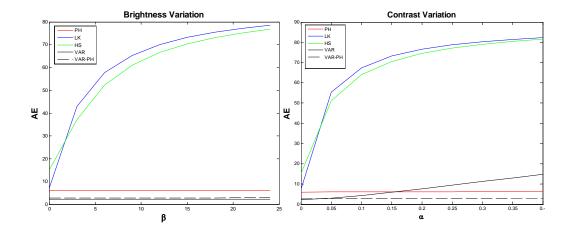

As we can see in Fig. 2.2, the phase-based algorithm is robust to variations compared with other methods. Obviously the variational method achieves a better accuracy in lack of variations but as shown in the plots its final error is worst than ours. Although a phase input to the variational method (dashed line in Fig. 2.2) gives more stability to this approach, it is worthwhile to remind that such large computational effort is not suitable for FPGA implementations. Note that in the case of brightness variation (additive noise) both approaches of variational method behave in a stable way: this is due to the nature of gradient, in this case the derivative is not affected by an additive constant. The algorithm has been applied with the same parameters and changing the input images. For contrast variation, we multiply each image by a 1- $\alpha$  where  $\alpha$ is a variable in the interval [0:0.4]. For brightness variation, we add a global constant to the pixels of the image. We use a variable  $\beta$  in the interval [0:25] considering an image gray color map from [0:255]. Taking into account that we have three temporal images, we applied a positive variation to the future frame, a negative variation to the previous one and no variations to the middle frame. Interestingly enough, for both the contrast and the brightness variations, the AE increases with the variation in the case of the LK method and the HS but it seems to maintain its base value for the phasebased approach. It confirms the hypothesis that phase information is very robust and, on the other hand, shows the well known problem of gradient models to illumination variations. Note that for all tests, we have a density of 98% valid values.

Figure 2.2: Phase robustness - System behavior for different camera variations (image artifacts). On the left side, a variation in contrast; on the right, a variation in brightness. On the y axis the AE value is reported; on the x axis,  $\alpha$  is reported for the contrast while  $\beta$  is shown for the brightness.

#### 2.1.1 Reference optical flow computation model

We have focused on the phased-based computing model proposed in Sabatini et al. [40] and [41] which is a multi-scale extension of the Gautama and Van Hulle original approach [33]. The advantage of phase-based approaches has been pointed out by different authors because their robustness against luminance variations and cameras imbalance problems. Furthermore, these phase-based approaches lead to a better behavior against affine transformations (for instance due to different cameras perspectives) [29, 30]. Spatially localized phase measurements can be obtained by filtering operations with quadrature-pair filters. It is possible to use the original Gabor filters or some Gabor-like approach as band pass steerable filters based on Gaussian derivatives as described in [42]. The filter response, obtained by convolving the images with the oriented quadrature filters is used as input to the phase-based algorithm. For every spatial orientation  $\theta$  and location x, the temporal phase gradient in time t, noted as  $\phi_{\theta}(x, t)$ , is computed through a linear least-squares t to the model as indicated in (2.1).

$$\phi_{\theta}(\mathbf{x}, t) \approx c_{\theta}(\mathbf{x}) + \phi_{t,\theta}(\mathbf{x})t \tag{2.1}$$

A simple unwrapping technique is used to cope with the periodicity of the phase. Next, for each orientation  $\theta$  a component velocity is computed directly from  $\phi_{t,\theta}(x)$ :

$$v_{c,\theta}(\mathbf{x}) = \frac{-\phi_{t,\theta}(\mathbf{x})}{2\pi (f_{x,\theta}^2 + f_{y,\theta}^2)} (f_{x,\theta}, f_{y,\theta})$$

(2.2)

Where  $f_{x}$ , and  $f_{y}$ , are the spatial frequency values at  $\theta$  orientation. The f components are not explicitly computed assuming phase linearity that allows translating the sum of squared frequency values to a constant characteristic which is the peak frequency of the filter used. Note that the spatial phase gradient is substituted by the radial frequency vector. The reliability of each component velocity at each orientation  $\theta$  is measured by the Mean Squared Error (MSE) of (2.3), where n is the number of frames and  $\Delta \phi_{\theta}(\mathbf{x}, t) = (c_{\theta}(\mathbf{x}) + \phi_{t,\theta}(\mathbf{x})t) - \phi_{\theta}(\mathbf{x}, t)$ .

$$MSE = \sum_{t} \frac{(\Delta \phi_{\theta}(x,t))^2}{n}$$

(2.3)

Therefore, a linear regression value gives a temporal derivative of the phase and the quality of this linear fit provides a good reliability estimator. Please note that, for uniform motions (no acceleration), the flow computation benefits of the use of a large number of temporal frames. Unfortunately, real-time and (accessible) memory constraints reduce this number to few frames, using typically 3-5 frames. Finally, provided that a minimal number of reliable component velocities are obtained (threshold on the MSE of each orientation (2.3)), an estimate of the full velocity is computed for each pixel by integrating the valid component velocities at that pixel only, as indicated in (2.4).

$$v^*(\mathbf{x}) = \underset{v(\mathbf{x})}{\operatorname{argmin}} \sum_{\theta \in O(\mathbf{x})} \left( \|v_{c,\theta}(\mathbf{x})\| - v(\mathbf{x})^T \frac{v_{c,\theta}(\mathbf{x})}{\|v_{c,\theta}(\mathbf{x})\|} \right)^2$$

(2.4)

Where O(x) is the set of orientations at which the valid component velocities have been obtained for pixel x. As a summary, the following are the different processing stages for the mono-scale optical flow:

- S1 Convolution with 8 Quadrature pair filters tuned at different orientations.

- S2 Phase calculation for each orientation with an arctangent core.

- S3 Temporal filter: wrapping of phase values considering their periodicity for temporal derivative estimation. Three temporal frames are used.

- S4 Velocity component computation as described in [40, 41] and indicated in 2.2.

- S5 Threshold operation based on confidence values and combination of valid values for each orientation for the final velocity vector estimation. Depending on the final confidence value, the optical flow vector or a tag indicating *non valid* data is generated for each pixel.

#### 2.1.2 Reference binocular disparity computation model

This model can be extended to stereo computation: disparity can be calculated as an optical flow with only two frames (left and right). In our case we adopt a simplification that uses the phase difference between left and right image, as described in [43]. In this case, the phase difference is computed from 2.5.

$$\phi(x) = \frac{(\phi^L(x) - \phi^R(x))}{k(x)} = \frac{1}{k_0}atan2(C^R S^L - C^L S^R, C^L C^R + S^L S^R)$$

(2.5)

where we note with  $\phi^L$  and  $\phi^R$  the left and right local image phases,  $C^R$  and  $C^L$  correspond to the values of left and right image pixels after convolving with the even part of the quadrature filter, while  $S^R$  and  $S^L$  are the results after convolving to the odd quadrature filter outputs, arctan2 stands for the principal part of the argument (i.e. the argument belongs to  $[-\pi, \pi]$ ) and finally, k(x) is the average instantaneous frequency of the band pass signal, which can be approximated by  $k_0$ , the quadrature filter peak frequency. Basic steps of mono-scale computation can be summarized as follows:

- 1. Even (C) and odd (S) filtering with quadrature filters pairs of left and right images.

- 2. Disparity computation using equation 2.5 at each orientation and threshold operation assuming  $k(x) \approx K_0$

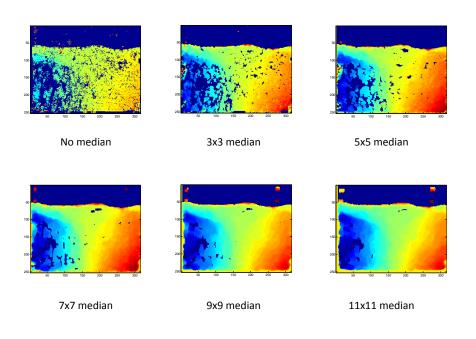

3. Chose of final disparity estimation between different orientations: median value.

We remark that threshold operations are based on the energy of the signal and the last choice of the final values is evaluated through a median value as described in [40]. The median value can be replaced by a more accurate method that for example takes information from exterior; this information can be provided from another algorithm or from a middle or high level control as in the novel concept of Signal to Symbol loop [44].

#### 2.1.3 Local features: magnitude, orientation and phase

Starting from filter response is possible to calculate local features from real part  $C_{\theta}$  and from imaginary part  $S_{\theta}$ . We extract the magnitude and the phase directly from the information of the filter at each orientation. As described in [45] and [46], different methods can be used for accurate edge detection. Quality of the first filtering stage influences the final results and as described in [46] better performances are obtained with second order Gaussian derivatives filters. If we consider 8 oriented filters (computing using Gabor or Gaussian Derivatives), is likely that the local orientation of some features do not fit this discrete number of orientations. Under this circumstance, we require to interpolate the feature values computed from this set of outputs in order to estimate the filter output at the proper signal orientation. Different methods can be used. We note  $E_i$  and  $P_i$  to the magnitude and phase of the filter oriented with  $angle = i * \pi/N$  and noted by  $h_i$ . This filter is expressed by:

$$h_i = c_i + js_i \tag{2.6}$$

And the primitives features are computed with this filter orientation and computed as:

$$Filter \ energy \to E_i = [c_i]^2 + [s_i]^2 \tag{2.7}$$

$$Filter \ phase \to P_i = arg(c_i, s_i) \tag{2.8}$$

If only the main orientation information is required (1-D local signals), we can apply several strategies to interpolate the primitives from this multi-valued set:

i Winner- take-all. We will take for each pixel the phase, energy and orientation of the filter with maximum energy.

$$E_{local} = E_{max} \qquad P_{local} = P_{max} \qquad \theta_{local} = \theta_{max} \tag{2.9}$$

ii Weighted-average: (we consider linear case, though the energy can be power to different orders).

$$E_{local} = \sum_{i} E_{i}^{N} \qquad P_{local} = \frac{\sum_{i} P_{i} E_{i}}{\sum_{i} E_{i}} \qquad \theta_{local} = \sum_{i} \frac{\theta_{i} E_{i}}{\sum_{i} E_{i}}$$

(2.10)

where all angles are properly shifted for avoiding angle wrapping effects.

iii Tensor-based method [45]. Based on a local tensor that projects the different orientations, information can be computed as follows (where j stands for the complex unit):

$$E_{local} = \sum_{i} E_{i}^{N} \tag{2.11}$$

$$\theta_{local} = \frac{1}{2} \arg\left(\sum_{i} \frac{4}{3} \sqrt{c_i^2 + s_i^2} \exp(j2\theta_i)\right)$$

(2.12)

$$P_{local} = \arctan\left(\frac{s}{c}\right) \tag{2.13}$$

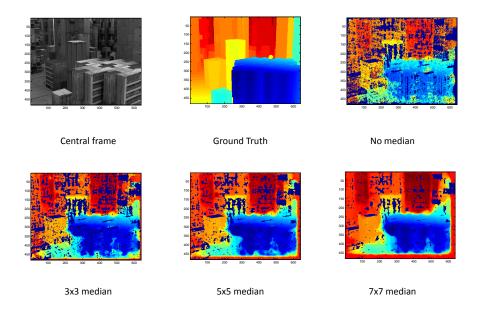

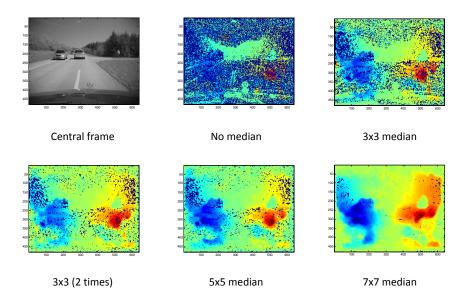

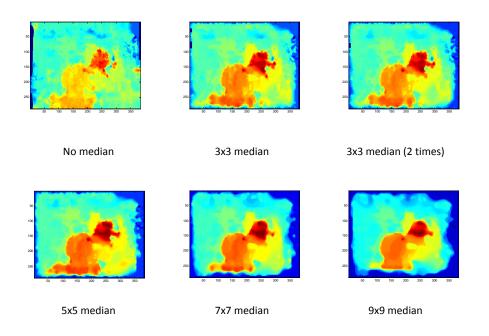

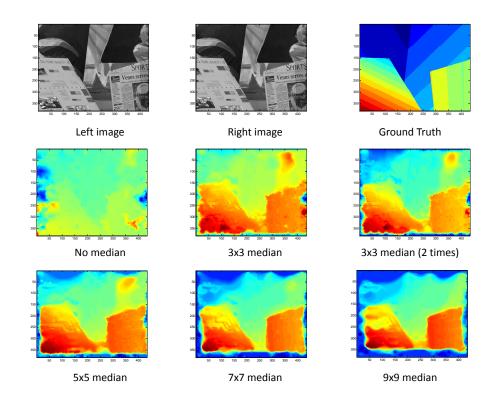

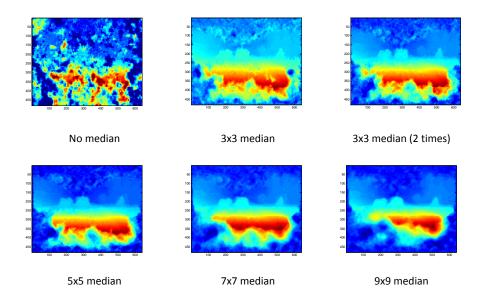

$$c = \sum_{i} c_i \cos^2 \theta_i - \theta_{local} \tag{2.14}$$