#### Universidad de Granada

### DOCTORAL THESIS

# ELECTRICAL CHARACTERIZATION OF RELIABILITY IN ADVANCED SILICON-ON-INSULATOR STRUCTURES FOR SUB-22NM TECHNOLOGIES

Author:

Carlos Márquez González

Advisors:

Dr. Noel Rodríguez Santiago Dr. Francisco J. Gámiz Pérez

A thesis submitted in fulfillment of the requirements to obtain the International Doctor degree as part of the Programa de Doctorado en Física y Ciencias del Espacio at the

Nanoelectronics Research Group, CITIC-UGR Departamento de Electrónica y Tecnología de los Computadores

Granada, February 21, 2017

Editor: Universidad de Granada. Tesis Doctorales

Autor: Carlos Márquez González ISBN: 978-84-9163-171-2 URI: http://hdl.handle.net/10481/45904

## Declaration of authorship

Mr. Carlos Márquez González, as Ph.D Candidate, and Dr. Noel Rodríguez Santiago and Dr. Francisco Gámiz Pérez, as Ph.D Advisors and Professors of Electronics at the Departamento de Electrónica y Tecnología de los Computadores of the Universidad de Granada in Spain,

Guarantee by signing this thesis:

that the research work contained in the present report, entitled *Electrical characterization of reliability in advanced Silicon-On-Insulator structures* for sub-22nm technologies, has been performed under the full guidance of the Ph.D Advisors and, as far as our knowledge reaches, during the work, it has been respected the right of others authors to be cited, when their publications or their results have been used.

Granada, 18<sup>th</sup> February, 2017.

Carlos Márquez González Ph.D Candidate Dr. Noel Rodríguez Santiago Tenured Professor of Electronics

Dr. Francisco Gámiz Pérez Full Professor of Electronics

## Acknowledgements

While this thesis is written in English, I write most of these acknowledgements in Spanish, as it will enforce my thanks.

Me gustaría dedicar unas líneas para agradecer a toda la gente que de algún modo ha contribuido al desarrollo de esta tesis doctoral. Por supuesto, en primer lugar, quiero agradecer a mis directores de tesis por su gran dedicación durante todo este tiempo. A D. Noel Rodríguez Santiago, por como es, por su profesionalidad y su incansable dedicación, además de su incondicional apoyo y orientación en todo momento. Todo un referente para mi, tanto en lo personal como en lo profesional, al que mucho tengo que agradecer. A D. Francisco J. Gámiz Pérez quien me ha apoyado y orientado en todo momento, desde el inicio confiando en mí, hasta el final, solventando todas las adversidades que han ido aconteciendo, y sin el que no hubiera llegado hasta aquí.

Me gustaría agradecer también a Dña. Cristina Fernández, compañera y amiga, que durante todo este tiempo ha sido un gran apoyo. A D. Rafael J. Ruíz a quien quiero agradecer todo su tiempo, su ímpetu y su incansable esfuerzo y profesionalidad, un gran amigo y persona. A D. Santiago Navarro quien desde el primer día ha contribuido, aportando siempre distintos puntos de vista y siendo artifice de las muestras 2D. A Carlos Navarro, por su apoyo y profundas discusiones. También a Cristina Medina que me ha ayudado siempre en todo lo posible y Abadlia Bagdad por su apoyo.

Por supuesto también agradecer al Departamento de Electrónica y Tecnología de los Computadores y a sus últimos directores, D. Enrique Carceller Beltrán y Juan Antonio López Villanueva por poner a mi disposición los medios necesarios para que este trabajo se haya podido realizar. A D. José L. Padilla por sus interesantes y motivantes discusiones, a D. Carlos Sampedro, que ha sido como un compañero de equipo y a D. Andrés Godoy que siempre me ha ofrecido su tiempo y ayuda. Además a todos los integrantes del grupo de Nanoelectrónica.

En el ámbito personal, tengo mucho que agradecer a mis padres, Isabel y Antonio, ejemplos como ninguno de esfuerzo, trabajo y perseverancia que me guian diariamente para ser mejor y conseguir mis metas. A mi hermano, Álvaro, ayuda y apoyo incondicionales, un referente a pesar de su juventud. Y, por supuesto, a Miriam, a la que dificilmente podría agradecer con palabras todo su apoyo, cariño y amor, ni en toda la vida podré recompensártelo lo suficiente. Debo agradecer también todo el apoyo de mi familia, primos, tíos y abuelas y también a mi familia política que siempre me muestran su apoyo, especial mención a Rucio y Magdalena, ejemplos de entereza y esfuerzo ante la adversidad. No podría olvidarme de mis amigos, muchos años de camino juntos.

I am deeply indebted to the members of the Tyndall National Institute. I appreciate the effort of Dr. Ray Duffy, Dr. Nicolás Cordero and Dr. Paul Hurley to do possible my mobility research in Tyndall. Also the intensive work and support of Mr. Gioele Mirabelli and Mr. Dan O'Connell.

Many thanks to Dr. Akiko Ohata, for all the collaboration and technical support.

I would like to express my gratitude to the committee of this thesis.

## Contents

| Lı | st or | Appreviations and Symbols                      |      | V  |

|----|-------|------------------------------------------------|------|----|

| P  | hysic | al constants                                   | I    | X  |

| Li | st of | Figures                                        |      | X  |

| Li | st of | Tables                                         | XXI  | IJ |

| Pi | rolog | rue 2                                          | XXV. | IJ |

| 1  | МО    | SFET Scaling                                   |      | 1  |

|    | 1.1   | Gate scaling: high- $\kappa$ dielectrics       |      | 3  |

|    | 1.2   | Gate scaling: metal stack                      |      | 6  |

|    | 1.3   | SOI technology                                 |      | 8  |

|    |       | 1.3.1 SOI wafers fabrication                   |      | 9  |

|    |       | 1.3.2 FDSOI transistors                        |      | 11 |

|    | 1.4   | Reliability concerns                           |      | 13 |

|    | 1.5   | Other structures and two dimensional materials |      | 16 |

|    | 1.6   | Conclusions                                    |      | 19 |

| 2  | Exp   | perimental Characterization                    | 2    | 21 |

|    | 2.1   | Bare substrates                                | 4    | 21 |

|    |       | 2.1.1 Material resistivity                     | 2    | 22 |

|    |       | 2.1.2 Contact resistance                       | 2    | 26 |

|    | 2.2   | Bare SOI wafers                                | §    | 32 |

|    |       | 2.2.1 Pseudo-MOS technique                     |      | 33 |

|   |      | 2.2.2   | Defects of SOI substrates                                   | 34         |

|---|------|---------|-------------------------------------------------------------|------------|

|   | 2.3  | SOI tı  | ransistors                                                  | 38         |

|   |      | 2.3.1   | Quasi-static characteristics                                | 39         |

|   |      | 2.3.2   | Noise characterization                                      | 44         |

|   |      | 2.3.3   | Over-the-wafer variability characterization                 | 49         |

|   | 2.4  | Concl   | usion                                                       | 51         |

| 3 | Bias | s Insta | ability in Bare SOI Wafers                                  | 53         |

|   | 3.1  | Introd  | luction                                                     | 53         |

|   |      | 3.1.1   | MOSFETs bias temperature instabilities                      | 54         |

|   |      | 3.1.2   | Recovery effect                                             | 57         |

|   |      | 3.1.3   | Motivation and wafer approach                               | 58         |

|   | 3.2  | Exper   | imental methodology                                         | 60         |

|   | 3.3  | Result  | ts and discussion                                           | 63         |

|   |      | 3.3.1   | BI measurements                                             | 63         |

|   |      | 3.3.2   | Recovery effects                                            | 65         |

|   |      | 3.3.3   | Impact of wafer surface preparation                         | 69         |

|   |      | 3.3.4   | Discussion                                                  | 71         |

|   | 3.4  | Concl   | usions                                                      | 72         |

| 4 | Ran  | dom I   | Telegraph Noise in Fully-Depleted SOI MOSFETs               | <b>7</b> 3 |

|   | 4.1  | Introd  | luction                                                     | 73         |

|   | 4.2  | Metho   | odology and experimental setup                              | 77         |

|   |      | 4.2.1   | Determination of the optimum bias condition for the RTN     |            |

|   |      |         | apperance                                                   | 79         |

|   |      | 4.2.2   | Identifying the number of traps involved in the RTN signals | 81         |

|   | 4.3  | Deter   | mination of the trap location                               | 86         |

|   | 4.4  | Tempe   | erature dependence                                          | 90         |

|   | 4.5  | Substi  | rate bias dependence                                        | 94         |

|   | 4.6  | Concl   | usion                                                       | 96         |

| 5 | Imp  | act Io  | nization in Fully-Depleted SOI Transistors                  | 99         |

|   | 5.1  | Introd  | luction                                                     | 99         |

|   | 5.2  | Metho   | odology and experimental setup                              | 103        |

|   | 5.3  | Result  | ts and discussion                                           | 105        |

|              |                 | 5.3.1 Zero-current measurements: body potential characterization 10    | )6         |

|--------------|-----------------|------------------------------------------------------------------------|------------|

|              |                 | 5.3.2 Zero-potential measurements: body current characterization 10    | 7          |

|              |                 | 5.3.3 Gate length dependence                                           | 18         |

|              |                 | 5.3.4 Inversion charge dependence                                      | .0         |

|              |                 | 5.3.5 Substrate bias effect                                            | .5         |

|              | 5.4             | Conclusions                                                            | .5         |

| 6            | Con             | clusions 11                                                            | 7          |

|              | 6.1             | Theoretical Framework                                                  | 7          |

|              | 6.2             | Main achievements                                                      | 8          |

|              | 6.3             | Future research topic                                                  | 20         |

| $\mathbf{A}$ | Elec            | etrical Characterization of Laser Reduced Graphene Oxide 12            | 3          |

|              | A.1             | Introduction                                                           | 23         |

|              | A.2             | Sample Preparation and Experimental Setup                              | 24         |

|              | A.3             | Results and Discussion                                                 | 28         |

|              |                 | A.3.1 Spectroscopic characterization of laser-reduced graphene ox-     |            |

|              |                 | ide                                                                    | 28         |

|              |                 | A.3.2 Electrical characteristics of laser-reduced graphene oxide 13    | 30         |

|              |                 | A.3.3 Initial surface GO concentration and laser power dependencies 13 | 34         |

|              |                 | A.3.4 Temperature dependence                                           | 6          |

|              |                 | A.3.5 Sample comparison                                                | 6          |

|              | A.4             | Conclusion                                                             | \$7        |

| В            | $\mathbf{List}$ | of publications 13                                                     | 9          |

|              | B.1             | Journal papers                                                         | <b>3</b> 9 |

|              | B.2             | Conference contributions                                               | 10         |

|              | B.3             | Book chapters                                                          | 1          |

| $\mathbf{C}$ | Sho             | rt summaries 14                                                        | .3         |

|              | C.1             | English                                                                | 13         |

|              | C.2             | Español                                                                | 16         |

| Bi           | bliog           | ranhy 14                                                               | 8          |

# List of Abbreviations and Symbols

#### Abbreviations

BESOI Bond-and-Etch-back SOI

BI Bias Instability

BJT Bipolar Junction Transistor

BOX Buried Oxide (buried isolation layer of a SOI structure)

BTBT Band-to-band Tunneling

CMOS Complementary MOS technology

CVD Chemical Vapor Deposition

DIBL Drain Induced Barrier Lowering

EOT Equivalent Oxide Thickness

ETSOI Extremely Thin SOI

FET Field-Effect Transistor

FDSOI Fully Depleted SOI

GAA Gate-all-around

GLM Gate Leakage Mechanism

GO Graphene Oxide HKMG High- $\kappa$  Metal Gate IL Interface Layer

ITRS International Technology Roadmap for Semiconductors

JFET Junction Field-Effect Transistor

MEMS Micro-Electro-Mechanical Systems

MIS Metal-Insulator-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MuGFET Multiple Gate Field-Effect Transistor

MSMMeasure-Stress-Measure method

N-channel MOSFET NMOS

**NBTI** Negative Bias Temperature Instability

OTF On-The-Fly method

**PBTI** Positive Bias Temperature Instability

Short Channel Effects

**PDSOI** Partially depleted SOI P-channel MOSFET **PMOS** RTNRandom Telegraph Noise SCE

**SGSOI** Single Gate SOI

S/D tunneling Direct Source to Drain tunneling

SOC System-on-Chip SOI Silicon On Insulator SSSubthreshold Swing

TCAD Technology Computer Aided Design TEM Transmission Electron Microscopy TFET Tunneling Field-Effect transistor

TLMTransmission Line Method

TMD Transition Metal Dichalcogenide

UTB Ultrathin-Body

**UTBB-FDSOI** Ultra-Thin Body and Buried oxide Fully Depleted SOI

## Symbols

| $C_D$       | Depletion capacitance                        |

|-------------|----------------------------------------------|

| $C_f$       | Fixed oxide capacitance                      |

| $C_{it}$    | Interface trapped capacitance                |

| $C_{ot}$    | Oxide trapped capacitance                    |

| $C_{ox}$    | Oxide capacitance                            |

| $C_{Si}$    | Silicon capacitance                          |

| $D_{it}$    | Interface trapped density                    |

| $E_g$       | Bandgap energy                               |

| $J_n$       | Electron current density                     |

| $J_p$       | Holes current density                        |

| $\kappa$    | Dielectric constant                          |

| L           | Gate length                                  |

| $L_T$       | Transfer length                              |

| $\mu_n$     | Electron mobility                            |

| n           | Electron concentration                       |

| p           | Hole concentration                           |

| $\phi_m$    | Metal workfunction                           |

| $\phi_n$    | Potential difference between $E_C$ and $E_F$ |

| $\phi_p$    | Potential difference between $E_V$ and $E_F$ |

| $\Phi_{fb}$ | Flatband potential                           |

| $\Phi_s$    | Surface potential                            |

| $Q_f$       | Fixed oxide charge                           |

| $Q_{it}$    | Interface trapped charge                     |

| $Q_m$       | Mobile oxide charge                          |

| $Q_{ot}$    | Oxide trapped charge                         |

| $ ho_c$     | Contact resistivity                          |

| $R_C$       | Contact resistance                           |

| $R_m$       | Metal resistance                             |

| $R_{sh}$    | Sheet resistance                             |

| $R_T$       | Total resistance                             |

| $SiO_2$     | Silicon dioxide                              |

| T           | Temperature (Absolute)                       |

| $T_{OX}$    | Gate dielectric thickness                    |

| $T_{Si}$    | Silicon Thickness                            |

| u        | Sound velocity in the material |

|----------|--------------------------------|

| $V_{DD}$ | Supply voltage                 |

| $V_{DS}$ | Drain-to-source voltage        |

| $V_{GS}$ | Gate-to-source voltage         |

| $V_{TH}$ | Threshold voltage              |

## Physical constants

| $\epsilon_0$     | vacuum permittivity       | $8.85418782 \cdot 10^{-12} \text{ F/m}$              |

|------------------|---------------------------|------------------------------------------------------|

| $m_0$            | electron rest mass        | $9.10938291 \cdot 10^{-31}~{\rm Kg}$                 |

| h                | Planck's constant         | $6.62606957 \cdot 10^{-34} \text{ J} \cdot \text{s}$ |

| $\hbar$          | reduced Planck's constant | $1.05457172 \cdot 10^{-34} \text{ J} \cdot \text{s}$ |

| $k_{\mathrm{B}}$ | Boltzmann's constant      | $1.38064881\cdot 10^{-23}~{\rm J/K}$                 |

| q                | elementary charge         | $1.60217656 \cdot 10^{-19} \text{ C}$                |

# List of Figures

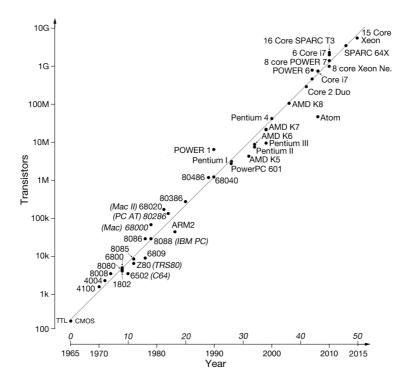

| 1.1  | Moore's law over time (line). Correspondence with some commer-                 |    |

|------|--------------------------------------------------------------------------------|----|

|      | cial processors is shown                                                       | 3  |

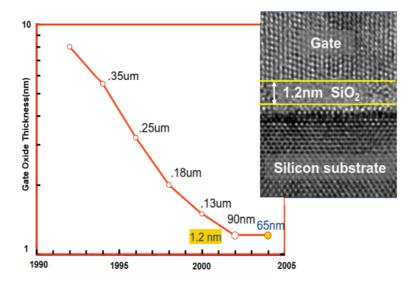

| 1.2  | Gate oxide thickness scaling according to the technology node. In-             |    |

|      | set: TEM image of a 90nm node with a dielectric thickness of $1.2\mathrm{nm}.$ | 4  |

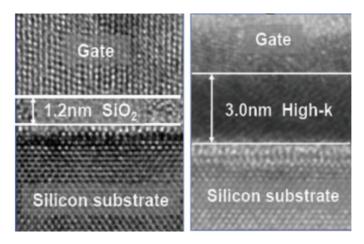

| 1.3  | TEM image of a 1.2nm EOT transistor (left) using 1.2nm of $SiO_2$              |    |

|      | layer in the gate oxide, (right) using 3nm of high- $\kappa$ material as gate  |    |

|      | oxide                                                                          | 5  |

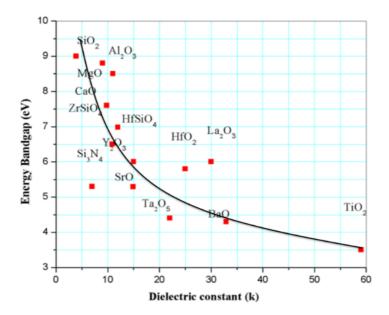

| 1.4  | Band gap as a function of the dielectric constant $(\kappa)$ for different     |    |

|      | high- $\kappa$ insulator materials                                             | 6  |

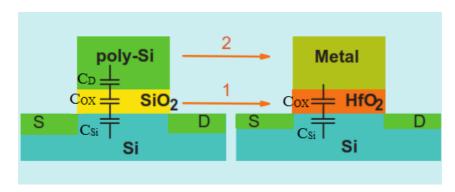

| 1.5  | Illustration of the replacement of $SiO_2$ gate oxide and the poly-Si          |    |

|      | gate by high- $\kappa$ gate oxide and metal gate (HKMG)                        | 7  |

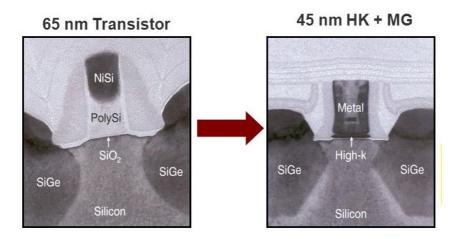

| 1.6  | TEM image of (left) a 65nm node technology transistor, (right) a               |    |

|      | 45nm node technology transistor implementing high- $\kappa$ and metal          |    |

|      | gate technologies                                                              | 8  |

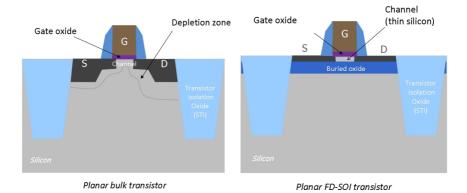

| 1.7  | Schematic cross-section of transistor structure: (left) planar bulk            |    |

|      | transistor, (right) planar SOI transistor                                      | 9  |

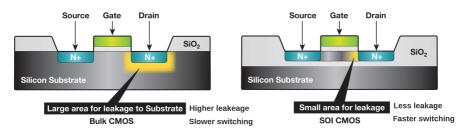

| 1.8  | Scheme of leakage areas in: (left) bulk transistors, (right) Silicon-          |    |

|      | on-Insulator transistor.                                                       | 10 |

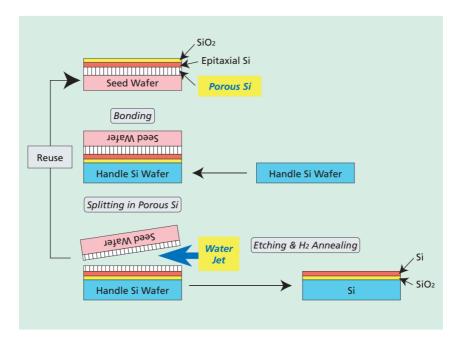

| 1.9  | Schematic illustration of ELTRAN process flow                                  | 11 |

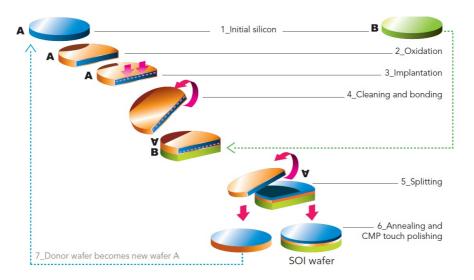

| 1.10 | Schematic illustration of Smart-cut process flow                               | 12 |

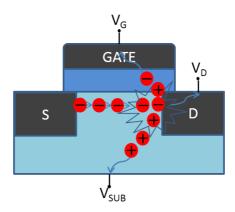

| 1.11 | Substrate bias illustration in FDSOI transistor                                | 13 |

| 1.12 | Factors contributing to carrier mobility degradation in a HKMG                 |    |

|      | transistor                                                                     | 14 |

| 1.13 | IMEC roadmap for the next technology nodes                                     | 16 |

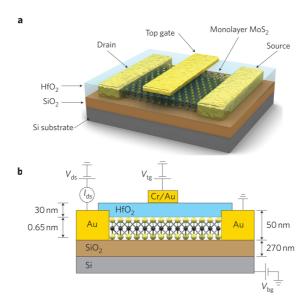

| 1.1 | 4 Schematic illustration of quality as a function of cost (price) for<br>the different graphene fabrication methods | 17 |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 1.1 |                                                                                                                     | 11 |

| 1.1 | dimensional schematic view, (b) Cross-sectional view with electrical                                                |    |

|     |                                                                                                                     | 19 |

|     | connections                                                                                                         | 19 |

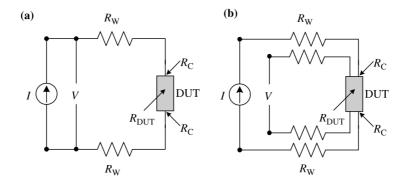

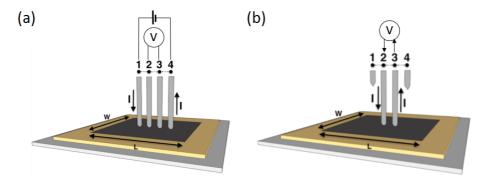

| 2.1 | Schematic illustration of (a) two-point and (b) four-point resistance                                               |    |

|     | measurement configuration                                                                                           | 22 |

| 2.2 | (a) Four point-contact setup: current $I$ is forced between probes 1                                                |    |

|     | and 4 by applying a constant bias $V_{1-4}$ while the voltage drop is                                               |    |

|     | measured between probes 2 and 3. (b) Two point-contact setup:                                                       |    |

|     | current $I$ and voltage $V$ are simultaneously applied and measured                                                 |    |

|     | through the same probes $(2 \text{ and } 3)$                                                                        | 23 |

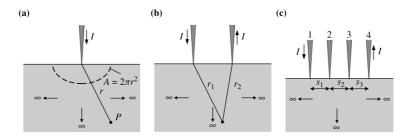

| 2.3 | Schematic illustration showing current flow and voltage measure-                                                    |    |

|     | ment in: (a) one-point probe, (b) two-point probe, and (c) collinear                                                |    |

|     | four-point probe configuration                                                                                      | 25 |

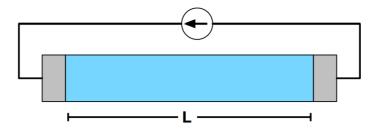

| 2.4 | Cross-sectioned illustration of a resistor with two lateral contacts                                                | 27 |

| 2.5 | Illustration of total resistance as a function of different device                                                  |    |

|     | lengths for the contact and sheet resistance extraction                                                             | 28 |

| 2.6 | Cross-sectioned illustration of two contacts deposited on a semi-                                                   |    |

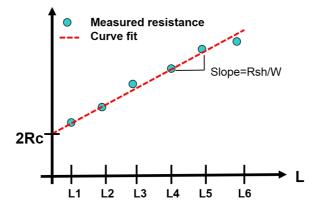

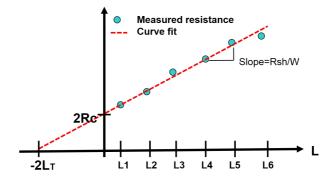

|     | conductor layer. Current flow is represented by lines                                                               | 29 |

| 2.7 | Illustration of total resistance as a function of different device                                                  |    |

|     | length for the contact and sheet resistance extraction                                                              | 30 |

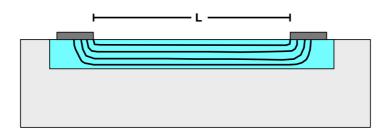

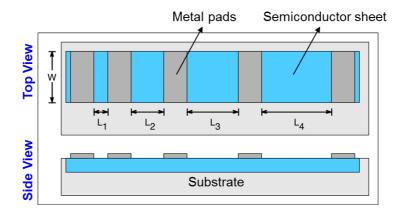

| 2.8 | Illustration of structure designed for TLM characterization                                                         | 30 |

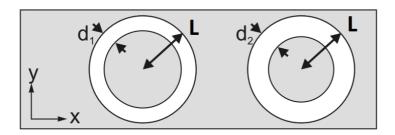

| 2.9 | Circular contact resistance test structure. The gray regions repre-                                                 |    |

|     | sents metallic regions. (a) Spacing $d$ and radius $L$ are defined in                                               |    |

|     | the two structures                                                                                                  | 31 |

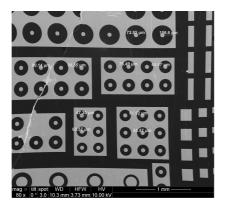

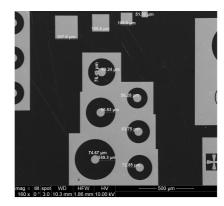

| 2.1 | 0 TEM image of circular contact resistance test structures on reduced                                               |    |

|     | graphene oxide. The gray zones represent metallic regions. Feature                                                  |    |

|     | sizes are shown in the image                                                                                        | 32 |

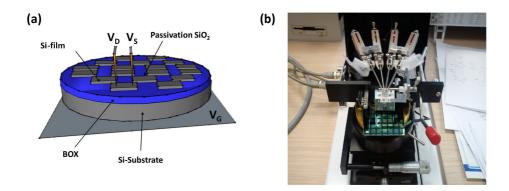

| 2.1 | 1 (a) Pseudo-MOSFET structure. Two probes act as drain and                                                          |    |

|     | source contacts. The bulk Si and the buried oxide act as gate                                                       |    |

|     | contact and gate oxide respectively. (b) Manual probe station used                                                  |    |

|     | for the experimental characterization                                                                               | 34 |

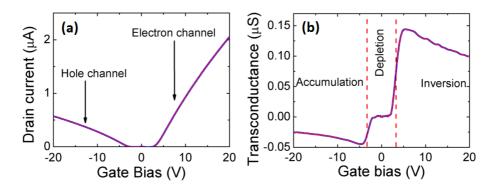

| 2.12 | (a) Drain current as a function of gate bias. (b) Transconductance                                                               |    |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

|      | as a function of gate bias. Non-passivated bare SOI wafer, $T_{Si} =$                                                            |    |

|      | 88 nm, $T_{BOX} = 145$ nm, $V_D = 20$ mV                                                                                         | 35 |

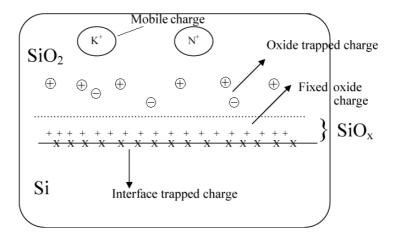

| 2.13 | Schematic cross-sectioned illustration of the oxide charges in a                                                                 |    |

|      | $SiO_2 - Si$ interface                                                                                                           | 36 |

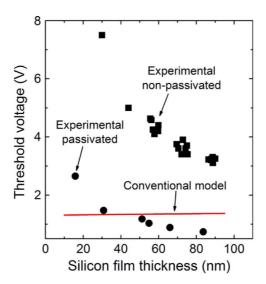

| 2.14 | Comparison between experimental values of threshold voltage in (circles) passivated and (squares) nonpassivated samples and the  |    |

|      | conventional pseudo-MOSFET model                                                                                                 | 38 |

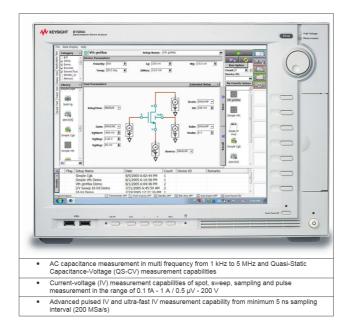

| 2.15 | Front view of the semiconductor parametric analyzer Agilent B1500 showing a generic test in a four-terminal transistor. The main |    |

|      | properties are summarized at the bottom                                                                                          | 39 |

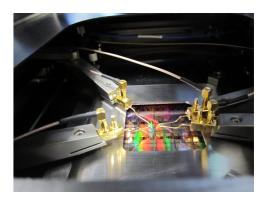

| 2.16 | (Left) Wafer is loaded in the automatic probe station. (Right) Golden electroplated probes contact with the pads of a transistor |    |

|      | in the wafer                                                                                                                     | 40 |

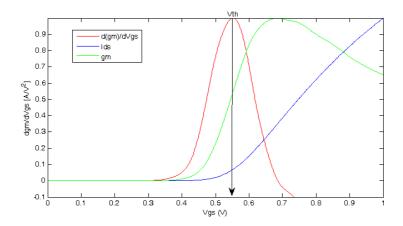

| 2.17 | Example of threshold voltage extraction from experimental charac-                                                                |    |

|      | terization of drain current-gate voltage using the transconductance                                                              |    |

|      | derivative method                                                                                                                | 42 |

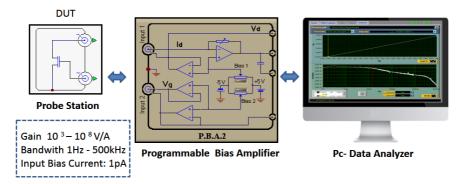

| 2.18 | Schematic illustration of our experimental characterization setup                                                                |    |

|      | of low-frequency noise in a transistor (device under test, DUT) by                                                               |    |

|      | using a programmable bias amplifier and two PCs for data and                                                                     |    |

|      | result representation. The properties inside the square correspond                                                               |    |

|      | to the Synergie Concept analyzer used in this thesis                                                                             | 45 |

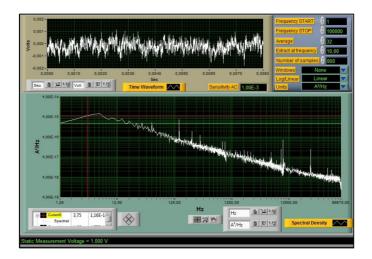

| 2.19 | Spectral experimental characterization of current noise in a SOI                                                                 |    |

|      | transistor biased with 1V at the drain and gate terminals. At the                                                                |    |

|      | top of the image, the voltage fluctuations at the output of the ${\rm I/V}$                                                      |    |

|      | amplifier in time domain are shown. At the bottom, the current                                                                   |    |

|      | power spectral density is plotted as a function of the frequency.                                                                |    |

|      | Some experimental setup parameters appear in the top-right side                                                                  | 46 |

| 2.20 | Experimental results of low-frequency noise in a device affected by                                                              |    |

|      | Random Telegraph Noise                                                                                                           | 48 |

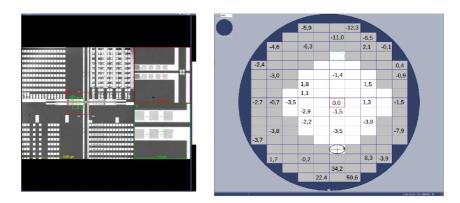

| 2.21 | (Left) Image of the alignment process in a wafer assisted by special                                                             |    |

|      | marks (crosses and squares) patterned for this purpose. (Right)                                                                  |    |

|      | Scheme of the wafer where thickness relative differences among                                                                   |    |

|      | dies are labeled after the profiling process                                                                                     | 49 |

|      |                                                                                                                                  |    |

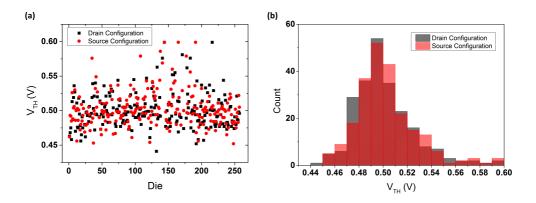

| 2.22 | (a) $V_{TH}$ extraction for 255 dies on the wafer when $V_{DS}$ is biased through the drain (Drain configuration) and through the source (Source configuration). (b) Histogram of the threshold voltage as |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0.00 | a function of the bias configuration (drain or source)                                                                                                                                                     | 50 |

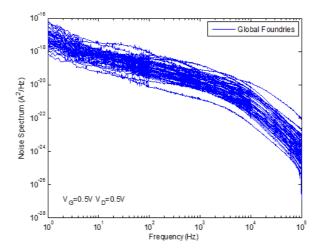

| 2.23 | Current power spectral density of a specific transistor in several dies along the wafer. $V_D$ =0.5V $V_G$ =0.5V                                                                                           | 51 |

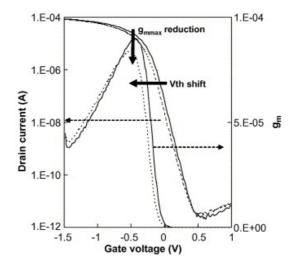

| 3.1  | Drain current and transconductance curves as a function of the gate voltage for a 2nm-thick oxide p-MOSFET transistor before (line) and after 10,000 seconds of stress at 398 K (dashed line)              | 54 |

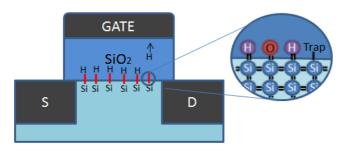

| 3.2  | Schematic illustration of the interface between the silicon channel and the gate $SiO_2$ oxide. Despite the fact that traps are annealed by hydrogen atoms, during a stress period some hydrogen atoms     |    |

| 3.3  | might diffuse generating these traps again                                                                                                                                                                 | 55 |

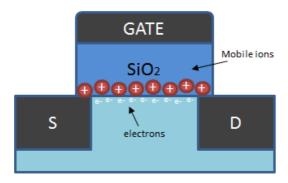

|      | ions and channel charge when a positive voltage is applied in the gate terminal is a source of instability.                                                                                                | 56 |

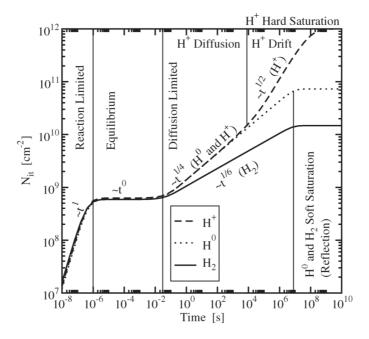

| 3.4  | Schematic illustration of RD model divided in five regions with different time behaviors and diffusion species                                                                                             | 57 |

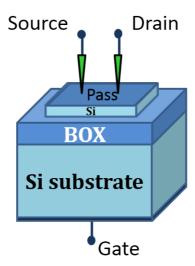

| 3.5  | Pseudo-MOSFET configuration used for parameter extraction of SOI wafers: Two needles on the surface form source and drain                                                                                  |    |

| 3.6  | terminals. The substrate and BOX act as the gate                                                                                                                                                           | 58 |

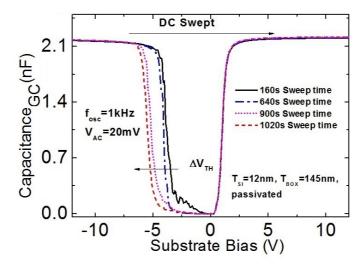

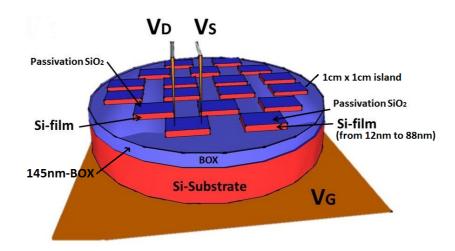

| 3.7  | threshold voltage                                                                                                                                                                                          | 59 |

|      | characterization                                                                                                                                                                                           | 60 |

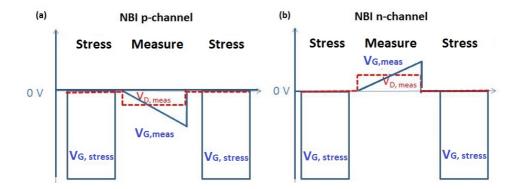

| 3.8  | Illustration of MSM method for characterizing negative BI stress (NBI) in: (a) p-channels substrate and (b) n-channel substrate.  Drain and source are grounded. During the measurement phase,             |    |

|      | the gate voltage is swept at a constant drain bias                                                                                                                                                         | 61 |

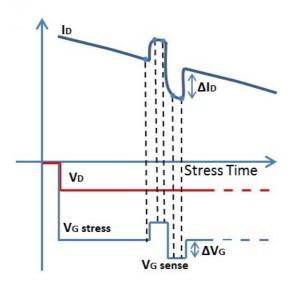

| 3.9  | Illustration of OTF method for NBI in p-channel. During the neg-                                |                 |

|------|-------------------------------------------------------------------------------------------------|-----------------|

|      | ative gate bias stress, the drain bias is kept constant. Variations in                          |                 |

|      | the gate bias $(V_{Gsense})$ allow obtaining the transconductance and                           |                 |

|      | $V_{TH}$ shift from the measured current                                                        | 62              |

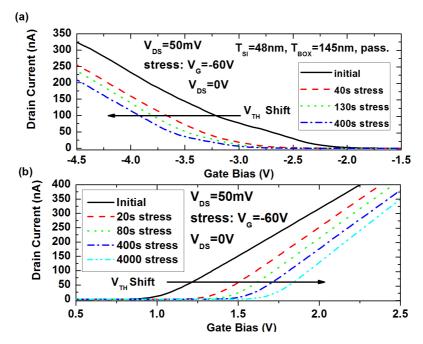

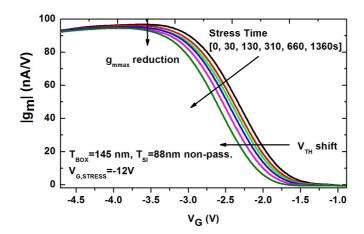

| 3.10 | $I_D(V_G)$ characteristics showing, (a) significant negative $V_{TH}$ shift                     |                 |

|      | in hole channel, and (b) positive $V_{TH}$ shift in electron channel,                           |                 |

|      | after different stress times in NBI measurement conditions. Gate                                |                 |

|      | voltage during stress $V_{G,stress} =$ -60V, $T_{Si}$ =48nm, $T_{BOX}$ =145nm,                  |                 |

|      | passivated surface, 300 K                                                                       | 64              |

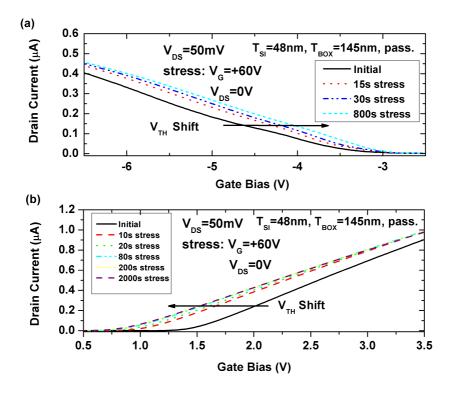

| 3.11 | $I_D(V_G)$ characteristics showing, (a) significant positive $V_{TH}$ shift                     |                 |

|      | in hole channel, and (b) negative $V_{TH}$ shift in electron channel,                           |                 |

|      | after different stress times in PBI measurement conditions. Gate                                |                 |

|      | voltage during stress, $V_{G,stress}$ , is 60V. $T_{Si}$ =48nm, $T_{BOX}$ =145nm,               |                 |

|      | passivated surface, 300 K                                                                       | 65              |

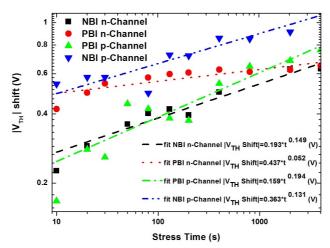

| 3.12 | $V_{TH}$ shift as a function of time after Negative or Positive BI in                           |                 |

|      | hole and electron channels. The stress bias applied to the gate is                              |                 |

|      | -60V for NBI and $+60\mathrm{V}$ for PBI. Logarithmic scale. The power law                      |                 |

|      | fitting is showed. The $I_D(V_G)$ characteristics, used for extracting                          |                 |

|      | the threshold voltage in the MSM method are obtained by sweep-                                  |                 |

|      | ing the gate (substrate) from $0\mathrm{V}$ to $-20\mathrm{V}$ for hole channels and            |                 |

|      | from 0V to 20V for electron channels. $ V_{DS} =50$ mV, $T_{Si}=48$ nm,                         |                 |

|      | $T_{BOX}$ =145nm, passivated, 300 K                                                             | 66              |

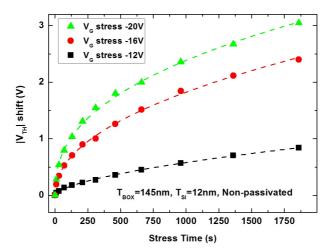

| 3.13 | $V_{TH}$ shift as a function of the stress time for three different stress                      |                 |

|      | voltages (symbols) and the corresponding fitting curves (dashed                                 |                 |

|      | lines). Results obtained using the MSM method at room tempera-                                  |                 |

|      | ture. $ V_{DS} =50\text{mV},T_{Si}=12\text{nm},T_{BOX}=145\text{nm},\text{non-passivated sur-}$ |                 |

|      | face                                                                                            | 66              |

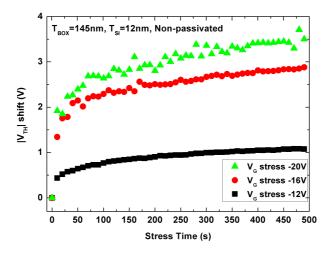

| 3.14 | $V_{TH}$ shift as a function of the stress time for three different stress                      |                 |

|      | voltages by using the OTF method at room temperature. $ V_{DS} $ =50mV                          | ,               |

|      | $T_{Si}$ =12nm, $T_{BOX}$ =145nm, non-passivated surface                                        | 67              |

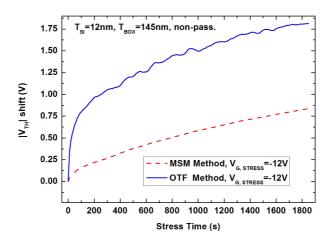

| 3.15 | $V_{TH}$ shift using On-The-Fly method (OTF) and Measure-Stress-                                |                 |

|      | Measure method (MSM). Non-passivated wafers, $ V_{DS}  = 50 \text{mV}, T_{Si} = 12 \text{mV}$   | $2\mathrm{nm},$ |

|      | $T_{BOX}$ =145nm, 300K                                                                          | 68              |

| 3.16 | Transconductance measured on p-channel after NBI stress. T=300K.                                | 68              |

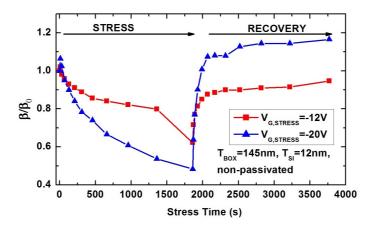

| 3.17 | (a) $\beta/\beta_0$ ratio after stress as a function of time and recovery periods for two different stress biases. T=300K                                                                                                                                                                                                                                                                                                                                                                                                       | 69 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

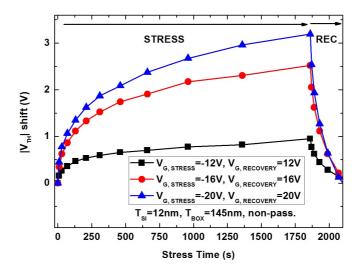

| 3.18 | $V_{TH}$ shift during the stress and the recovery period (REC period after 1860s of stress) for three different stress voltages using MSM method. During the recovery period the magnitude of gate voltage is the same than during the stress period but with opposite polarity. Measurements are performed at room temperature                                                                                                                                                                                                 | 69 |

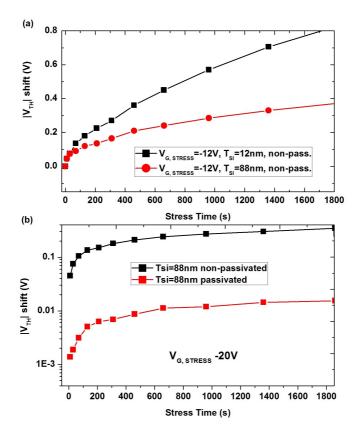

| 3.19 | $V_{TH}$ shift during NBI stress for hole channels, (a) for $V_{G,,stress}$ = -12 V in two non-passivated wafers with different Si layer thickness and (b) for $V_{G,stress}$ =-20 V in passivated and non-passivated wafers with same Si film thickness. $ V_{DS} $ =50mV, $T_{BOX}$ =145nm, at room temperature.                                                                                                                                                                                                              | 70 |

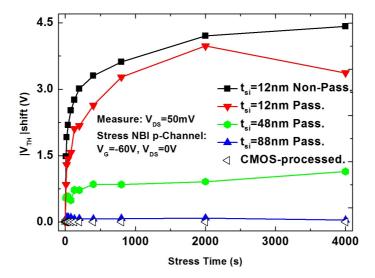

| 3.20 | $V_{TH}$ shift after NBI in hole channels. Comparison between bare SOI wafers with different Si layer thickness and a fully processed MOSFET wafer, $ V_{DS} $ =50mV, $T_{BOX}$ =145nm, 300K                                                                                                                                                                                                                                                                                                                                    | 71 |

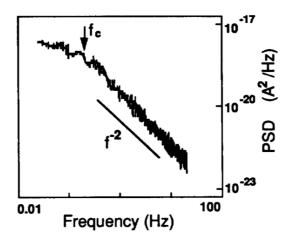

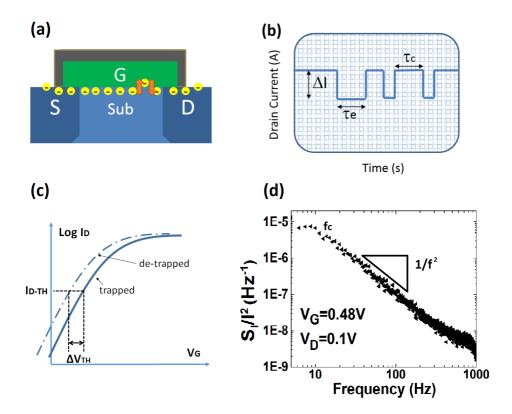

| 4.1  | (a) Schematic illustration of a channel carrier trapped/detrapped by a trap in the gate oxide. (b) Trapping/detrapping events result in a two-level current characteristic where the capture and emission time are determined from the average high and low current levels respectively. (c) Threshold voltage shift observed between trapped (solid line) and detrapped (dashed line) carrier levels. (d) The power spectrum density (PSD) of the RTN fluctuation shows a Lorentzian shaped spectrum with a slope of $(1/f^2)$ | 75 |

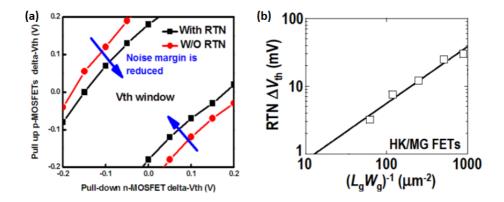

| 4.2  | (a) Comparison of the noise margin in a SRAM memory when is (and not) affected by RTN. (b) Threshold voltage shift as a function of the inverse of the transistor area for HKMG MOSFETs                                                                                                                                                                                                                                                                                                                                         | 76 |

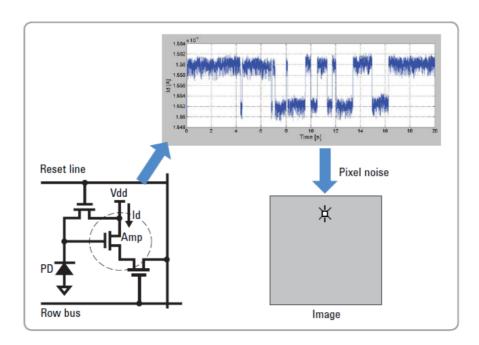

| 4.3  | Schematic illustration of a CMOS image sensor. The scaling of the amplifier (bottom left) makes it more susceptible to RTN (top), generating erroneous white spots (bottom right). Reproduced from Agilent Report 2015                                                                                                                                                                                                                                                                                                          | 76 |

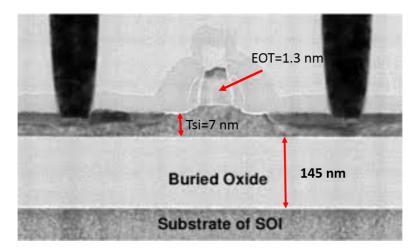

| 4.4  | Cross-sectional TEM image of a FD-SOI transistor used for the electrical characterization of RTN.                                                                                                                                                                                                                                                                                                                                                                                                                               | 78 |

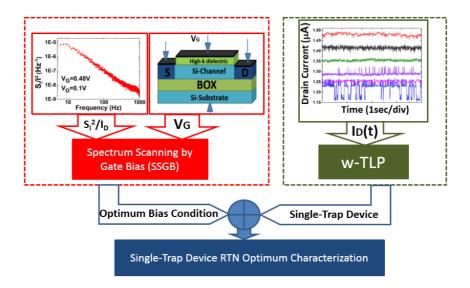

| 4.5  | random telegraph noise characterization in transistors. The method permits the optimum RTN characterization of single-trap devices combining the Spectral Scanning by Gate Bias technique and the Time Lag Plot method.                                                                                                                                                                                                                     | 79 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

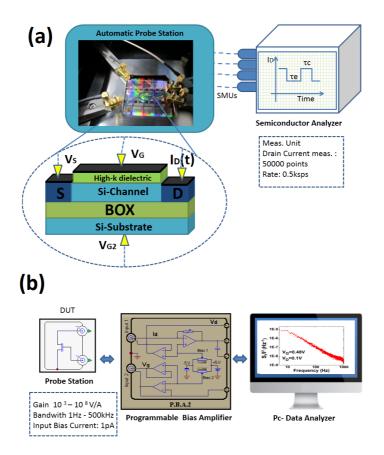

| 4.6  | (a) Schematic of the experimental setup developed for the RTN measurements. Each terminal of the transistor is monitored by an Agilent B1517A SMU at a rate of 500 samples per second. Automatic measurements around the wafer are implemented through a Süss semiautomatic probe station. (b) Schematic of the measurement setup used to extract the spectral noise power of the drain current based on a programmable low-noise amplifier | 80 |

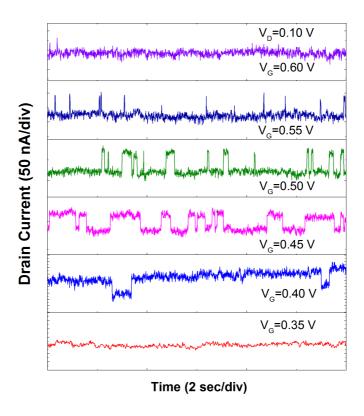

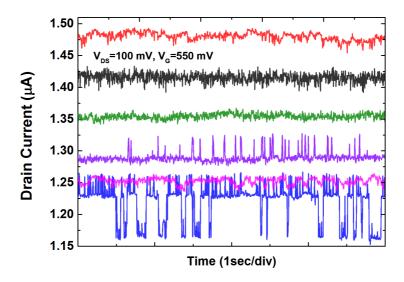

| 4.7  | Drain current traces as a function of the time from a transistor affected by random telegraph noise for different gate voltages. (b) Normalized current noise power $(S_I/I^2)$ dependence with frequency for different gate voltages $(V_G)$ . (c) Normalized current noise spectral density dependence with gate voltage (SSGB) for the transistor of figure (b)                                                                          | 81 |

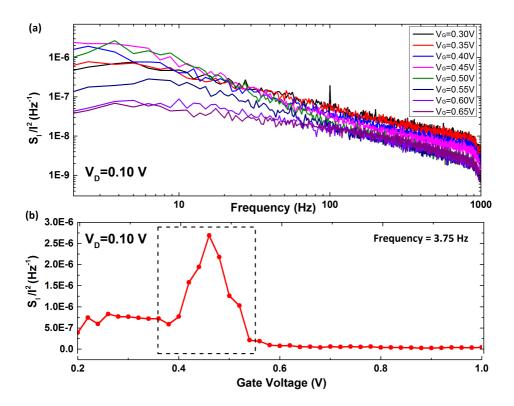

| 4.8  | (a) Normalized current noise power $(S_I/I^2)$ dependence with frequency for different gate voltages $(V_G)$ . (b) Normalized current noise spectral density dependence with gate voltage for the transistor of figure (a)                                                                                                                                                                                                                  | 82 |

| 4.9  | Drain current traces of different devices presenting multi-trap RTN.                                                                                                                                                                                                                                                                                                                                                                        | 83 |

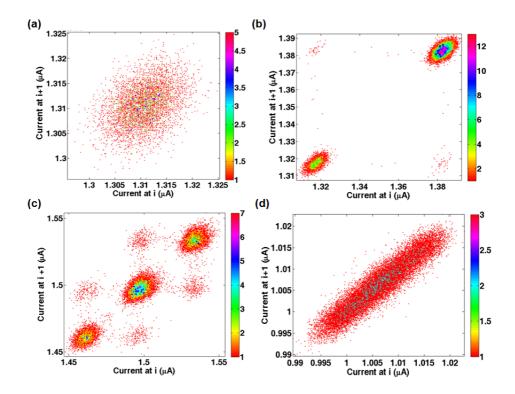

| 4.10 | Traps constellations in the Weighted TLP space of drain current signals: (a) cloud: transistor lacking of RTN signature (only thermal noise is reflected). (b) Transistor with two lobes (states) in the TLP constellation result from the single active trap. (c) Transistor with a three-lobes constellation identifying the characteristic signature of two traps. (d) Spread cloud corresponding to a transistor with multi-trap events | 84 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

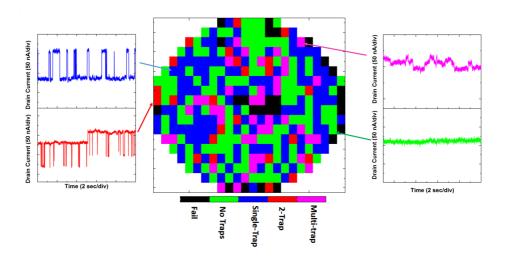

| 4.11 | Distribution of the number of current levels detected in the transistors over the wafer at $V_D = 0.1V$ and $V_G = 0.5V$ . (Left) Examples of transistors with two and three current levels (top and down respectively). (Right) Examples of multi-current level (> 3) and RTN-free transistors (top and down respectively) | 85  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

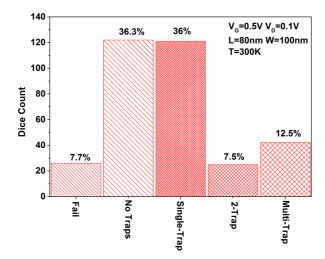

| 4.12 | Histogram of the number of dice presenting a determined number of traps in the device under study detected from the RTN characterization ( $L=100nm,W=80nm,$ one transistor per die). Same bias than in Figure 4.11                                                                                                         | 86  |

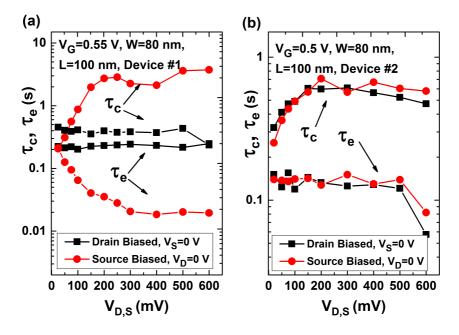

| 4.13 | Capture and emission time dependence with the drain/source bias applied (a) to a device where an asymmetry appears between drain and source configuration and (b) to a device where drain and source configuration present similar results.                                                                                 | 87  |

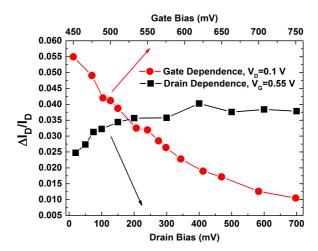

| 4.14 | Normalized amplitude of the RTN signals as a function of the gate bias and the drain bias. Same device than in Figure 4.13.b (trap located in the middle of the channel). $L=100nm,W=80nm.$                                                                                                                                 | 88  |

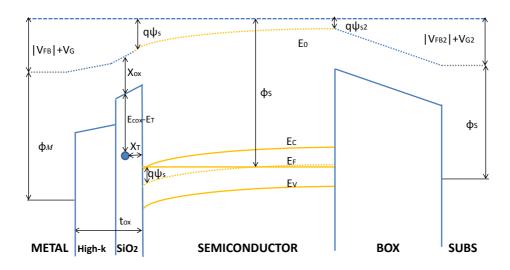

| 4.15 | Energy-bands diagram for a back-biased $(V_{BG})$ SOI-MOSFET with a single trap inside the gate insulator                                                                                                                                                                                                                   | 89  |

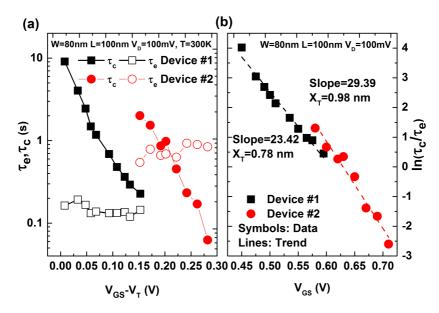

| 4.16 | (a) $\tau_c$ and $\tau_e$ dependencies with the gate bias corresponding to two SOI transistor with $L=100nm, W=80nm$ and featuring a single active trap. (b) $ln\frac{\tau_c}{\tau_e}$ plot to extract the physical and energetic position of the trap                                                                      | 91  |

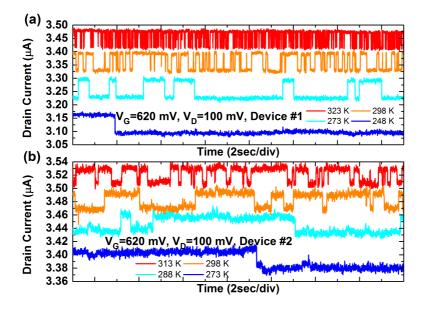

| 4.17 | Drain current signals at a constant bias in two transistors affected by RTN. For case (a), only at high temperature, $\tau_e < \tau_c$ whereas in case (b) $\tau_e < \tau_c$ in all the measured temperature range. $V_{t,1} = 0.442V, V_{t,2} = 0.428V.$                                                                   | 92  |

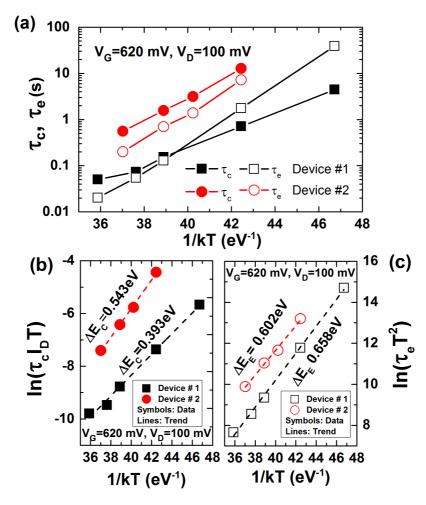

| 4.18 | $100nm$ , $W=80nm$ SOI transistors with a single active trap. (b) $Ln(\tau_c I_D T)$ vs. $1/kT$ for the extraction of the capture activation energy. (c) $Ln(\tau_e T^2)$ vs. $1/kT$ for the extraction of the emission                                                                                                     | 0.0 |

|      | activation energy                                                                                                                                                                                                                                                                                                           | 93  |

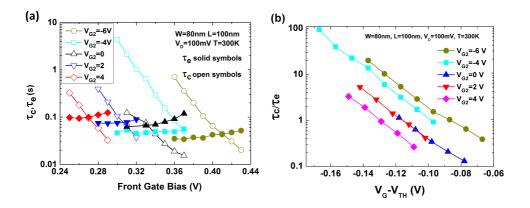

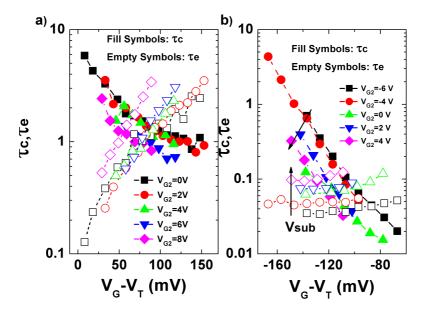

| 4.19 | (a) Capture, $\tau_c$ , and emission, $\tau_e$ , evolution as a function of the gate bias for different substrate biases $(V_{G2})$ . (b) $\tau_c/\tau_e$ ratios as a function of the gate overdrive bias for different negative and positive substrate biases                                                                                                       | 95  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

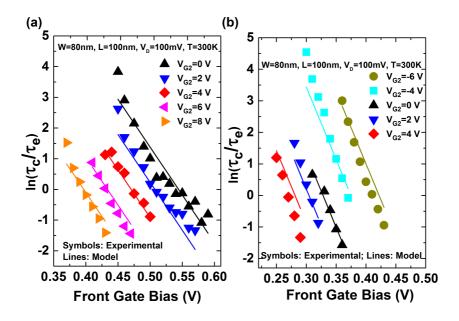

| 4.20 | Comparison of the experimental values of $ln(\tau_c/\tau_e)$ (symbols) and the proposed model (lines) for two devices (a and b)                                                                                                                                                                                                                                      | 96  |

| 4.21 | $	au_c$ and $	au_e$ ratios as a function of the gate overdrive voltage for different substrates biases in the same devices than in Fig. 4.20                                                                                                                                                                                                                         | 97  |

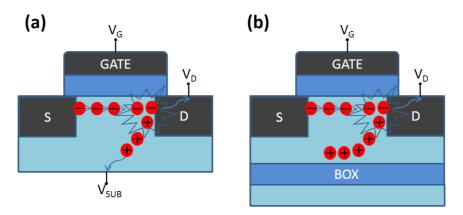

| 5.1  | Schematic illustration of the impact ionization in a N-MOSFET.  (a) In bulk transistors, electrons are collected by the drain while holes escape through the substrate. (b) In Silicon-On-Insulator transistors, the minority carriers, electrons, are collected by the drain, while the majority carriers, holes, cannot escape through the substrate of the device | 101 |

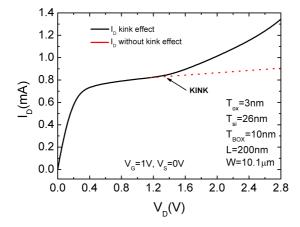

| 5.2  | Experimental drain current as a function of drain bias in a SOI transistor where kink effect is observable (black line), and the current without kink effect (red line) is approached                                                                                                                                                                                | 101 |

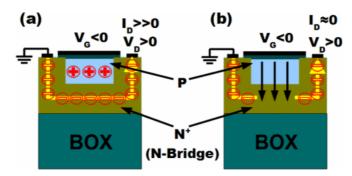

| 5.3  | A2RAM memory cell schematic. (a) The top semi-body stores the holes generated by impact ionization or band-to-band tunneling whereas the N-bridge is used for current sensing ('1' state). (b) The holes are evacuated ('0' state)                                                                                                                                   | 102 |

| 5.4  | Schematic illustration of carriers being injected into the gate dielectric. These <i>hot carriers</i> (injected into the gate) might induce device degradation and reduce the transistor lifetime. This degradation effect is considered as a major reliability problem in the recent technologies                                                                   | 103 |

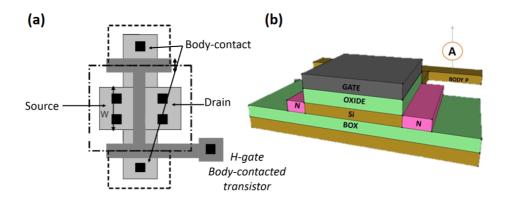

| 5.5  | (a) Layout of the H-gate body-contacted SOI-MOSFETs used for the study. (b) Schematic 3D illustration of the body-contacted SOI device                                                                                                                                                                                                                               | 104 |

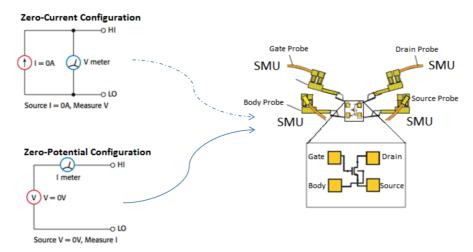

| 5.6  | Schematic illustration of the experimental configuration used for the characterization of body-contacted devices. Zero-current configuration allows to measure the body potential and Zero-potential configuration sets the body-contact potential at $0V$ and allows to measure the hole current generated by impact ionization. The five-terminal H-gate body-contacted SOI-MOSFETs are biased and measured by using source-measure-units (Substrate contact through the platter of the equipment is not shown) |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

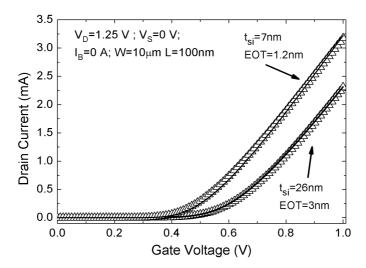

| 5.7  | $I_D-V_G$ characteristic of a standard $100nm$ -length $10\mu m$ -width SOI transistor (line) and the H-gate body-contacted counterpart (symbols). Results for thin and ultra-thin body transistors are shown                                                                                                                                                                                                                                                                                                     |

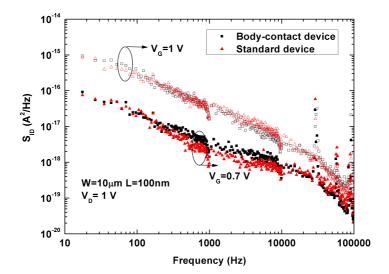

| 5.8  | Drain current power spectral density as a function of the frequency for a body-contacted FD-SOI transistor (black symbols), and an equivalent device without body-contact (red symbols). Two bias points ( $V_G = 1V$ and $V_G = 0.7V$ ) are shown                                                                                                                                                                                                                                                                |

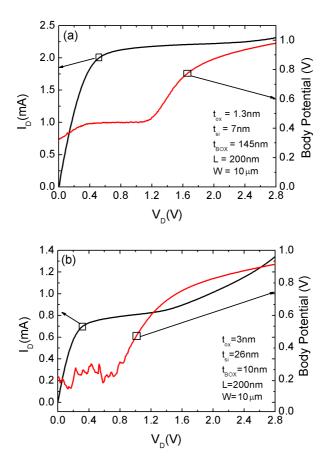

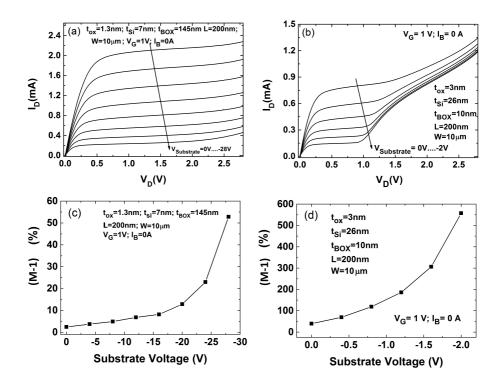

| 5.9  | Drain current and body potential in a SOI-MOSFET with $L=200nm$ and $W=10.1\mu m$ when the body-contact is kept under zero-current condition $(I_B=0)$ . Gate voltage is set to $V_G=1V$ . (a) Ultra-thin body device $t_{Si}=7nm$ , (b) thin body device $t_{Si}=26nm$ . 108                                                                                                                                                                                                                                     |

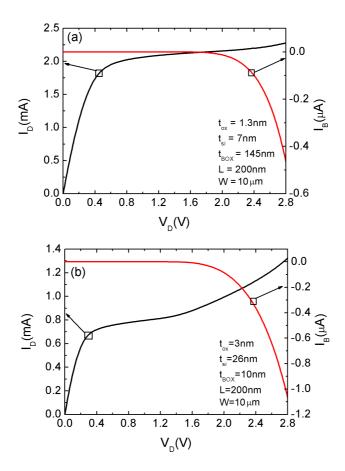

| 5.10 | Drain and body currents on a SOI-MOSFET with $L=200nm$ and $W=10.1\mu m$ when the body-contact is kept under zero-potential condition $(V_B=0)$ . Gate voltage is set to $V_G=1V$ . (a) Ultra-thin body device $t_{Si}=7nm$ , (b) thin body device $t_{Si}=26nm$ 109                                                                                                                                                                                                                                              |

| 5.11 | (a) Drain current as a function of the drain voltage for different gate lengths. A clear increase in the impact ionization (kink effect) is observable in the shorter devices. (b) Body-contact current as a function of the drain voltage. The shorter device, the higher hole injection in the body of the transistor                                                                                                                                                                                           |

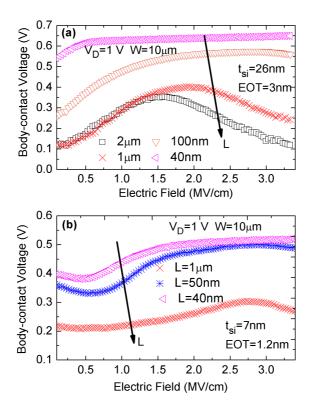

| 5.12 | Dependence of the measured body-voltage on the gate voltage for devices with: (a) $EOT = 3nm$ , $t_{Si} = 26nm$ and length of $2\mu m$ , $1\mu m$ , $0.1\mu m$ and $0.05\mu m$ . (b) $EOT = 1.2nm$ , $t_{Si} = 7nm$ and                                                                                                                                                                                                                                                                                           |

|      | length of $1\mu m$ , $0.05\mu m$ and $0.04\mu m$ . $V_D = 1V, V_S = 0V, I_B = 0A$ . 112                                                                                                                                                                                                                                                                                                                                                                                                                           |

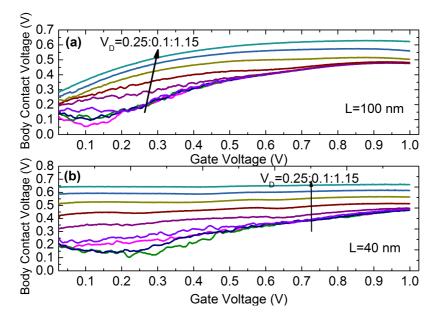

| 5.13 | Body-voltage as a function of the gate voltage for different drain biases: (a) 100nm gate-length device, (b) 40nm gate-length device. $V_S = 0V, I_B = 0A$ . $EOT = 3nm, t_{Si} = 26nm$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

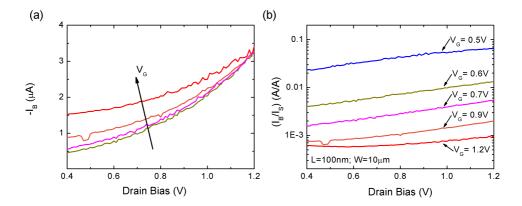

| 5.14 | (a) Experimental body-contact current, and (b) impact ionization ratio $(M-1)$ as a function of the drain bias, obtained from direct body current monitoring at different inversion levels $(V_G)$ . $EOT=3nm,L=100nm,W=10\mu m,t_{BOX}=10nm.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

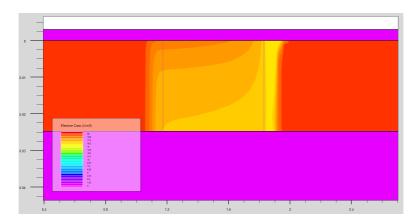

| 5.15 | Cross-sectioned TB SOI transistor where the electron concentration is obtained from numerical simulations. $EOT=3nm,T_{si}=26nm,L=100nm,W=10\mu m,t_{BOX}=10nm,V_D=1.2V,V_G=0.7V.$ . 11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.16 | Output drain current characteristics and impact ionization ratio on a SOI-MOSFET with $L=200nm$ and $W=10.1\mu m$ for different substrate biases when the body-contact is kept under zero-current condition $(I_B=0)$ : (a & c) ultra-thin body device $t_{Si}=7nm$ , (b & d) thin body device $t_{Si}=26nm$ . (c) and (d) have been extracted at $V_D=2.8V$                                                                                                                                                                                                                                                                                                                                                                        |

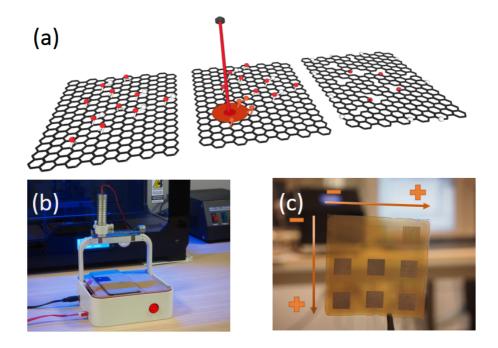

| A.1  | (a) Illustration of GO reduction with laser diode irradiation according to the Lerf-Klinowski model. Before graphene oxide thermal reduction, there is a large amount of functional hydroxyl (C-OH) and epoxyl (C-O-C) groups (left). The functional groups are broken during the reduction process (center) for obtaining the partial restoration of the graphene layers although some defects remain in the structure (right). (b) Image of the experimental setup based on a numerical control unit with interchangeable laser head. (c) An example of $1cm \times 1cm$ rGO samples on a PET substrate reduced at increasing laser power intensities, from 65mW to 105mW with an increment of 5mW in the direction of the arrows |

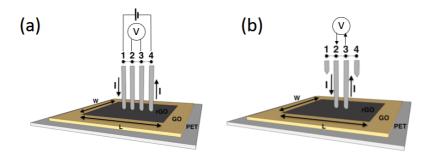

| A.2  | (a) Four point-contact setup, current $I$ is forced between probes 1 and 4 by applying a constant bias $V_{1-4}$ while the voltage drop is measured between probes 2 and 3. (b) Two point-contact setup, current $I$ and voltage $V$ are simultaneously applied and measured through the same probes $(2 \text{ and } 3), \ldots, 12$                                                                                                                                                                                                                                                                                                                                                                                               |

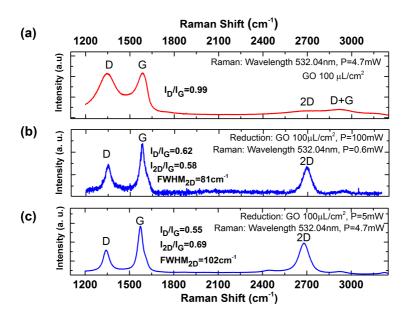

| A.3 | Raman spectra of different samples on PET substrates: (a) GO before reduction, (b) Reduced-GO at a laser power of 100mW $(\lambda = 550nm)$ at an excursion rate of $1min/cm^2$ , (c) Reduced-GO at a laser power of $4.7\text{mW}$ $(\lambda = 788nm)$ at an excursion rate of $24min/cm^2$                                                                                                                                                                                                                                                                                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

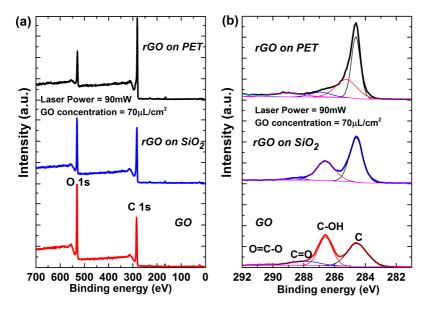

| A.4 | XPS spectra for graphene oxide and reduced graphene oxide on PET and $SiO_2$ substrates: (a) comparison of wide spectra, (b) comparison of C1s peaks. The initial GO concentration before water evaporation was $70\mu L/cm^2$ ; the laser power, $90mW$ ( $1cm^2/min$ ). 130                                                                                                                                                                                                                                                                                                                                             |

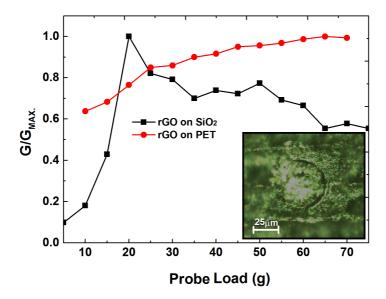

| A.5 | Relative conductance extracted by successive 2PC measurements and direct $WC$ contact as a function of the probe load for rGO reduced on PET and $SiO_2$ substrates. Inset: Microscope image of the probe crater generated by the probe                                                                                                                                                                                                                                                                                                                                                                                   |

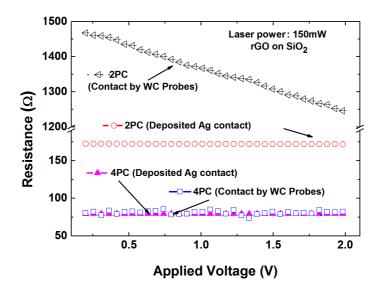

| A.6 | Comparison of resistance extracted from 4 and 2 point-contact measurements combining direct contact of the rGO surface with the $WC$ probes and deposited $Ag$ contacts                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

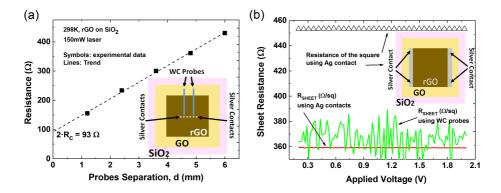

| A.7 | (a) Example of contact resistance extraction for $Ag$ deposited contacts by extrapolation of the 2 point-contact resistance at $d=0$ . The residual contact resistance is relatively low compared to that of direct $WC$ contacts, explaining the differences observed in Fig. A.6. (b) Sheet resistance as a function of applied voltage for $1cm \times 1cm$ reduced graphene oxide sample on $SiO_2$ substrate with $Ag$ deposited contacts covering opposite edges of the sample (open symbols), and 4PC measurements with direct contact of the WC probes on the rGO surface and through silver contacts (lines) 134 |

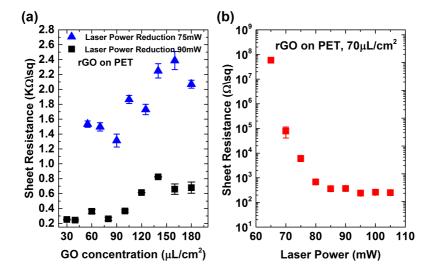

| A.8 | (a) Sheet resistance extracted using 4PC method for $1cm \times 1cm$ samples with different initial graphene concentration (before water evaporation) for two different laser powers. (b) Sheet resistance of the rGO obtained with a initial surface concentration of colloid of $70\mu L/cm^2$ as a function of the laser power ( $\lambda = 550nm$ ). Laser power above 120mW can compromise the integrity of the PET substrate at a laser excursion speed of $1cm^2/min$                                                                                                                                              |

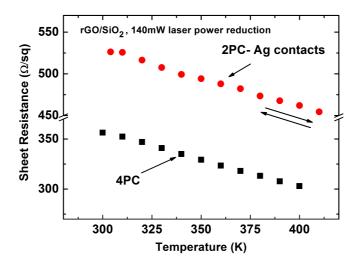

| A.9  | Sheet resistance $(\rho_s)$ as a function of temperature in two point-  |     |

|------|-------------------------------------------------------------------------|-----|

|      | contact (2PC) and four point-contact (4PC) configurations. For          |     |

|      | the first case, the contact is carried out through deposited $Ag$ elec- |     |

|      | trodes covering two opposite edges of the sample, whereas for the       |     |

|      | 4PC case the contact is done with the $WC$ probes on $Ag$ deposited     |     |

|      | electrodes                                                              | 137 |

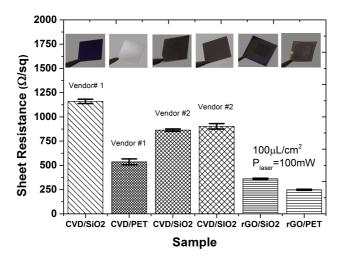

| A.10 | Comparison of the sheet resistance, $\rho_s$ , extracted by 4PC method  |     |

|      | from CVD graphene on PET and $SiO_2$ substrates acquired from           |     |

|      | commercial channels and optimized rGO samples. Characteriza-            |     |

|      | tion of two CVD samples on $SiO_2$ from the same vendor (Vendor         |     |

|      | 2) reflects the variability of the commercial samples                   | 138 |

## List of Tables

| 1.1 | Comparison of the effect of scaling on MOSFET device parameters. |

|-----|------------------------------------------------------------------|

|     | $\alpha$ is the scaling factor                                   |

| 5.1 | Ionization coefficients                                          |

# Prologue

## Context

Since the MOSFET transistor was demonstrated in 1959 [1] and after Gordon Moore well determined in the 1960's with his 'Moore's law' [2], the semiconductor industry trend has been the miniaturization (reduction the device size) with the goal of increasing the number of devices per chip and improving the switching frequency. Consequently, the voltages are reduced in proportion to the dimension in order to keep the electric fields constant. Regrettably, huge technology difficulties have been found to follow some of the 'scaling rules' needed in the transistor miniaturization, however, the way to solve the majority of them has also been found.

One of the ways to increase the device performance is reducing the thickness of the silicon oxide insulator. Silicon dioxide  $(SiO_2)$  has been the preferred gate insulator for silicon MOSFET since its very beginning in the 1960's due to the easiness to grow controlled  $SiO_2$  thin layers on Si films. The oxide thickness has been reduced over the years from 300nm, for  $10\mu$ m technology, to 1.2nm, for 65nm technology [3]. In these latter thicknesses, the electric filed in the oxide becomes very high causing current leakage through the insulator and even destructive breakdown of the oxide [4]. Moreover, tunneling leakage current appears in  $SiO_2$  films thinner than 1.5nm, doing the device inoperative [5]. To solve this issue while following the scale trend, materials having larger dielectric constants (high-k dielectrics) have been proposed to replace the  $SiO_2$  [6]. These high- $\kappa$  dielectric insulators allow thicker films while keeping the same gate capacitance according to Equation 1:

$$C = \frac{\kappa \epsilon_0 A}{t_{or}} \tag{1}$$

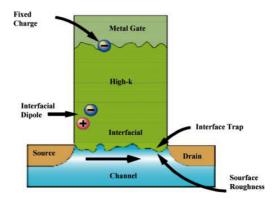

where  $\kappa$  is the relative dielectric constant of the material,  $\epsilon_0$  is the permittivity of free space, A the capacitor area and  $t_{ox}$  the thickness of the insulator. However, adopting high- $\kappa$  dielectrics in integrated circuits (ICs) introduces chemical reactions between them and the silicon substrate, as well as lower surface mobility than the in  $Si/SiO_2$  structure [7]. These issues can be minimized by inserting a thin  $SiO_2$  interfacial layer between the silicon substrate and the high- $\kappa$  dielectric and using a metal gate instead of a poly-Si gate [7]. Despite the improvements introduced, new effects and instabilities such as interface trapping, oxide mobile charges or random telegraph noise (RTN), come into action due to the increase in the number of interfaces, the quality of them, and the properties of the new material introduced. These reliability issues make necessary an extensive characterization of the transistor behavior under different bias conditions.

On the other hand, the randomness in the position of dopant atoms in the device is an inherent source of fluctuations as the dimensions shrink. This effect in the depleted layer under the channel causes fluctuations (variability) in the threshold voltage of the transistors from device to device [8]. Voltages must overcome these fluctuations intrinsic to fabrication process and cannot be reduced as desired. These voltage limitations imply high electric fields in the transistor which triggers new instability effects such as hot carrier degradation, negative bias instability (NBTI) or impact ionization, among others.

The extreme scaling down in the length of transistors to nanometer ranges and the difficulties involved in the manufacturing process, have originated the arising of new structures and materials to fabricate the transistors. The increase of extrinsic parasitic resistances and capacitances caused by the scaling of the transistor is relieved by reducing the parasitic junction capacitance [9]. The Silicon-on-Insulator (SOI) technology, with the integration of an ultra-thin buried oxide (BOX), improves the threshold voltage variability [10]. Besides, this buried oxide layer eliminates the need to add dopants to the channel, thus making it fully depleted, (FDSOI). Other technologies adopted are the ultra-thin body FETs and vertical transistor structures which use a double gate structure such as the FinFET [11].

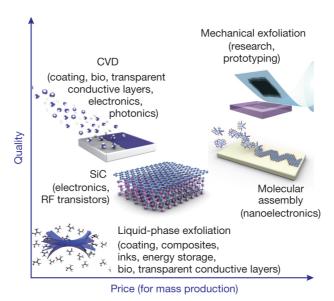

Finally, there has been a recent trend to investigate the role of new materials in electronics applications in general, leaded by two dimensional (2D) semiconductors such as graphene [12] or transition metal dichalcogenides (TMDs) [13].

These materials hold stunning electrical properties in very thin scales and are being investigated to be incorporated in future technology nodes.

To sum up, this work studies the impact of the miniaturization on the transistor through the characterization of reliability effects. The instability effect involved in new process schemes and materials associated to gate (NBTI, RTN, impact ionization, etc.) will be the main focus of this thesis. Moreover, electrical characterization and synthesis of new electronic 2D materials have been carried out.

## Outline

The structure of the work is described as follows:

Chapter 1. MOSFET Scaling. This chapter focuses on the study of the transistor structures and technologies proposed to achieve the goals imposed by technology miniaturization. These technologies are the Silicon-on-Insulator, the use of high- $\kappa$  insulator as gate oxide and the gate stack structure. The two dimensional (2D) materials proposed in the next technologies nodes are analyzed and the reliability effects concerning all these technology improvements are summarized.

Chapter 2. Experimental Characterization. This chapter introduces the experimental techniques and the theoretical framework which allow to carry out the electrical characterization of reliability issues in semiconductor devices. The techniques used for electrical characterization of bare SOI wafers, and the defects located in the oxide-Si interfaces of these devices are described. The substrate bias dependence of the threshold voltage, the sources of instability and the noise characterization of SOI transistors are detailed. Additionally, the characterization of wafer variability through automatic measurement setups is explained in this chapter. Finally, The characterization techniques to extract the sheet resistance and contact resistivity of 2D materials (both bare substrates and metallized substrates) are detailed.

Chapter 3. Bias Instability. This chapter is focused on the reliability issues affecting the electrical characteristics of a MOS transistor when the gate is stressed with relatively high voltage (Bias Instability). In this chapter, the instability of bare SOI wafers is characterized by using the Pseudo-MOSFET

technique. The effect of positive and negative stress pulses on the properties of both hole and electron channels is systematically investigated using several characterization methods. The origin of the instability, the dependence of the degradation with time, and the recovery after the stress are discussed.

Chapter 4. Random Telegraph Noise. In this chapter Random Telegraph Noise (RTN) has been studied in ultra-thin SOI MOSFETs. A new experimental characterization protocol which aims to identify unequivocally the single-trap RTN signals in optimum bias conditions is introduced. The methodology combines a modified Weighted Time Lag Plot algorithm assisted with 1/f spectral scanning by gate bias. The procedure has been applied to study the influence of the back-gate bias on the RTN characteristics of the SOI devices with coupled front and back interfaces. The effect of the temperature on the characteristic times has been studied in the range from 248 to 323 K validating the results obtained at room temperature.

Chapter 5. Impact Ionization. This chapter faces the study of impact ionization in Silicon-On-Insulator transistors from the direct characterization of the body current and electrostatic potential. Thin and ultra-thin body-contacted silicon-on-insulator transistors have been fabricated for that purpose, and biased at zero-body potential and zero-body current conditions. The influence of the channel length on the evolution of the body potential as well as the substrate bias dependence are analyzed.

Chapter 6. Conclusions. This chapter faces the main ideas extracted from the thesis, from the theoretical to the experimental achievements. The future steps are also shown in this chapter.

Appendix A. Electrical characterization of laser rGO This appendix is focused on the electrical characterization of laser-assisted reduced graphene oxide by point contact techniques. The careful investigation of in-line two and four point-contact techniques applied to macroscopic samples of reduced graphene oxide is carried out. Then, the application of the characterization technique to improve the conductivity of the samples is shown.

# Chapter 1

# MOSFET Scaling

The scaling of the dimensions of a MOSFET and the consequent performance improvement of the transistors have been shocking during the last four decades, since Dennar et al. described the MOSFET scaling rules in 1974 [14]. Starting at a minimum feature length of 10 mm in 1970, the gate length was gradually reduced to a feature size of decades of nanometers in the last years. Proper scaling of MOSFET, however, requires not only a size reduction of the gate length and width but also a reduction of all other dimensions including the gate/source and gate/drain alignment, the oxide thickness and the depletion layer widths. The 'scaling rules' of MOSFET device parameters are illustrated in the Table 1.1.