## **WOCSDICE 2012**

# Study of the Gate Capacitance of GaAs, InAs and InGaAs Nanowires

E. González-Marín, F. G. Ruiz\*, I. M. Tienda-Luna, A. Godoy and F. Gámiz

Dpto. Electrónica y Tecnología de Computadores, Facultad de Ciencias, Universidad de Granada. Av. Fuentenueva S/N, 18071 – Granada, Spain.

\*E-mail: franruiz@ugr.es

#### **ABSTRACT**

In this work, a simulation-based study of the gate capacitance of III-V nanowires is performed by using a 2D Schrödinger-Poisson solver. The effective mass approximation, including non-parabolic corrections, is used to model the semiconductor conduction band. Also, wave-function penetration into the gate dielectric is considered. We assess the impact of parameters such as the gate-insulator effective mass and the satellite conduction band valleys energy offsets.

#### 1. INTRODUCTION

The combination of both, nanowire (NW) architectures and III-V semiconductor materials are among the most promising candidates for future technology nodes. The reduction of the Short-Channel Effects (SCEs) provided by NWs and the higher electron mobility achieved with III-V compounds may allow a further integration density while increasing the device performance [1]. However, the low conduction effective mass (m\*) of III-V semiconductors (particularly that associated to their  $\Gamma$ valley), which is the reason of the higher electron mobility, is also related to one of the main limitations of these III-V-based devices: the decrease of the inversionlayer capacitance [2]. In this work, the gate capacitance (C<sub>G</sub>) of NWs with GaAs, InAs and In<sub>x</sub>Ga<sub>1-x</sub>As compounds is studied by means of numerical simulations. In the following, x=0.53 is employed for the ternary semiconductor, InGaAs.

## 2. SIMULATOR AND DEVICES DESCRIPTION

The electrostatic behavior of long-channel NWs is calculated by solving the 2D Schrödinger-Poisson equations in a cross-section, which provides us with the subband structure of the conduction band (CB). The effective mass approximation (EMA) is used to model the three kinds of valleys  $(\Gamma, X \text{ and } \Lambda)$  of the CB. Table I shows the parameters used in this work, achieved from [3] and [4], to model each valley. Due to the high value of the non-parabolic parameters, especially for the  $\Gamma$ valley  $\alpha_{\Gamma} \approx 1 eV^{-1}$ , the inclusion of non-parabolic corrections is needed to achieve accurate results [5]. To do so, we have followed the method proposed in [6]. Finally, wave-function  $(\Psi)$  penetration into the gateinsulator is allowed by introducing as additional boundary conditions the continuity of  $\Psi$  and  $M^{-1}\nabla \Psi$  at the semiconductor-insulator interface, where M is the effective mass tensor in the confinement plane. The second boundary condition needs the effective mass of the gate-insulator, for which uneven values are found in the literature [7,8].

|                                                                   | GaAs [3]/[4]  | InGaAs [3]/[4] | InAs [3]/[4]  |

|-------------------------------------------------------------------|---------------|----------------|---------------|

| E <sub>Γ</sub> (eV)                                               | 1.518 / 1.519 | 0.730 / 0.830  | 0.416 / 0.417 |

| E <sub>L</sub> (eV)                                               | 2.003 / 1.981 | 1.480 / 1.182  | 1.140 / 1.133 |

| E <sub>X</sub> (eV)                                               | 1.812 / 1.815 | 1.980 / 1.563  | 1.477 / 1.433 |

| $\mathbf{m}_{\Gamma}$ ( $\mathbf{m}_{0}$ )                        | 0.082 / 0.067 | 0.045 / 0.052  | 0.026 / 0.026 |

| $m_{Ll}(m_0)$                                                     | 1.610 / 1.900 | 1.232 / 1.661  | 1.707 / 0.640 |

| $\mathbf{m}_{\mathrm{Lt}} \left( \mathbf{m}_{\mathrm{0}} \right)$ | 0.126 / 0.075 | 0.061 / 0.115  | 0.106 / 0.050 |

| $\mathbf{m}_{\mathrm{XI}}\left(\mathbf{m}_{\mathrm{0}}\right)$    | 1.705 / 1.300 | 1.209 / 4.553  | 7.079 / 1.130 |

| $\mathbf{m}_{\mathbf{X}\mathbf{t}} (\mathbf{m}_{0})$              | 0.236 / 0.230 | 0.193 / 0.233  | 0.232 / 0.160 |

Table I. III-V semiconductor parameters.

#### 3. RESULTS

Cylindrical NWs oriented along the [100] direction have been simulated. Semiconductor diameters range from 5nm to 15nm. Al $_2$ O $_3$  is considered as gate insulator (dielectric constant  $\epsilon_r = 9\epsilon_0$ ), with a constant insulator thickness of  $T_{ins}$ =2nm. A metallic gate with work function  $\Phi_m$ =5.05eV is used. No interface charge is included in the simulations.

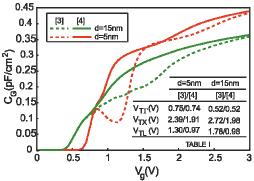

First, the influence of simulation conditions is studied. InGaAs NWs have been simulated with the two different sets of parameters shown in Table I. The resulting C<sub>G</sub>-V<sub>G</sub> curve is shown in Fig. 1, including  $V_{T\Gamma}$ ,  $V_{TL}$  and  $V_{TX}$ , defined as the  $\Gamma$ , L and X valleys threshold voltage, respectively. The lower the gap of a valley, the lower its threshold voltage: thus,  $V_{T\Gamma}$  coincides with the device threshold voltage (V<sub>T</sub>). The C<sub>G</sub> values achieved for both sets of parameters are quite similar in the range between  $V_{TT}$  and  $V_{TL}$ . However, for  $V_G > V_{TL}$  the population of the satellite valleys increases and, due to their higher m\*, their contribution to C<sub>G</sub> becomes more and more significant. Therefore, the considered value for the  $\Gamma$ -L valleys gap clearly influences the C<sub>G</sub> curve, as shown in Fig. 1, where a hump is observed where the satellite valleys are activated. When the parameters from [4] are considered, a shoulder is observed near V<sub>TL</sub> (V<sub>G</sub>≈0.7V), which is associated to an increase of the L valley population. On the other hand, when the second set of parameters is taken into account (from ref. [3]), the shoulder appears at higher gate voltages (V<sub>G</sub>≈1.5V for d=15nm, V<sub>G</sub>≈1.2V for d=5nm), as expected from the larger difference between  $E_{g\Gamma}$  and  $E_{gL}$ . In the following, parameters from [3] will be used.

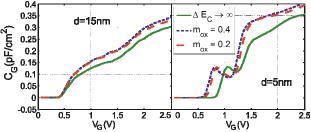

A second simulation-related effect that can modify the calculated  $C_G$  behavior is the inclusion of wave function penetration into the gate insulator (see Fig. 2). Assuming an infinite potential barrier in the insulator, the minimum energy of the  $\Gamma$  valley subbands is raised, increasing  $V_{T\Gamma}$ . Moreover, the infinite barrier potential approximation underestimates  $C_G$ : the charge density is pushed away from the gate insulator, increasing the inversion layer centroid and thus reducing the inversion capacitance [9].

Fig. 1.  $C_G$  for 5nm and 15nm diameter InGaAs NWs. Two sets of material parameters, achieved from [3] and [4], are used.

An additional consideration to take into account when allowing the wave function penetration into the gate dielectric is the effective mass of the insulator. Fig. 2 includes a comparison for two different values of  $m_{ox}$  [7,8]: the larger  $m_{ox}$ , the lower  $V_{TT}$ , and the higher the difference with the infinite potential barrier. These effects are more noticeable for smaller NWs.

When comparing the  $C_G$  of InAs, InGaAs and GaAs NWs, there are several effects that determine their behavior:

- i. A reduction of the threshold voltage can be expected when the In molar fraction in the  $In_xGa_{1-x}As$  compound increases, due to the grow of the semiconductor electron affinity  $(\chi_s)$ .

- ii. The lower the confinement effective mass for the  $\Gamma$  valley, the higher the energy separation from the conduction band minimum. Again, as shown in Table I, a higher In content in the  $In_xGa_{1-x}As$  compound implies a lower  $\Gamma$  valley effective mass.

- iii. The wave function penetration into the gate insulator is especially relevant for large  $m_{ox}$ – $m_s$  discontinuities. Therefore, it has a greater impact on smaller effective mass semiconductors (i.e., InAs), adding up to the previous effects.

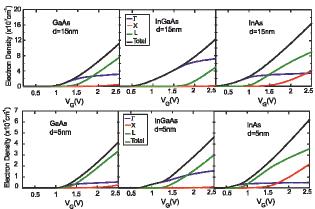

Figure 3 shows the electron density per unit length  $(N_t)$  as a function of  $V_G$  for NWs with the three semiconductors considered and 5nm and 15nm diameters. In the  $V_G$  range between  $V_{T\Gamma}$  and  $V_{TL}$ , the conduction effective mass coincides with the  $\Gamma$  valley mass, thus providing its well-known beneficial effects on the transport properties (high mobility). Moreover, InGaAs devices achieve the highest separation between  $V_{T\Gamma}$  and  $V_{TL}$  for the two device sizes considered. However, and despite the larger value of  $E_L - E_\Gamma$  of InAs,  $V_{TL} - V_{T\Gamma}$  is not as large as it could be expected for this material. The reason may be found in the higher energy separation from the conduction band minimum, due to the lower effective mass. In all the cases, the shrinking of the device sizes reduces  $V_{TL} - V_{T\Gamma}$ , due to the increase on  $V_{T\Gamma}$ .

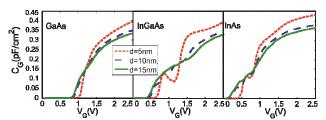

As a drawback, in the same  $V_G$  range where the higher mobility is expected, the so-called density of states bottleneck appears, limiting the gate capacitance (see Fig. 4). The gate capacitance is increased to acceptable values when L valleys get populated, and devices with smaller  $V_{TL}$ – $V_{TT}$  (GaAs) present better  $C_G$ – $V_G$  curves.

Fig. 2.  $C_G$  for InGaAs NWs with 15nm (left) and 5nm (right) diameter, with and without wave function penetration into the insulator

Fig. 3. Electron density per unit length corresponding to 15nm (first row) and 5nm (second row) NWs with GaAs, InGaAs and InAs (left, center and right columns, respectively). Black, blue, green and red lines stand for the total electron density and  $\Gamma$ , L and X valleys, respectively.

Fig. 4.  $C_G$  vs  $V_G$  for GaAs (left), InGaAs (center) and InAs (right), for 5nm, 10nm and 15nm diameter nanowires.

#### 5. ACKNOWLEDGMENT

Work supported by the Spanish Government under projects FIS2008-05805 and FIS2011-26005, and the Junta de Andalucía under project P09-TIC-4873. E. Gonzalez-Marín also acknowledges the FPU program.

### 5. REFERENCES

- [1] J. del Alamo, Nature, 479, 317-323 (2011).

- [2] T. P. O'Regan et al., App. Phys. Let., 99, 163502 (2011).

- [3] J. Kim et al., *J. App. Phys.*, **108**, 013710 (2010).

- [4] Vurgaftman et al., J. App. Phys., 89, 11, 5815 (2001).

- [5] T. P. O'Regan et al., App. Phys. Let., 96, 213514 (2010).

- [6] S. Jin et al., J. App. Phys., 102, 083715(2007).

- [7] S. Meng et al., App. Phys. Let., 83, 4429 (2003).

- [8] T. V. Perevalov et al., Eur. Phys. J. App. Phys., 52, 3 (2010).

- [9] J. B. Roldán et al., *IEEE Trans. Elec. Dev.*, **55**, 1 (2008).