# UNIVERSIDAD DE GRANADA

Ph.D Thesis

## Low-cost soft-error hardened D-Latch in nano CMOS technology

Doctoral Programme in Information and Communication Technologies

Department of Electronic and Computer Technology University of Granada

> Author Seyedehsomayeh Hatefinasab

> Supervisors Noel Rodríguez Encarnación Castillo Morales

Editor: Universidad de Granada. Tesis Doctorales Autor: Seyedehsomayeh Hatefinasab ISBN: 978-84-1195-170-8 URI: <u>https://hdl.handle.net/10481/89398</u>

## Low-cost soft-error hardened D-Latch in nano CMOS technology

by Seyedehsomayeh Hatefinasab Universidad de Granada, Departamentode Electrónica y Tecnología de Computadores

**Palabras clave**: Hardened D-latch; Complementary Metal Oxide Semiconductor technology (CMOS technology); Power-Delay Product (PDP); Soft Error (SE); Single Event Upset (SEU); High Impedance State (HIS); Single Event Transient (SET), Dual Interlocked Storage Cell (DICE), Triple Path DICE (TPDICE), Quadruple-Node Upsets (QNUs), Delay-Power-Area Product (DPAP).

#### Resumen:

En un entorno hostil con una enorme radiación como la del espacio, la parte de memoria de los circuitos electrónicos, como los biestables D puede perder sus valores almacenados y volverse más vulnerable a eventos de alteración de múltiples nodos (multiple node upsets, MNU). Para abordar este problema, los chips integrados de un sistema aeroespacial deben diseñarse con un alto nivel de confiabilidad contra errores leves. Un fallo puede provocar el mal funcionamiento de los módulos o sistemas de un cohete, de una nave espacial o de un satélite en entornos hostiles, poniendo en riesgo estos equipos y vidas humanas. Además, es necesario reducir la tecnología para aumentar la potencia de procesamiento y la densidad de integración, pero al hacerlo, no nos podemos olvidar de seguir manteniendo la confiabilidad de los circuitos; en particular, en los nodos de biestables D a nanoescala se pueden producir errores de alteración de múltiples nodos cuando funcionan en entornos radiactivos hostiles. Por lo tanto, es necesario diseñar módulos de almacenamiento autorecuperables capaces de realizar cálculos altamente confiables en cualquier situación en el espacio exterior. Esta tesis aborda así el diseño de un biestable D tolerante a errores en un nodo, a errores en dos nodos y a errores en cuatro nodos, proponiendo así un nuevo biestable D robusto, de bajo coste, alta confiabilidad y autorrecuperabilidad usando para ello una estrategia de diseño adecuada.

## Low-cost soft-error hardened D-Latch in nano CMOS technology

by Seyedehsomayeh Hatefinasab University of Granada, Department of Electronics and Computer Technology

**Keywords**: Hardened D-latch; Complementary Metal Oxide Semiconductor technology (CMOS technology); Power-Delay Product (PDP); Soft Error (SE); Single Event Upset (SEU); High Impedance State (HIS); Single Event Transient (SET), Dual Interlocked Storage Cell (DICE), Triple Path DICE (TPDICE), Quadruple-Node Upsets (QNUs), Delay-Power-Area Product (DPAP).

#### Abstract:

In a harsh environment with huge radiation as space, the memory part of electronic circuits, such as D-latches, can lose their stored values and become more vulnerable to multiple node upsets (MNUs) events. To tackle this issue, the on-board chips of aerospace system have to be designed with a high-level reliability against soft errors. One failure can cause the malfunction of modules or systems of a rocket, spacecraft, or satellite in harsh environments putting equipment and lives at risk. Also, scaling down the technology is necessary to boost processing power and density of integration, but in doing so keeping the reliability of circuits is a concern that cannot be neglected; in particular, D-latches nodes at nano-scale confront multiple-node upset errors when they are operated in harsh radiative environments. Therefore, it is mandatory to design self-recoverable storage modules capable of highly-reliable computing under any outer space situation. This thesis addresses the design of a single-node-upset, double-node-upset, and quadruple-node-upset tolerant D-Latch, which is a new approach of hardened D-latch featuring low-cost, high-reliability, and self-recoverability under the proper design strategy.

I, Seyedehsomayeh Hatefinasab, as Ph.D. Candidate under the Doctoral Program in Information and Communication Technologies of the University of Granada, I authorize the location of the following copy of the Doctoral Thesis in the library of the center so that can be consulted by people who want it.

Fdo.: Seyedehsomayeh Hatefinasab

Granada, 6th October 2023

D. Noel Rodríguez Santiago, Full Professor of the the Department of Electronics and Computer Technology at the University of Granada.

Dña. **Encarnación Castillo Morales**, Professor Department of Electronics and Computer Technology at the University of Granada.

## Declare:

That the research entitled Low-cost Soft-Error Hardened D-Latch in Nano CMOS Technology has been conducted under our supervision by Mrs. Seyedehsomayeh Hatefinasab, a Ph.D. Candidate enrolled in the Doctoral Program in Information and Communication Technologies at the University of Granada.

Throughout the course of this research, proper acknowledgment has been given to other authors by citing their publications and findings whenever they have been utilized. We grant authorization for the defense of the aforementioned work in front of the appropriate academic tribunal.

This statement is issued and undersigned in Granada, in the month of October 2023.

## The supervisors:

Noel Rodríguez Santiago

Encarnación Castillo Morales

## Acknowledgments

First of all, I would like to thank my directors Noel Rodríguez Santiago and Encarnación Castillo Morales. They give me this opportunity to study PhD and follow my interest research, they help me for publish manuscripts in high h-index journal and introduce me to Granada University team. Also, I should thank a lot of Granada University team for helping me and give me wonderful support. This thesis has been carried out satisfactorily. I would like that too appreciate the advice and guidance of Prof. Diego P. Morales, and Prof. Antonio García and all the components of the Department of Electronics and Computer Techonology of the University of Granada since they have welcomed me as one more and have integrated me into all department activities.

Of course, getting here would have been impossible without the people most important, my family who have helped me who I am today. Thanks to my husband who has supported and advised me in these years. And important part of my life is my new born baby, Evan, he is only the person who doesn't not only at all help me, but also makes a lot of delay to my studying. He is always nagging and crying without any stop. But whole of motivation and energy comes from his present. Specially, when I want to check him and I raise my head to see what he is doing and suddenly I notice his look that he is looking at me and after we make eye contact, he smiles at me. I always keep telling to my husband, Evan is my best achievement in our life. Because of him, I have a lot of pleasure in my life, so with whole of my heart I give this thesis to my son. Take it hamstero!

Thanks a lot, to my mother, brother and sisters, even from long distance our heart are connected to each other.

## Contents

| Part I. Introduction                                                       | 1  |

|----------------------------------------------------------------------------|----|

| Introduction                                                               | 3  |

| 1.1 Objectives                                                             | 5  |

| 1.2 Thesis outline                                                         | 5  |

| Bibliography                                                               | 6  |

| Materials and Methods                                                      | 9  |

| 2.1 Soft error                                                             | 9  |

| 2.2 Sensitive Regions in Silicon Devices                                   | 10 |

| 2.3 Single Event Transient                                                 | 10 |

| 2.4 Soft Error Mitigation Techniques                                       | 10 |

| 2.4.1 Prevention Techniques                                                | 11 |

| 2.4.2 Recovery Techniques                                                  | 11 |

| 2.5 Methodology                                                            | 12 |

| Bibliography                                                               | 13 |

| Part II. Publications                                                      | 15 |

| Low-Cost Soft Error Robust Hardened D-Latch for CMOS<br>Technology Circuit | 17 |

| 3.1 Introduction                                                           |    |

| 3.2 Previous Work                                                          | 19 |

| 3.3 Proposed D-Latch                                                       | 22 |

| 3.4 Latch Evaluation and Benchmarking                                      | 29 |

| 3.4.1 Power Consumption                                                    | 29 |

| 3.4.2 Delay                                             |

|---------------------------------------------------------|

| 3.4.3 PDP                                               |

| 3.4.4 Temperature Variation                             |

| 3.4.5 Area Usage                                        |

| 3.4.6 Process Variations                                |

| <b>3.5 Conclusions</b>                                  |

| Appendix A                                              |

| References                                              |

| Highly Reliable Quadruple-Node-Upset-Tolerant D-Latch43 |

| <b>4.1 Introduction</b>                                 |

| 4.2 Previous Hardened D-latch46                         |

| 4.2.1 DICE                                              |

| 4.2.2 CLCT                                              |

| 4.2.3 TPDICE-based D-latch                              |

| 4.2.4 LSEDUT D-latch                                    |

| 4.2.5 QNUTL-CG D-latch                                  |

| 4.3 Proposed D-latch                                    |

| 4.3.1 Immunity against SNU                              |

| 4.3.2 Immunity against DNU                              |

| 4.3.3 Immunity against TNU                              |

| 4.3.4 Immunity against QNU                              |

| <b>4.4 Simulation</b>                                   |

| 4.4.1 Reliability comparison                            |

| 4.4.2 Cost comparison                                   |

| 4.4.3 Process variation                                 |

| 4.4.4 PVT variations                                    |

| 4.5 Conclusion71                                        |

| References                                              |

| Rule-Based Design for Low-Cost Double-Node Upset Tol  | lerant |

|-------------------------------------------------------|--------|

| Self-Recoverable D-Latch                              | 77     |

| 5.1 Introduction                                      | 79     |

| 5.2 State of the art: previous hardened latch designs |        |

| 5.2.1 DNCS-SEU tolerant latch                         |        |

| 5.2.2 NTHLTCH                                         |        |

| 5.2.3 TPDICE-based D-latch                            |        |

| 5.2.4 LSEDUT D-latch                                  |        |

| 5.2.5 DNURHL D-latch                                  |        |

| 5.2.6 RDTL D-latch                                    |        |

| 5.4 Simulation results                                |        |

| 5.5 Conclusion                                        |        |

| References                                            |        |

| Part III. Conclusions                                 | 101    |

| Conclusions and future work                           | 103    |

| 6.1 Conclusions                                       | 103    |

| 6.2 Future work                                       |        |

| Acronyms                                              | 107    |

## List of Figures

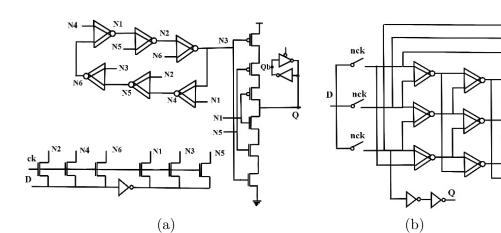

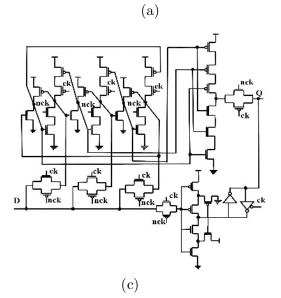

Figure 3.1. (a) Static D-latch schematic; (b) input and output signals of the Static D-Figure 3.2. Proposed D-latch (a) schematic; (b) layout; (c) equivalent schematic Figure 3.3. Test results for SEU injection to nodes when the output is "1" during the holding time; positive SEU injection to "X3" and negative SEU injection to "X2", Figure 3.4. Test results for a positive and negative SEU injections to nodes when the output is "0" during the holding time: (a) to "Q" node; (b) to "X3" node......26 Figure 3.5. Test results when the output is "0" during the holding time: (a) negative and positive SEU injection to "X1" and "X2" nodes, respectively; (b) positive SEU injection to "X4" and "X5" nodes, respectively......27 Figure 3.6. (a) SET pulse filtering capability of the proposed D-latch; (b) maximum pulse width of SET filtered by the proposed D-latch at various supply voltages......28 Figure 3.7. Power consumption of various D-latches: (a) at three frequencies from 1 MHz to 100 MHz and 0.9 V power supply voltage; (b) at three supply voltages and Figure 3.8. Delay of various D-latches: (a) at various frequencies from 1 MHz to 100 MHz and 0.9 V power supply voltage; (b) at three supply voltages and 10 MHz input Figure 3.9. PDP of various D-latches: (a) at various frequencies from 1 MHz to 100 MHz and 0.9 V power supply voltage; (b) at three supply voltages and 10 MHz input Figure 3.10. Temperature variation effect on: (a) delay vs. temperature; (b) power Figure 3.11. (W/L) variation effect on D-latch delay: (a) proposed D-latch; (b) Static D-latch (c) TPDICE-based D-latch (d) DICE (e) LSEH-1 latch (f) delay of D-latches Figure 3.12. (W/L) variation effect on power consumption: (a) proposed D-latch (b) Static D-latch (c) TPDICE-based D-latch (d) DICE (e) LSEH-1 latch (f) power consumption of D-latches with maximum deviation, 0.16, from original W/L value. 35

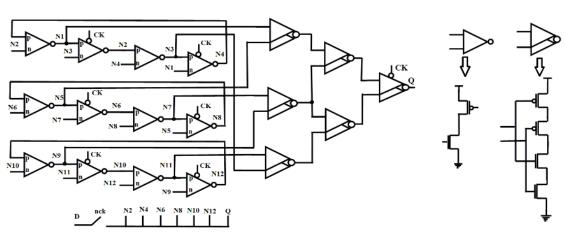

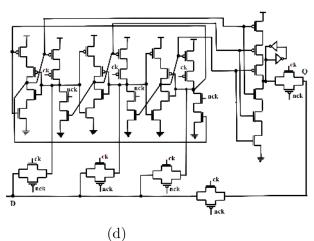

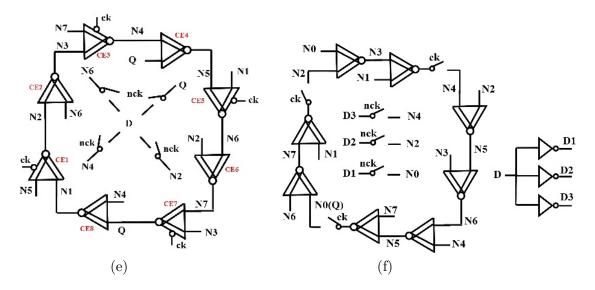

| Figure 4.1. (a) DICE $[26]$ ; (b) CTCL latch $[15]$ ; (c) TPDICE-based D-latch $[27]$ ; (d) |

|---------------------------------------------------------------------------------------------|

| LSEDUT D-latch [25]; (e) QNUTL-CG D-latch [7]                                               |

| Figure 4.2. Proposed D-latch (a) schematic; (b) layout                                      |

| Figure 4.3. (a) SET positive pulse filtering capability of the proposed D-latch; (b)        |

| SET negative pulse filtering capability of the proposed D-latch; (c) maximum pulse          |

| width of SET filtered by the proposed D-latch at various supply voltages56                  |

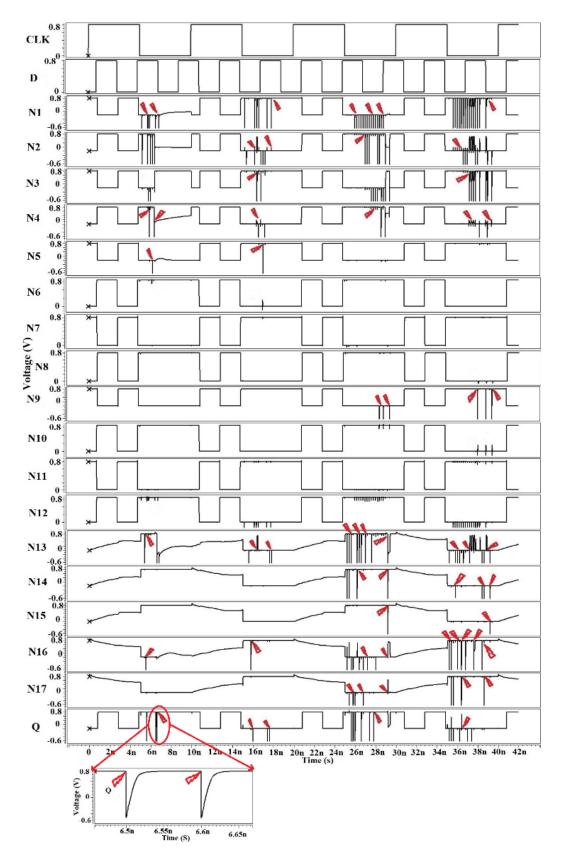

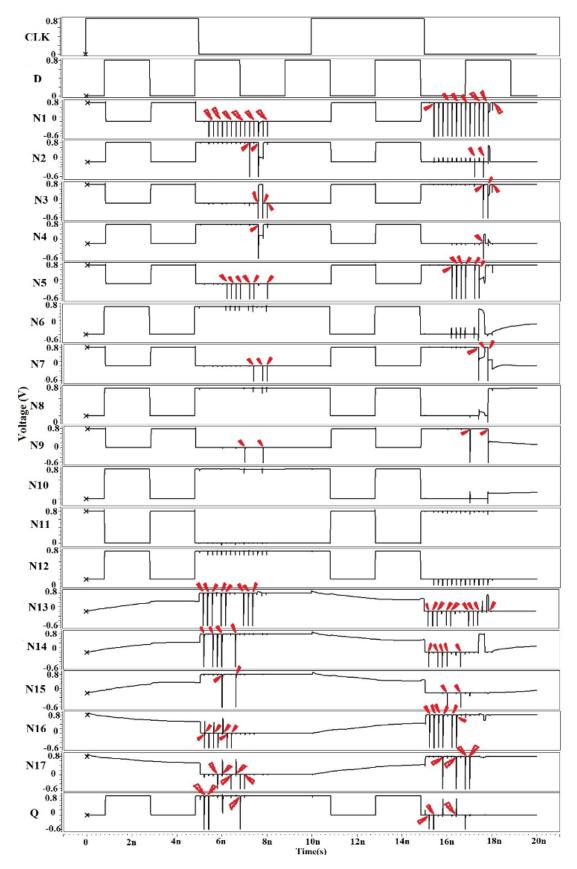

| Figure 4.4. Simulation of the key patterns of SNU, DNU, and TNU injections for the          |

| proposed D-latch                                                                            |

| Figure 4.5. Simulation results of QNUs injected in the proposed D-latch                     |

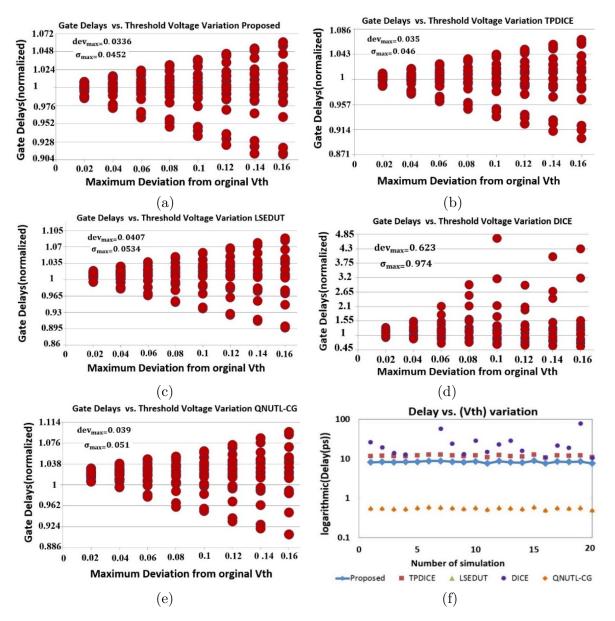

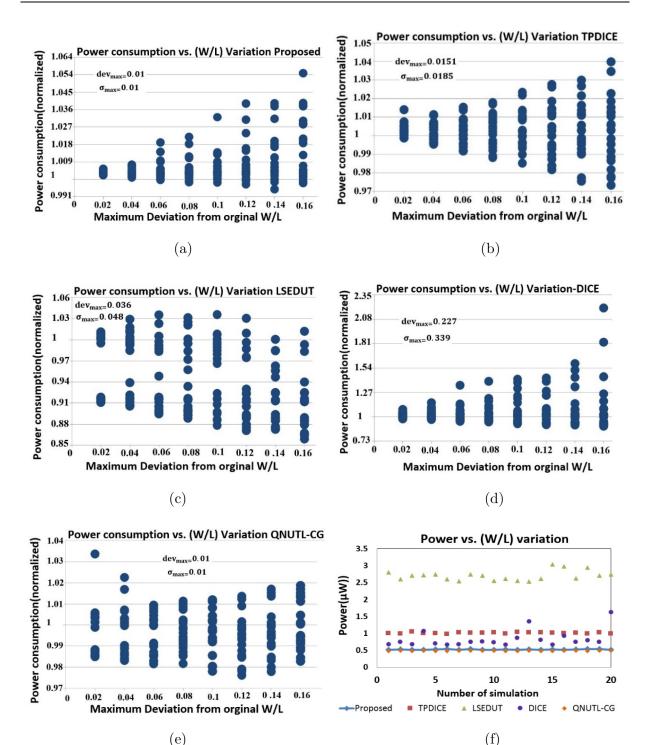

| Figure 4.6. Threshold voltage variation effect on the D-latch delay: (a) proposed D-        |

| latch; (b) TPDICE-based D-latch; (c) LSEDUT latch; (d) DICE; (e) QNUTL-CG                   |

| latch; (f) delay of D-latches with maximum deviation, 0.16, from original threshold         |

| voltage                                                                                     |

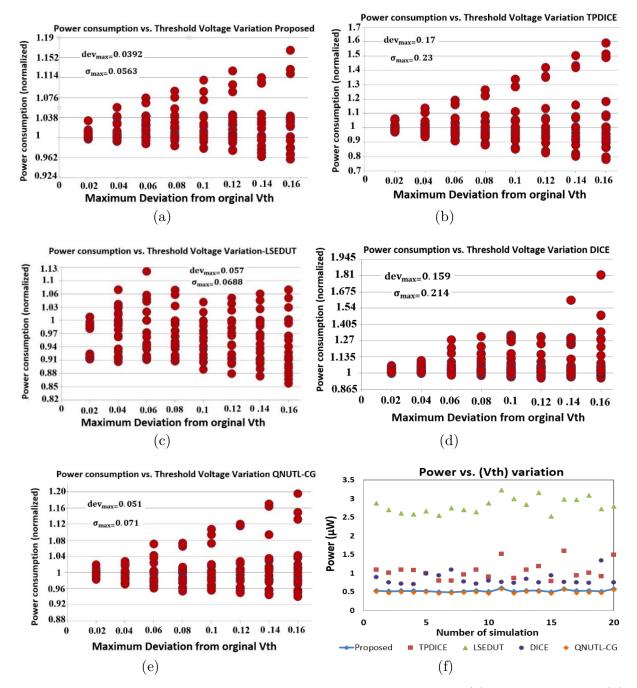

| Figure 4.7. Threshold voltage variation effect on power consumption: (a) proposed D-        |

| latch (b) TPDICE-based D-latch (c) LSEDUT latch (d) DICE (e) QNUTL-CG latch                 |

| (f) power consumption of D-latches with maximum deviation, 0.16, from original              |

| threshold voltage                                                                           |

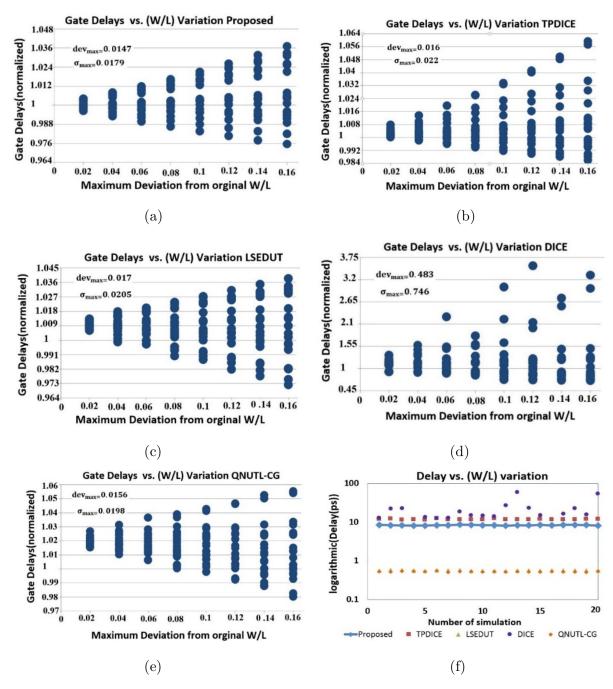

| Figure 4.8. $(W/L)$ variation effect on D-latch delay: (a) proposed D-latch; (b)            |

| TPDICE-based D-latch; (c) LSEDUT latch; (d) DICE; (e) QNUTL-CG latch; (f)                   |

| delay of D-latches with maximum deviation, 0.16, from original W/L67 $$                     |

| Figure 4-9. (W/L) variation effect on power consumption: (a) proposed D-latch; (b)          |

| TPDICE-based D-latch; (c) LSEDUT latch; (d) DICE; (e) QNUTL-CG latch; (f)                   |

| power consumption of D-latches with maximum deviation, 0.16, from original W/L.             |

|                                                                                             |

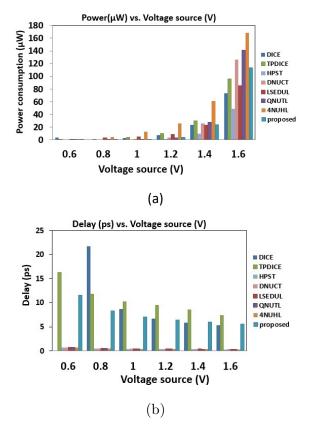

| Figure 4.10. Impact of supply voltage variation on: (a) Power consumption; (b)              |

| delay                                                                                       |

| Figure 4.11. Impacts of temperature variation on: (a) power consumption; (b) delay.         |

|                                                                                             |

|                                                                                             |

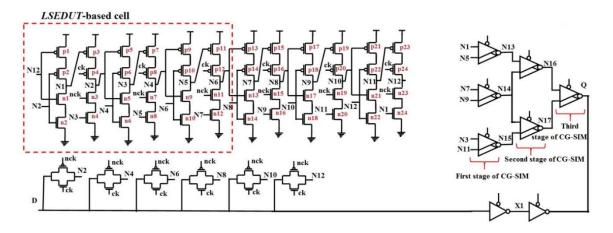

| Figure 5.1. Previous hardened latch designs (a) DNCS-SEU tolerant latch; (b)          |

|---------------------------------------------------------------------------------------|

| NTHLTCH; (c) TPDICE-based latch; (d) LSEDUT latch; (e) DNURHL latch; (f)              |

| RDTL                                                                                  |

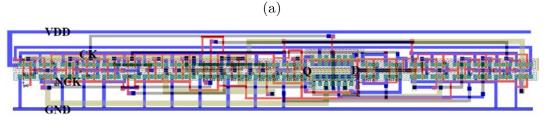

| Figure 5.2. Proposed RB-LDNUR D-latch (a) schematic; (b) layout83                     |

| Figure 5.3. Simulation results of SNU injections to key single nodes of the proposed  |

| RB-LDNUR D-latch                                                                      |

| Figure 5.4. Simulation results of key patterns of DNU injections for the proposed RB- |

| LDNUR latch                                                                           |

| Figure 5.5. Simulation results of DNU injections to pairs related to the output node  |

| (Q) and other internal nodes of the proposed RB-LDNUR latch                           |

| Figure 5.6. Impacts of temperature variation on: (a) delay; (b) power consumption.    |

|                                                                                       |

| Figure 5.7. Impacts of supply voltage variation on: (a) delay; (b) power consumption. |

|                                                                                       |

## List of Tables

| Table 3.1. Classification of different type of D-latch in regard to their soft-error |

|--------------------------------------------------------------------------------------|

| immunity                                                                             |

| Table 3.2. Comparative area of D-latches                                             |

| Table 4.1. Key pattern of SNU, DNU, and TNU injections of the proposed D-latch in    |

| Fig.4.4                                                                              |

| Table 4.2. Key patterns of QNUS injected in the proposed D-latch                     |

| Table 4.3. Immunity against SNU, DNU, TNU, AND QNU, AND his insensitivity,           |

| and SET filtering of the proposed D-latches                                          |

| Table 4.4. Comparative area of D-latches                                             |

| Table 5.1. Key pattern of DNU injections of the proposed RB-LDNUR latch in figure    |

| 5.4                                                                                  |

| Table 5.2. Pattern of DNU injections to pairs with output node (Q) and other nodes   |

| of the proposed RB-LDNUR latch90                                                     |

| Table 5.3. Immunity against SNU, DNU, HIS Insensitivity, and Self-Recoverability of  |

| the proposed RB-LDNUR and previous D-latches                                         |

| Table 5.4. Percentage improvement of DPAP proposed D-latch in comparison with        |

| other D-latches                                                                      |

| Table 5.5. Properties Comparative features of D-latches.    93                       |

## Part I. Introduction

## Chapter 1

## Introduction

In the contemporary era, electronic devices have pervaded all facets of our lives; exemplars include mobile phones, computers, tablets, and the like, with their numbers poised to continuously surge. As technology scales down, it becomes imperative to enhance processing power and integration density. Yet, this progression must be juxtaposed with the imperative of circuit reliability. The downsizing of transistors, integral to scaling, results in the concomitant reduction of node capacitors. In order to uphold electrostatic integrity and manage power dissipation, the supply voltage is reduced. Both these factors augment circuit susceptibility to particle-induced charge. The accumulation of particle-induced charge can instigate transient faults, manifested as single event transients (SETs). Moreover, a single event upset (SEU) may arise from an SET traversing combinational logic circuits and subsequently impinging on sequential circuits, such as flip-flops or latches [1].

The D-latch constitutes a pivotal component of sequential digital systems. The design of VLSI circuits mandates meticulous consideration of various factors for D-latches, encompassing high performance, transistor count, reliability, power-delay, and power-area ratios. The operational frequency of digital circuits is chiefly bounded by the D-latches. Notably, D-latches and clock distribution networks account for a substantial fraction of chip power consumption, while an escalated transistor count results in larger chips or increased manufacturing costs. Given that latches are deployed for data storage, their reliability holds paramount importance across various circuit states, even in the presence of glitches or significant charge injection into internal nodes. This concern has fostered the introduction of novel latch designs commonly known as hardened latches.

Extensive research endeavors have been devoted to the hardening of latches, often achieved by augmenting their basic designs with additional transistors [2-6]. Four categories of hardened latches exist based on their immunity against SEU, SET filtering, and HIS sensitivity. The first category encompasses latches that can tolerate SEU in certain nodes but are not fully SEU-immune; such latches may incur corruption of values following particle strikes. The second category encompasses latches fully tolerant against SEU yet unable to filter SET at their inputs, potentially leading to a high-impedance state at the output node. The third category comprises latches that are fully immune against SEU, devoid of high-impedance states in output nodes, albeit unable to filter input SET. Finally, the fourth category features latches fully immune against SEU, lacking high-impedance states at output nodes, and possessing the ability to filter input SET.

In the design of hardened latches, myriad parameters demand consideration: power consumption, (D-Q) propagation delay, and Power-Delay Product (PDP), immunity against SEU and SET, temperature dependence, process variability, area penalty.

Recent research has placed emphasis on single event double-upset (SEDU), arising from the injection of multiple charges into different internal nodes of latches or flipflops [7-8]. This concern has gained prominence with the advent of nano-scale transistor technology in the sub-nanometer range. Several hardening strategies have been proposed, encompassing node spacing increase, guard rings, multiple-modular redundancy, and well isolation.

The ensuing sections furnish an overview of diverse designs of hardened D-latches, including the subsequent types: Low-Cost and highly Reliable Radiation-hardened latch (LCHR latch), Circuit and Layout Combination Technique latch (CLCT latch), Double Node charge sharing-Soft error interception latch (DNCS-SEI latch), and triple Path DICE latch (TPDICE-based latch).

The LCHR latch employs Schmitt trigger inverters' hysteresis property to filter SET. It utilizes three loops for data retention and SEU tolerance, aligning with the first category of hardening latches previously described [1].

The CLCT latch leverages Clocking-Gate (CG) technology, featuring no active feedback loops within the Dual Interlocked storage Cell (DICE). The transparent mode employs a keeper, rendering it a power-efficient solution. In latching mode, the data of DICE and keeper counteract SEU or SEDU. As DICE and the keeper are linked to a Triple-input Muller C-element (TMCE), the output may adopt a high-impedance state. However, this D-latch is not entirely immune against SEDU [6].

The DNCS-SEI latch is fully SEU-immune, with each triple-input Muller Celement (TMCE) capable of blocking SEU. TMCE can self-recover due to the loop. In cases where SEDU impacts both TMCE inputs and information recovery is not possible, the keeper can prevent a high-impedance state at the output (Q). Additionally, if SEDU affects the loop and the Q node, the latch can remain immune and self-recover. However, this latch cannot filter SET, and its extended loop and greater number of additional transistors contribute to higher power consumption [5].

The TPDICE-based latch is entirely immune against SEDU and SEU, while also capable of filtering SET at the input [8]. It comprises a TPDICE for data storage and a TMCE for SEDU tolerance. A keeper thwarts the output node from entering a high-impedance state, and a Schmitt Trigger Inverter (STI) filters SETs from combinational gates at the preceding stage of the D-latch [8].

### 1.1 Objectives

The main objective of this Doctoral Thesis is to study the behaviour and to develop harden latches required for an emerging nano-electronics nodes. This objective also can be applied for the detailed analysis of the advantages/challenges of using memory cells or flip flops at the forthcoming nanotechnology scale.

The main objective can be split in five specific objectives, with main focus on third and fifth objectives:

- 1. Node sensitivity analysis in D-latches based on subcircuits and transistors.

- 2. Exploration of single node upset (SNUs), double node upset (DNUs), triple node upset (TNUs), quadruple node upset (QNUs) in dynamic D-latch circuits.

- 3. Designing the D-latch to achieve optimum performance over the whole operating states in terms of minimum power dissipation, delay and highly reliable.

- 4. Verify the theoretical analysis by software and available tools.

- 5. Validation of the prototype considering final application requirements in terms of: efficiency, size, reliability against supply voltage and temperature or process variations.

## 1.2 Thesis outline

This thesis is presented as a compendium of articles. The structure of Articles is the following:

• **Publication I**: This publication covers the low-cost hardened SNU with high reliability against of temperature and process variations, such as (W/L) and threshold voltage transistor variability. Also, other previous SNU tolerant D-latch is explained and compered with them.

- **Publication II**: This publication covers QNU tolerant D-latch (HRQNU) with high reliability against process variations, such as threshold voltage and (W/L) transistor variability. Also, this D-latch can mask single event transients in the transparent mode. Also, other previous QNU tolerant D-latch is explained and compered with them.

- **Publication III**: This publication covers a low-cost, self-recoverable, doublenode upset tolerant latch. This D-latch features this character because of rule design combined with other techniques. This design can be used for multiple node upset (MNU) hardened D-latch, such as QNU tolerate D-latch.

## Bibliography

- C. Qi, L. Xiao, J. Guo, T. Wang, "Low cost and highly reliable radiation hardened latch design in 65nm CMOS technology," *Microelectronics Reliability*, 420 vol. 55, no. 6, pp. 863-872, 2015.

- H. Nan, K. Choi, "Novel radiation hardened latch design considering process, voltage and temperature variations for nanoscale CMOS technology," *Microelectron Reliab*, vol. 51, pp. 2086–92, 2011.

- R. Rajaei, M. Tabandeh, M. Fazeli, "Low cost soft error hardened latch designs for nano-scale CMOS technology in presence of process variation," *Microelectron Reliab*, vol. 53, pp. 912–24, 2013.

- [4] R. Rajaei, M. Tabandeh, B. Rashidian, "Single event upset immune latch circuit design using C-element,". In the IEEE ninth international conference on ASIC (ASICON2011), pp. 252–255, 2011.

- [5] K. Katsarou, Y. Tsiatouhas, "Soft error interception latch: double node charge sharing SEU tolerant design," *Electron. Lett.*, vol. 51, no. 4, pp. 330–332, 2015.

- [6] H. Xu, Y. Zheng, "Circuit and layout combination technique to enhance multiple nodes Upset tolerance in Latches," *IEICE Electron Express* vol. 12, no. 9, pp. 1–7, 2015.

- M. Saremi, A. Privat, H.J. Barnaby, et al., "Physically based predictive model for single event transients in CMOS gates," *IEEE Trans. Electron Dev.* vol. 63, no. 6, pp. 2248–2254, 2016.

- [8] A. Yana, Z. Huang, X. Fang, Y. Ouyang, H. Deng, "Single event double-upset fully immune and transient pulse filterable latch design for nanoscale CMOS," *Microelectronics Journal*, vol. 61, pp. 43–50, 2017.

## Chapter 2

## Materials and Methods

#### 2.1 Soft error

An electronic circuit without any hardware problems can face some events resulting in spontaneous single-bit changes in the system without any such failures. This phenomenon in the computer industry is known as a "soft fail". Accruing a soft error in the hardware system does not mean that it features less reliability because the soft fail is completely random. These soft fails can be from well-known electronic noise sources such as power supply fluctuations, lightning, and electrostatic discharge (ESD) [1], or the thermal radiation from the galaxy, such as radiation-emitting stars and atmospheric gases. A soft or non-permanent fault is a non-destructive fault and falls into two categories [2]:

- 1. Transient faults [3], caused by environmental conditions like temperature, voltage, power supply, vibrations, fluctuations, electromagnetic, interference, ground loops, cosmic rays and alpha particles. However, by applying enhanced design and manufacturing technology, non-environmental conditions may not affect nano-technology semiconductor reliability. Meanwhile, the errors caused by cosmic rays, and alpha particles remain a dominant factor causing errors in electronic systems.

- 2. Intermittent faults caused by non-environmental conditions like loose connections, aging components, critical timing, power supply noise, resistive or capacitive variations or couplings, and noise in the system.

As the soft errors in digital electronics, such as electronic anomalies are random in the monitoring equipment. Recent Soft Error Rate (SER) testing results for SRAMbased FPGAs shows a significant risk of functional failures due to the corruption of configuration data, especially when the system has higher densities [4]. It is expected that neutron induced soft errors will get worse by a factor of two as we move from 130nm to 90nm technology. Radiation induced soft errors have become one of the most important and challenging failure mechanisms in modern electronic devices. Therefore, SER of commercial chips is considered and classified in four-phase approach [5]:

- 1. Methods to protect chips from soft errors (prevention).

- 2. Methods to detect soft errors (testing).

- 3. Methods to estimate the impact of soft errors (assessment).

- 4. Methods to recover from soft errors (recovery).

#### 2.2 Sensitive Regions in Silicon Devices

A SET can be generated by charges from a single particle (proton or heavy ion) passing through a sensitive node in the circuit [6]. SET in linear devices differs significantly from other types of single event effects (SEE) like SEU in a memory. A SET features the unique characteristics like polarity, waveform, amplitude, duration, which depend on particle impact location, particle energy, device technology, device supply voltage and output load. The junction area of CMOS transistor during "off" state are most sensitive area to struck SEU from a heavy ion particles. When these particles hit the silicon bulk, minority carriers are created and, if collected by the source/drain diffusion regions, a change in the voltage value of the signal node can happen [7].

A particle can induce SEU when it strikes at the channel region of an nMOS transistor during "off" state or the drain region of a pMOS transistor during "off" state. The ionization induces a current pulse in a p-n junction. In the other words, when the charge injected in the form of the current pulse at a sensitive node, which are more than a critical charge  $(Q_{crit})$ , a SET is generated at this junction.

#### 2.3 Single Event Transient

A SET is produced after a high-energy ionizing particle strikes a silicon device near a sensitive node [8]. The transient charge collected from the radiation event produces a current pulse at the junction. If enough charge is collected by a node, the logic state of the silicon device may change.

#### 2.4 Soft Error Mitigation Techniques

Soft error-tolerant design techniques can be classified into two types: prevention and recovery. The methods to protect microchips from soft errors are the prevention methods [9], which are applied during chip design and development. The recovery

methods include online recovery mechanisms from soft errors in order to achieve the chip robustness requirement.

### 2.4.1 Prevention Techniques

### a. Purify the Fabrication Material

A significant reduction in the soft error rate of microelectronics can be achieved by eliminating or reducing the sources of radiation. To reduce the alpha particle emission in packaged ICs, high-purity materials and processes are employed, but the SER caused by the high-energy cosmic neutron interactions cannot be easily shielded.

### b. Radiation Hardened Process Technologies

An SER parameter can be significantly improved by a process technology that increases the critical charge (Qcrit) [10]. One approach is applying additional well isolation (triple-well or guard-ring structure) to reduce the amount of charge collected by creating potential barriers.

### 2.4.2 Recovery Techniques

Fault-tolerant computing methods are considered in this method. Online testing techniques are frequently used as recovery solutions for soft error mitigation.

#### a. Redundancy

The basic idea of redundancy design is to gain higher system reliability by sacrificing the minimality of time or space, or both. The classic triple modular redundancy (TMR) with a majority voter is the common technique in this method. Mitra et al. [11] combine a self-checking design with time redundancy based on the C-element gate to compare two samples of the output signal from a combinational circuit. The C-element can eliminate glitches at combinational outputs. Space and time redundancy are often combined to meet high fault-tolerance requirements with reduced hardware overhead, such as duplication and comparison instead of TMR.

## b. Error-Correcting Code and Parity

Memories are one of the most important parts of modern systems. Because of the high density of storage cells, a large memory is more sensitive to ionizing particles than logic gates. A simple solution for protecting a memory is adding parity bits to each memory word.

During the write operation of a memory, a parity generator computes parity bits for the data to be written. The parity bits are written into memory along with the data. If a particle strike alters the state of a single bit of a memory word, now including the parity bits, the error can be discovered by checking the parity code during the read operation. Depending on the number of parity bits used, this scheme can detect errors, and correct them as well. Such schemes are often combined with system-level approaches for error recovery [12]. In most situations, however, the error recovery in memory is more complex so protection of the memory through codes like error correcting code (ECC) is preferable.

Based on the investment done, the best way to protect memory part is Redundancy technique, which is more reliable and has less penalty. Therefore, this thesis is based on this technique. In the following, the Methodology of this thesis with details is presented.

## 2.5 Methodology

A detailed explanation of the objectives and how to be achieved are presented below.

1. Node sensitivity analysis in D-latch

This objective addresses the technique to identify the sensitive node of D-latches and the analysis of the SEU sensitivity of these nodes, also including the application of node analysis information for selective node hardening techniques. One of the ways to reduce the node sensitivity to SEU are the selective harden nodes (SHN). The SNH technique is based on the transistor scaling of the logic gates associated with the sensitive nodes. Unlike other hardening techniques (i.e., TMR, DICE, etc.) which are coupled with large area overhead and more propagation delays, the proposed selective node hardening does not result in a large area overhead because it only targets the PMOS channel widths  $W_p$  of the logic gates closely connected to the more vulnerable node.

2. Exploration of SEUs, DNUs, TNUs, QNUs in dynamic d-latch circuits

The analysis of SEU, DNU, TNU, QNU effect in dynamic latches has not been explored in detail so far. Current SEU analysis on dynamic latches or node stored charged with feedback should be comprehensively addressed. In this sense, a new SEU analysis approach is expected to be developed.

3. Designing the D-latch to achieve optimum performance over the whole operating states in terms of minimum power dissipation

Designing harden D-latches needs extra transistors in simple latches. This strategy introduces area and power consumption penalty in the circuit. In this regard, within this objective, the development of a new structure of harden D-latch will be targeted in order to outperform the existing alternatives by stablishing a better trade off of area and power consumption.

4. Verify the theoretical analysis by software.

All previous discussed items should be verified based on a software demonstrator. Taking into account the previous designs and comparing them to the new design, the advantages will be displayed with the support of numerical simulations.

5. Validation of the prototype considering final application requirements in terms of: efficiency, size, process variation reliability, supply voltage and temperature variation reliability, etc.

The main target of this step is to have a practical view of the new design of the Dlatch or harden D-latch and to understand the impact of the real application requirements.

#### Bibliography

- [1] J. M. Kolyer and D. E. Watson, ESD from A to Z: Electrical Discharge. New York: Van Nostrand Reinhold, 1990.

- [2] A. J. van de Goor, Testing Semiconductor Memories: Theory and Practice. Wiley, 1991.

- M. A. Breuer, "Testing for Intermittent Faults in Digital Circuits," *IEEE Trans. Computers*, vol. C-22, no. 3, pp. 241-246, 1973.

- [4] Effects of Neutrons on Programmable Logic: White Paper," Technical report, Actel Corporation, Dec. 2002.

- K. Roy, S. Kundu, R. Galivanche, V. Narayanan, R. Raina, and P. N. Sanda,

"Is the Concern for Soft-Error Overblown?," in *Proc. International Test Conf.* (Panel Discussion), 2005.

- [6] B. G. Rax, A. H. Johnston, and C. I. Lee, "Proton Damage E®ects in Linear Integrated Circuits," *IEEE Trans. Nuclear Science*, vol. 45, no. 6, pp. 2632-2637, 1998.

- [7] M. Omana, G. Papasso, D. Rossi, and C. Metra, "A Model for Transient Fault Propagation, in Combinatorial Logic," in *Proc. 9th IEEE On-Line Testing* Symp., pp. 111-115, 2003.

- [7] R. Baumann, "Soft Errors In Commercial Integration Integrated Circuits," *International Jour. High Speed Electronics and Systems*, vol. 14, no. 2, pp. 299-309, 2004.

- [9] F. Wang and V. D. Agrawal, "Single Event Upset: An Embedded Tutorial," in Proc. 21th International Conference on VLSI Design, Jan. 2008, pp. 429-434.

- [10] Q. Zhou and K. Mohanram, "Gate Sizing to Radiation Harden Combinational Logic," *IEEE Trans. on CAD*, vol. 25, no. 1, pp. 155-166, 2006.

- [11] S. Mitra, Z. Ming, S. Waqas, N. Seifert, B. Gill, and K. S. Kim, "Combinational Logic Soft Error Correction," in *Proc. International Test Conference*, pp. 1-9, 2006.

- [12] M. Nicolaidis, "Design for Soft Error Mitigation," *IEEE Transactions on Device* and Materials Reliability, vol. 5, no. 3, pp. 405-418, 2005.

# Part II. Publications

# Chapter 3

# Low-Cost Soft Error Robust Hardened D-Latch for CMOS Technology Circuit

Seyedehsomayeh Hatefinasab<sup>\*</sup>, Noel Rodriguez, Antonio García and Encarnacion Castillo

Department of Electronics and Computer Technology, University of Granada, 18071 Granada, Spain; noel@ugr.es (N.R.); grios@ugr.es (A.G.); encas@ugr.es (E.C.)

\*Correspondence: <u>hatefi@correo.ugr.es</u>

#### Electronics 2021, vol. 10, no. 11, 1256

- Received: 2 April 2021; Accepted: 21 May 2021; Published: 25 May 2021

- DOI: 10.3390/electronics10111256

- Impact factor: 2.690

- JCR Rank: 139/276 in category Engineering, Electrical & Electronic (Q3) (2021)

# Low-Cost Soft Error Robust Hardened D-Latch for CMOS Technology Circuit

**ABSTRACT:** In this paper, a Soft Error Hardened D-latch with improved performance is proposed, also featuring Single Event Upset (SEU) and Single Event Transient (SET) immunity. This novel D-latch can tolerate particles as charge injection in different internal nodes, as well as the input and output nodes. The performance of the new circuit has been assessed through different key parameters, such as power consumption, delay, Power-Delay Product (PDP) at various frequencies, voltage, temperature, and process variations. A set of simulations has been set up to benchmark the new proposed D-latch in comparison to previous D-latches, such as the Static D-latch, TPDICE-based D-latch, LSEH-1 and DICE D-latches. A comparison between these simulations proves that the proposed D-latch not only has a better immunity, but also features lower power consumption, delay, PDP, and area footprint. Moreover, the impact of temperature and process variations, such as aspect ratio (W/L)and threshold voltage transistor variability, on the proposed D-latch with regard to previous D-latches is investigated. Specifically, the delay and PDP of the proposed D-latch improves by 60.3% and 3.67%, respectively, when compared to the reference Static D-latch. Furthermore, the standard deviation of the threshold voltage transistor variability impact on the delay improved by 3.2%, while its impact on the power consumption improves by 9.1%. Finally, it is shown that the standard deviation of the (W/L) transistor variability on the power consumption is improved by 56.2%.

**KEYWORDS:** Hardened D-latch; Complementary Metal Oxide Semiconductor (CMOS) technology; Power-Delay Product (PDP); Soft Error (SE); SEU (Single Event Upset); High Impedance State (HIS); Single Event Transient (SET)

# **3.1 Introduction**

The advent of nano-scale transistors is a movement towards the reduction of the supply voltage of circuits, but this implies increases in delay and parasitic effects [1]. Thus, nano-scale CMOS circuits are more vulnerable to errors, such as the Soft Error (SE) caused by Single Event Upset (SEU) [1]. These errors have a huge negative impact on hardware security of integrated circuits, which is invested frequently [2,3], even for electronic applications [4–6]. In the particular case of SE, they have to be addressed as a hardware security or hardware reliability issue since they can be caused by and from the environment. Environmental radiation can be constituted by high energy particles (such as neutrons, protons, alpha particles, etc.), whose impact is similar to an injected charge or SEU to internal nodes. These charge injections can potentially change the

value of stored data inside digital circuits. Another typical error is Single Event Transient (SET), which is the result of a combinational path connecting to the input of D-latch in digital circuits [7]. This undesirable pulse, as error, can change the output voltage level of a D-latch. Traditional D-latches and memory cells are very vulnerable against upsets; thus, many approaches have been proposed to solve this problem; among these are hardened circuit design [8], error correcting codes (ECC) [9] and temporal redundancy [10]. Many new D-latches have also been proposed to increase immunity against SEU [11-17] and SET [7,13]. The design of these D-latches is based on filtering the SEU or/and SET. However, the highest immunity of D-latches against the SEU and SET is achieved by increasing the number of transistors, which yields several penalties such as higher power consumption, larger area, and delay. This work proposes a new D-latch considering this trade-off and aiming at achieving a better solution in terms of power consumption, delay, working condition (temperature), process variation, and filtering the possible length of SET pulses. Immunity against SEU for various nodes is also observed. These features have been paired with a lowcost and reliable design, having a power consumption and delay close to the Static Dlatch, set as a reference D-latch.

The paper is structured as follows: Section 3.2 revisits previous works on the topic including a review of existing hardened latches. The new D-latch architecture is introduced in Section 3.3, where SEU and SET immunity of the proposed D-latch are also tested by an exponential current pulse model that is inserted in various internal nodes. In Section 3.4, the impact of technological variability and temperature on the proposed and previous D-latches is investigated. The main conclusions are drawn in Section 3.5.

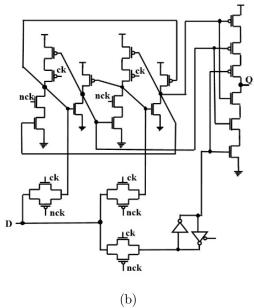

## **3.2 Previous Work**

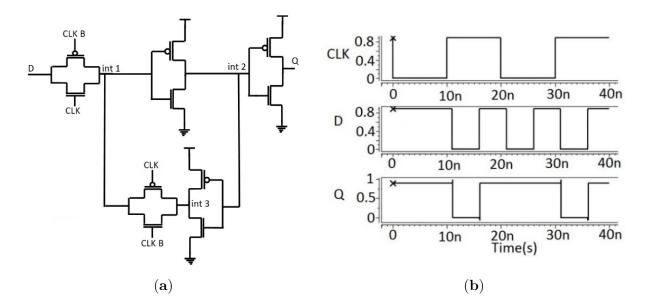

Traditional D-latches are very vulnerable against upset, which reduces their reliability for storing data in environments affected by single ionizing particles striking sensitive nodes. One of the better known of these traditional D-latches is the so-called Static Dlatch. Among the advantages of this latch are its low power consumption and simplicity. However, it is not immune to SEU and SET. The input and output signals of the Static D-latch and its schematic are shown in Figure 3.1.

As the reliability of data storage in the D-latch is of paramount importance, D-latches are typically classified in four types based on their immunity against SEU and SET:

(i). The first type of D-latch can tolerate SEU in some nodes, but they have some sensitive nodes against charge injection. The proposed D-latches in [13–15] are examples of this first type. It is important to mention that only some of this kind of D-latch can filter the SET by using a delay element, which is usually in the input lines [18–20].

Figure 3.1. (a) Static D-latch schematic; (b) input and output signals of the Static D-latch

- (ii). The second type of D-latch is fully immune against the SEU, but they cannot filter input SET. In this family the output can also be in a high impedance state (HIS). An example of this type of D-latch is the Dual Interlocked storage CEll (DICE) latch [8].

- (iii). The third type of D-latch can tolerate SEU in various nodes and avoids high impedance states, so high impedance at output cannot occur. However, they cannot filter the SET [21].

- (iv). The fourth type of D-latch is not only fully immune against the SEU and SET, but also has a high impedance state at the output [22–24]. The high impedance state of the output can be solved by a keeper, which is a buffer that connects input and output nodes [22–24].

A summary of the different types of D-latch is shown in Table 3.1. According to the four types of hardened D-latch, the so-called DICE belongs to the second type of hardened latch, being immune against SEU based on-cross the coupled inverter [8]. When SEU occurs in one node, the DICE structure can handle this SEU since it stores the input data in two different nodes. However, it cannot tolerate two simultaneous upsets to the two sensitive nodes and cannot filter SET pulses. Furthermore, the DICE presents high power consumption and delay in comparison to other hardened D-latches [25].

| Type   | Full Immune<br>SEU | Filtering<br>SET | HIS<br>Insensitive | Examples                                                                 |

|--------|--------------------|------------------|--------------------|--------------------------------------------------------------------------|

| First  | x                  | x                | ×                  | [14–16]                                                                  |

| Second | $\checkmark$       | ×                | ×                  | DICE [8], TMR [23]                                                       |

| Third  | $\checkmark$       | $\checkmark$     | ×                  | [21]                                                                     |

| Fourth | $\checkmark$       | $\checkmark$     | $\checkmark$       | TPDICE-based [24], FERST<br>[23], LSEH-1 [7]; LSEH-2 [1,7],<br>This work |

Table 3.1. Classification of different type of D-latch in regard to their soft-error immunity.

The Triple Modular Redundancy (TMR) latch presents a hardened design that makes it totally immune against upset, which fits the second type [23]. The TMR architecture can detect and correct SEU. However, it has a large number of transistors, which means that power consumption, area and delay penalty of this latch are far from ideal. In [23], a TMR D-latch including three Static D-latches with a voting circuit is discussed in regard to its performance and how it can be fully immune against upsets. In [23] a feedback redundant SEU/SET-tolerant latch (FERST) is also presented. FERST consists of two feedbacks and a delay element to avoid upset and there are two inverters as keepers to avoid a floating output node. Despite being fully immune against SEU, it consumes less power in comparison to TMR.

In [26], the authors proposed a latch design applying the hysteresis property of the Schmitt trigger inverter to increase immunity against SET; however, a Schmitt trigger based inverter with hysteresis property can reduce the speed of the D-latch. The feedback of this D-latch includes a C-element and two dynamic inverters. This feedback is active when CLK is "0" and holds the data in one node.

On the other hand, a Low-cost and Soft Error Hardened (LSEH) D-latch is proposed in [7], called LSEH-1, which has two separated paths to store the input data. These two paths have different delays to filter the SET of the input data. These two paths are connected to the C-element to trigger the output stage. LSEH-1 has three stages to store the input data at holding time. If the particle strikes in one stage, the two other stages can correct the output without any upsets. Furthermore, a so-called LSEH-2 is proposed in [7] having two latching stages in two different paths, which are connected to the C-element. Each input data, "0" and "1", passes through a different path to reach the output nodes, so SET pulses can be filtered in this D-latch. These LSEH-1 and LSEH-2 D-latches are benchmarked against the TMR in different parameters, such as delay, power consumption, temperature variation and process variation. This comparison shows better performance of these two LSEH-1 and LSEH-2 D-latches when compared to that of TMR [7]. In addition, full immunity against the SEU in any single node and filtering SET are the features of the D-latch proposed in [1]. This D-latch stores the data in two inverters with positive feedbacks during holding time. Moreover, it can tolerate single event multiple upsets (SEMUS), along with other features, such as reliability and low-cost structure.

Finally, the Triple Path DICE (TPDICE)-based D-latch in [24] can tolerate SEU and filter SET. It can handle Single Event Double-Upset (SEDU), which means that this D-latch can tolerate different charge injections at multiple nodes. The structure of this D-latch consists of a TPDICE, a triple-input Muller C-element, a Schmitt trigger inverter, and a keeper in the output node. The TPDICE is triggered by the clock and the D-input. The inputs of the triple-input Muller C-element of this D-latch are provided by TPDICE. This structure of TPDICE with C-element can recover the data, with a single event upset in one node. Moreover, the TPDICE is applied in this Dlatch to tolerate SEDU. The keeper is used in the output of TPDICE-based D-latch to avoid the high impedance state at the output. Besides, the embedded Schmitt trigger inverter on the propagation path can filter SET of the input.

It is worth mentioning that although this work focusses on SEU, hardened Dlatches to tackle DNU (double node upset) [5,27], and TNU (triple node upset) [28] are also being investigated. However, those alternatives, out of the scope of this work, are also penalized by higher transistor count and power consumption.

The proposed D-latch in this paper belongs to the fourth type and its immunity against SEU is better than that of the TPDICE-based D-latch [24], which is already considered fully immune, since the proposed design can tolerate a significant charge injection. The proposed D-latch also has lower transistor count and better performance in comparison to the TPDICE-based D-latch and other previous D-latches, regarding lower process variation, power consumption and delay. The next two sections are devoted to the presentation of the proposed D-latch and to analyzing these benefits in detail.

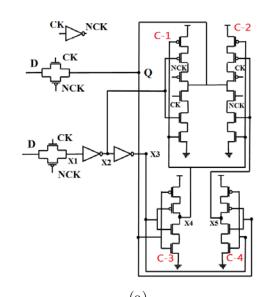

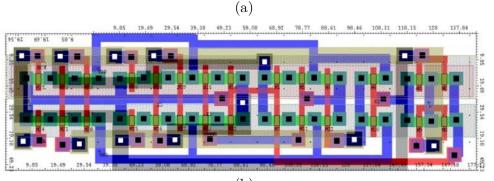

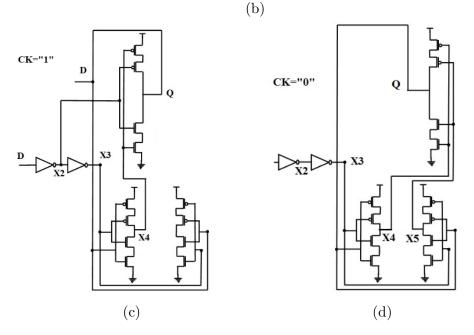

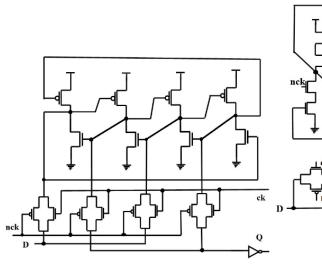

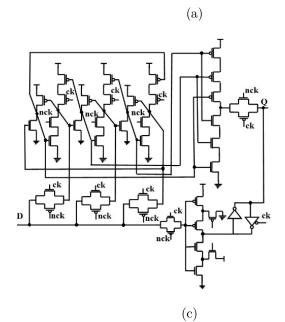

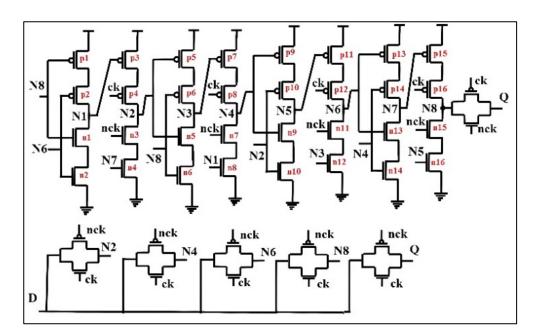

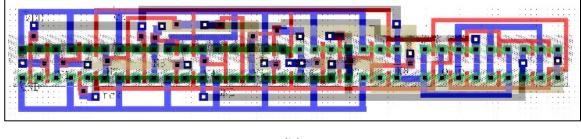

### 3.3 Proposed D-Latch

The schematic of the novel D-latch is shown in Figure 3.2a. The D-input passes through two paths; one path is integrated by one switch connecting the input to the output Dlatch and the other path is formed by two inverters and one switch that is ON when CK = "1". The "X4" and "X2" nodes are connected to the first C-element to delete the SET of D data; this C-element increases the delay because it is ON when CK ="1". The third and fourth C-elements are used to store the output for the holding time. The second C-element of the feedback path is ON when CLK = "0" and provides the feedback in the hold mode. Storing the D-input in two different C-elements makes the structure reliable against SEU. The C-element with the same inputs works as an inverter; however, when the values of two or three inputs are not the same, the output of the C-element does not change. For example, when one SEU occurs in one of the two or three different paths, the output node does not change. The layout of the proposed D-latch is shown in Figure 3.2b. The equivalent schematics for each case (CK = "0" and CK = "1") are also shown in Figure 3.2c and Figure 3.2d, respectively.

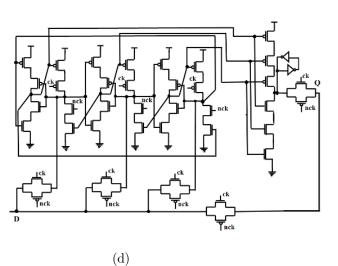

Figure 3.2. Proposed D-latch (a) schematic; (b) layout; (c) equivalent schematic when CK = "1"; (d) equivalent schematic when CK = "0".

As mentioned above for the D-latch in [26], the feedback is applied to hold the data during the holding time. As the positive feedback of the D-latch increases the side effects of the process variations, the activation of the positive feedback only during holding time reduces power consumption and improves immunity against process variability in threshold voltage and W/L.

As can be seen, the proposed D-latch has extra circuitry for masking SET, which turns into area consumption and larger delay. However, when CK = "1", there are two paths to connect input to output: one path consists only of the transmission gate and the other comprises inverters and the C-1, and C-3 elements. Therefore, the second path introduces more delay and masks SET. However, in this design input and output are connected by the transmission gate, therefore the delay will be reduced and it is not directly affected by the inverters and the C-1, and C-3 elements. Similarly to other approaches of hardened D-latches [5,24], two sample paths of input are used for improved reliability. Furthermore, the proposed D-latch features two separated circuits in transmission mode and holding that, combined with clock-gating technique, lead to a very low power consumption.

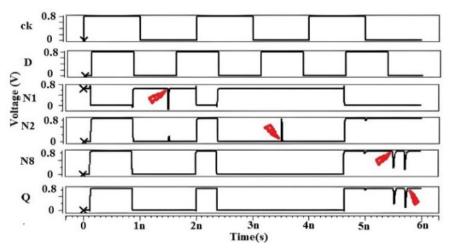

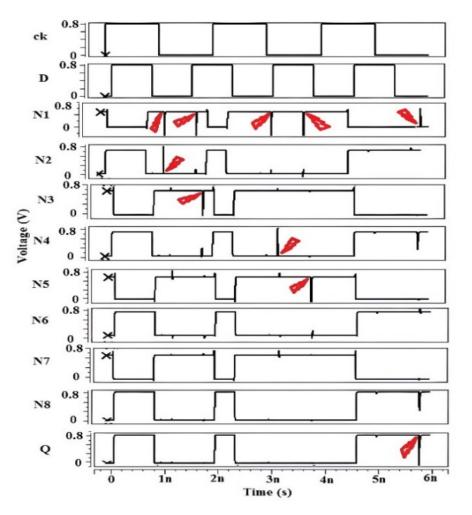

To investigate the SEU capability of the proposed D-latch, a number of SEUs are injected to various internal nodes. Then, the output signal is monitored to prove immunity against SEU at different nodes. The model of injected charge is based on an exponential current source [23]. The charge injection with different values is introduced during 0.3 ns and 0.9 V supply voltage at different internal nodes in reference CMOS technology at room temperature. Since different nodes can tolerate different values of charge injections, the maximum value of charge injection has been calculated for each specific node to produce voltage spikes slightly over the supply voltage and under zero volts [7,24], as shown in Figures 3.3–3.5 to test SEU immunity. The shape of the current source can be expressed mathematically [29]:

$$Q = \int_0^t \frac{Q_{total}}{\tau_f - \tau_r} \times \left( e^{-t/\tau_f} - e^{-t/\tau_r} \right) dt$$

(1)

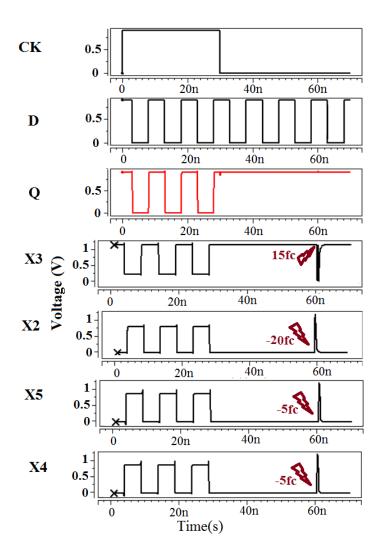

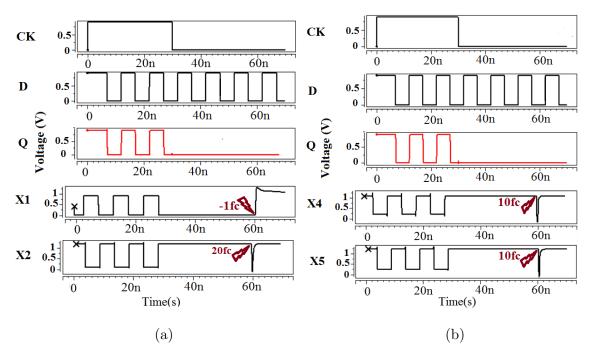

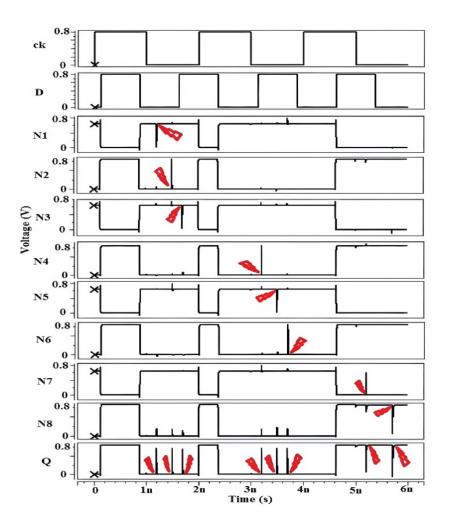

where  $Q_{notal}$  is the total charge generated by the upset,  $\tau_r$  is a constant coefficient of fall time and  $\tau_r$  is a constant coefficient of rise time. Four different situations for each node are considered to test the proposed D-latch to observe the output. For example, the positive and negative charge injections are introduced to the "X1" node, when the output is "1" or "0" at the holding time. Thus, these four situations are tested for all internal nodes. Figure 3.3 shows the results of this test, when the output is "1" during the holding time with positive charge injections introduced in "X3" node and with negative charge injections introduced in "X3" nodes. As can be observed, the output node "Q" is not affected by the SEU event in each one of these tests. For example, when the negative charge is injected in the "X5" node when "Q" is in the high logic value "1", the value after this charge injection maintains the value of "Q" is "1" and, as can be seen, the value of "Q" does not change. This kind of test

shows the immunity of the proposed D-latch against SEU. Moreover, for all of these tests (SEU immunity) for various nodes and for monitoring the Q node, the high impedance state does not occur, which means this proposed D-latch is insensitive to high impedance.

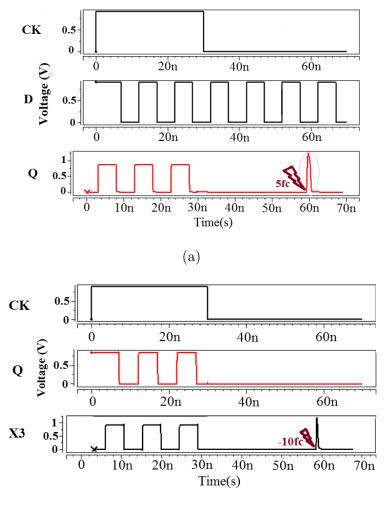

Figures 3.4 and 3.5 show test results of charge injection when the output is "0" during the holding time. In Figure 3.4, "Q" and "X3" nodes in the direct path are injected with charge. In Figure 3.4a, the positive charge injection is introduced to the "Q" node and, as shown, the proposed D-latch can tolerate this injection since the value of the output does not change after the upset.

Figure 3.3. Test results for SEU injection to nodes when the output is "1" during the holding

time; positive SEU injection to "X3" and negative SEU injection to "X2", "X4", and "X5" nodes.

(b)

Figure 3.4. Test results for a positive and negative SEU injections to nodes when the output is "0" during the holding time: (a) to "Q" node; (b) to "X3" node.

In Figure 3.4b, the test is performed for the "X3" node; in this case too the output of the proposed D-latch does not change its value.

Figure 3.5 shows results when the output is "0" and a negative injection is introduced in "X1" node and a positive injection is introduced in "X2", "X4", and "X5" nodes. As can be observed in this figure, in neither case would the output be affected.

The results of the study on critical charge injection in different nodes show that N1 can lose its data and valid logic state by small charge injections. N2 has more tolerance against charge injection. If more than 85 fC charge is injected to N2, it loses its value, but even this situation does not affect the Q value. The tolerance of N3, N4 is better, as they can tolerate up to 800 fC without disturbance in the data. Tolerance of N5 is lower since approximately 160 fC can be injected without losing the data. More importantly, for all these situations, the logic value of Q does not change. The previous figures for charge injections are very high, substantially over the usual value for testing SEU immunity, i.e., 20 fC [7].

Figure 3.5. Test results when the output is "0" during the holding time: (a) negative and positive SEU injection to "X1" and "X2" nodes, respectively; (b) positive SEU injection to "X4" and "X5" nodes, respectively.

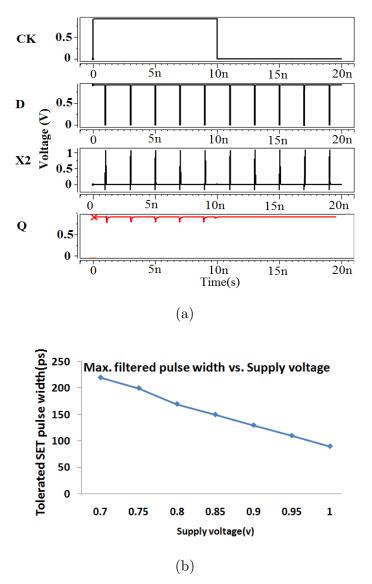

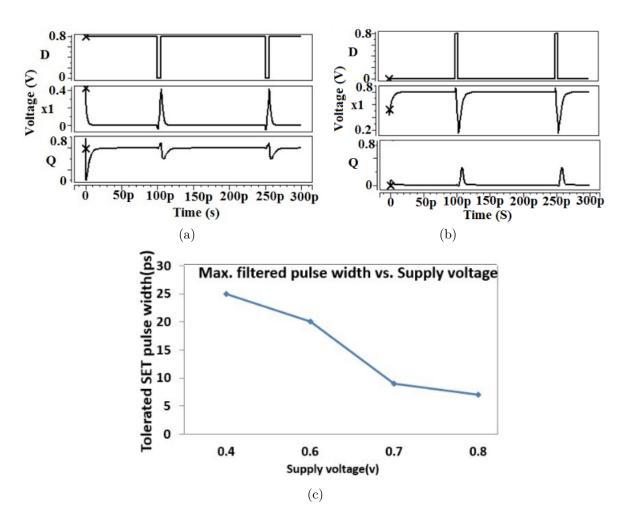

A further test has been carried out to demonstrate the SET masking capability of the proposed D-latch. The result of this test is shown in Figure 3.6. The proposed design can mask undesirable pulses that are generated at the combinational digital circuits of previous D-latch stages. In the transparent mode, SET can be filtered by two simple inverters and the first and third C-elements comparing data of two paths, with differences in two inverters and two C-elements to produce delay. Those two inverters, and the first, and third C-elements in the direct path, increase the delay but provide the D-latch with one important feature: the filtering of the SET. SET has no impact on the output from the feedback path from "X4" and "X5" nodes, since the second C-element connecting these nodes is not ON at the transparent mode. In Figure 3.6a, the input signal is shown with a 100 ps SET pulse at 0.9 V supply voltage. illustrating how this SET pulse is filtered by the proposed D-latch. It is worth mentioning that this masking depends on the supply voltage, the width of SET pulse, the delay and the temperature. The maximum width of SET pulses filtered by the proposed D-latch is shown as a function of supply voltages in Figure 3.6b. As can be seen, the maximum pulse width of SET decreases as the voltage supply increases (higher conductivity of the transistors) [7]. This dependency should be considered when it is necessary to suppress the SET pulse in sensitive applications [30–32]

Figure 3.6. (a) SET pulse filtering capability of the proposed D-latch; (b) maximum pulse width of SET filtered by the proposed D-latch at various supply voltages.

It is worth mentioning that in [24], aiming at masking SET, a Schmitt Trigger Inverter is used in transparent mode; however, it has a large impact on delay because of the hysteresis property. LSEH-2 [7] also has two different paths for two different inputs, "0" and "1", which implies huge power consumption and area for filtering SET without double sampling, reducing reliability. These solutions are avoided in this work in order to achieve reasonable delay and accuracy. Thanks to the double sampling with different delays, SET is masked. The delay of the two paths (one transmission gate, and the inverters and C-elements) depends indirectly on the delay of inverters and C-1 and C-3 elements. The aspect ratio of PMOS and NMOS of the inverter and C-1 and C-3 element can also affect the delay. However, in our design they do not have a significant impact in comparison to the approach used for masking SET in other Dlatches [7,23,24]; therefore, this effect has been neglected.

## 3.4 Latch Evaluation and Benchmarking

In this section the Static D-latch, DICE [8], TPDICE-based D-latch [24], LSEH-1 D-latch [7] and the proposed D-latch are simulated at three power supply voltages and three frequencies using HSPICE in the reference TSMC 65nm CMOS technology. In these simulations, the aspect ratio of PMOS transistors is W/L = 130nm/65nm, while the aspect ratio of NMOS transistors is W/L = 120nm/65nm. Benchmarking of various important characteristics, such as power consumption, Power Delay Product (PDP), and (D-Q) delay is presented. All these D-latches are immune against SEU apart from the Static D-latch, which is chosen as a reference since it features less power consumption and propagation delay. Furthermore, the proposed D-latch, TPDICE-based D-latch, and LSEH-1 D-latches can filter SET pulses.

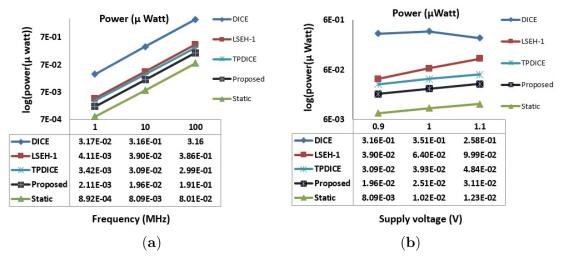

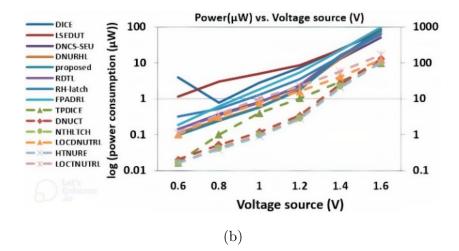

### **3.4.1** Power Consumption

As can be observed in Figure 3.7, the power consumption of the proposed D-latch is lower than those of all the other previous hardened D-latches (all of them designed to achieve minimum footprint), DICE [8], TPDICE-based D-latch [24] and LSEH-1 latch [7]. They all have been simulated at different frequencies, from 1 MHz to 100 MHz. at 0.9 V power supply voltage (Figure 3.7a), and different supply voltages, ranging from 0.9 to 1.1 V, at 10 MHz input frequency (Figure 3.7b). The power consumption of the proposed D-latch is higher than that of the Static D-latch, with an increment of 142%, but with the introduction of immunity against SEU and SET. The lower power consumption of the proposed D-latch in comparison to the other alternatives is attributed to the use of the clock-gating C-elements. There are two clock-gating Celements in the proposed D-latch: the first one on the transparent path for filtering SET, which is ON whenever the CK = "1", and the second in the feedback path, which is ON whenever CK = "0".

Figure 3.7. Power consumption of various D-latches: (a) at three frequencies from 1 MHz to 100 MHz and 0.9 V power supply voltage; (b) at three supply voltages and 10 MHz input frequency.

Moreover, the proposed D-latch has separate stages for transparent mode and holding time, which further reduces power consumption and delay. The delay decreases because in transparent mode the output can be set without passing from the saving nodes, which are used for holding time, while power consumption is reduced since, by separating two modes, it is possible to use clock gating-based C-elements.

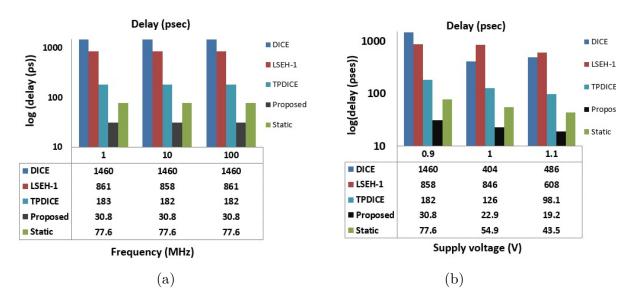

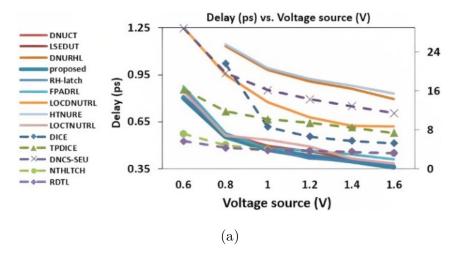

### 3.4.2 Delay

The delay is one of the most important parameters of D-latches. This decreases with increasing supply voltages due to the higher conductivity of the channel of the transistors, as shown in Figure 3.8. According to the results, the improvement of the proposed D-latch delay in comparison to the Static D-latch is up to 60%.

### 3.4.3 PDP

Furthermore, as PDP is a figure of merit showing the total performance of D-latches and, in particular, commonly used to evaluate hardened D-latches [7,30], a PDP comparison of the proposed and previous D-latches is shown in Figure 3.9. As can be seen, the PDP of the proposed D-latch is even slightly better than that of the Static D-latch, with a 3.67% improvement. This improvement is achieved by reducing delay, as PDP is power consumption multiplied by delay.

Figure 3.8. Delay of various D-latches: (a) at various frequencies from 1 MHz to 100 MHz and 0.9 V power supply voltage; (b) at three supply voltages and 10 MHz input frequency.

Figure 3.9. PDP of various D-latches: (a) at various frequencies from 1 MHz to 100 MHz and 0.9 V power supply voltage; (b) at three supply voltages and 10 MHz input frequency.

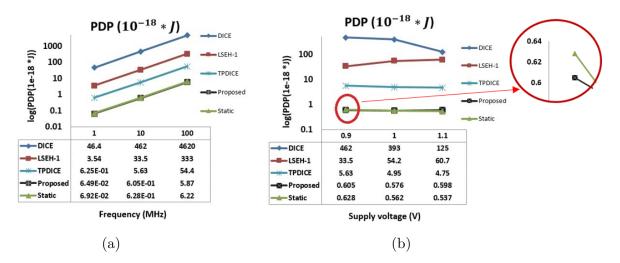

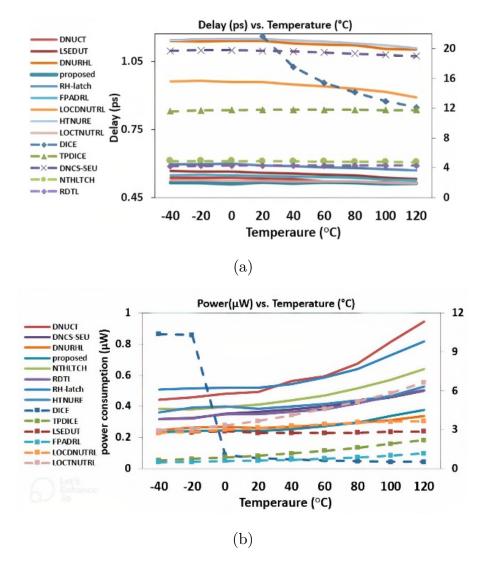

### 3.4.4 Temperature Variation

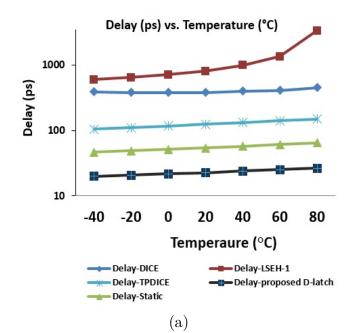

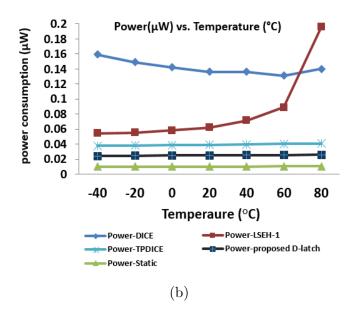

One of the most important operational parameters considerably affecting the D-latch performance is temperature, which may change dramatically under different conditions. To show this impact, the DICE, TPDICE-based D-latch, Static, LSEH-1, and proposed D-latches are simulated at different temperatures ranging from -40 °C to 80 °C (industrial range) with 10 °C steps.

As expected, raising the temperature increases the delay (above 30 °C for DICE) due to the lower electrical conductivity (lower carrier's mobility) and increases the power consumption (above 60 °C for DICE), as high temperature increases current leakage [33]. However, the temperature effect on the proposed D-latch is lower than in other D-latches, such as LSEH-1, DICE, and TPDICE-based D-latches, as deduced from Figure 3.10 (a comparative study in terms of a temperature coefficient has been included in Appendix A).

### 3.4.5 Area Usage

Another important benchmarking parameter is area usage; this parameter can be evaluated from the device layout. Table 3.2 shows the area comparison between the proposed D-latch and previous D-latches designed with Tanner L-EDIT [34] (all designs targeting minimum area). As can be observed, the proposed D-latch footprint matches that of DICE with the advantage of presenting better immunity and power consumption parameters.

Figure 3.10. Temperature variation effect on: (a) delay vs. temperature; (b) power consumption vs. temperature.

| Table 3.2. | Comparative area | of D-latches. |

|------------|------------------|---------------|

|------------|------------------|---------------|

| D-Latch         | Proposed<br>D-Latch | Static | TPDICE<br>[19] | DICE<br>[8] | LSEH-1<br>[7] |

|-----------------|---------------------|--------|----------------|-------------|---------------|

| $Area(\mu m)^2$ | 7.959               | 3.0816 | 18.04          | 7.944       | 12.21         |

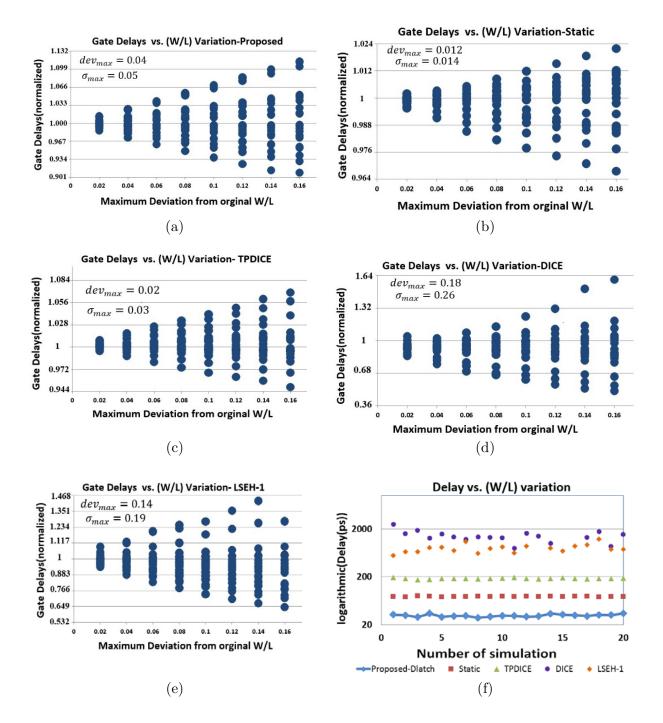

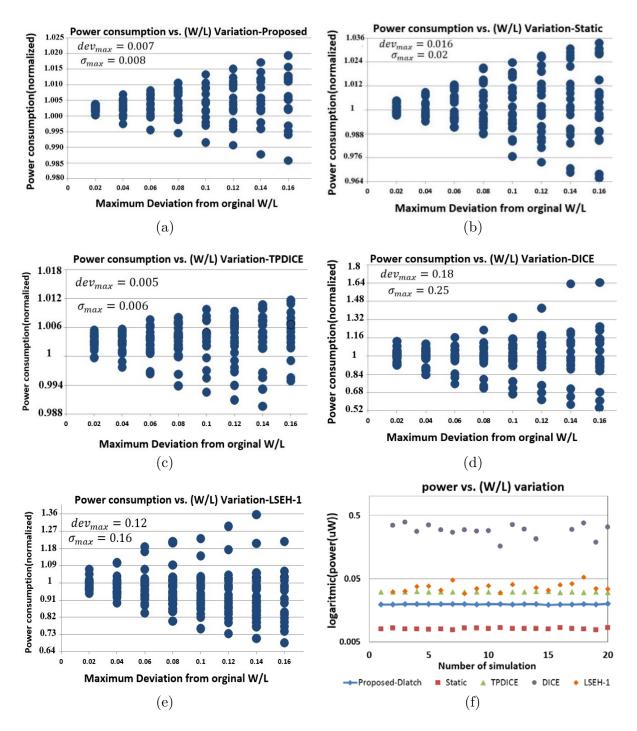

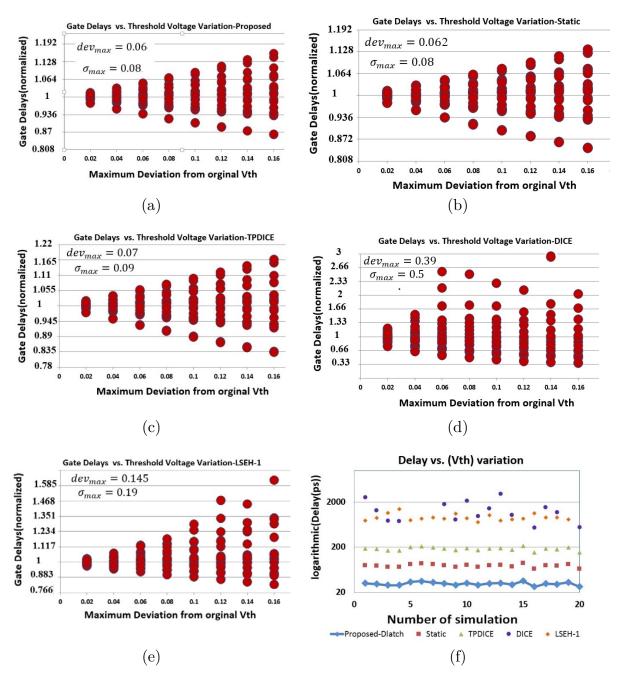

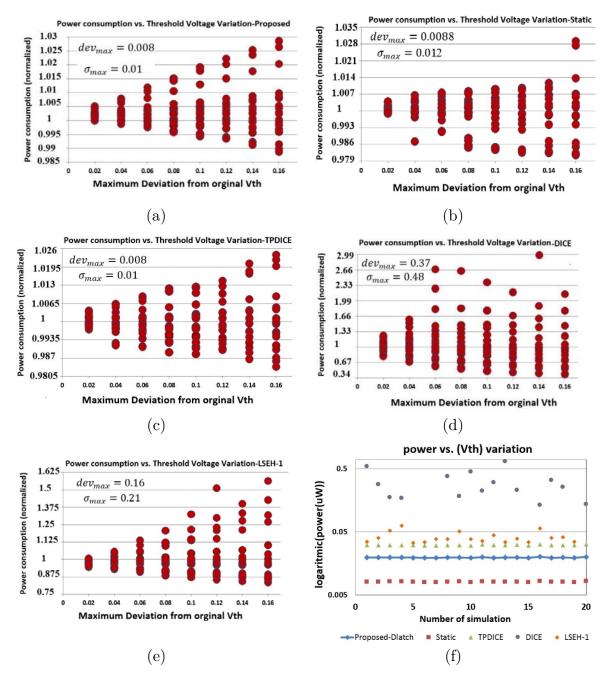

### **3.4.6** Process Variations

Finally, process variability, such as variation of transistor aspect ratio (W/L) or threshold voltage are analyzed. Monte Carlo simulations constitute a helpful tool to assess how the delay and power consumption are affected by these variations. A Gaussian distribution has been considered to model (W/L) and threshold voltage variability. The maximum deviations from the original (W/L) values of transistors and threshold voltages are set from 2% to 16%, which is the probable range of change normally used for comparison in this kind of study [1,7,27]. For each maximum deviation, 20 simulations are carried out to study the effect of (W/L) and threshold voltage variability on the delay and power consumption. Figure 3.11 shows the delay as the result of (W/L) transistor variability. In Figure 3.11a, the delay changes of the proposed D-latch as a result of (W/L) transistor variations are shown. It can be seen that the results have approximately the same delay variation as that of the TPDICEbased D-latch (Figure 3.11c), and the Static D-latch (Figure 3.11b), while it is much better than that of DICE (Figure 3.11d) and LSEH-1 D-latches (Figure 3.11e). The results are normalized to the delay of the original D-latch without any process variation. This normalization helps better visualize the effect of (W/L) transistor variations on delay. Figure 3.11f clearly shows the minimum variations of delays for the proposed D-latch when compared to other D-latches in maximum deviation.

In Figure 3.12, the effect of (W/L) variability on the power consumption is shown. As can be seen by varying (W/L) of the transistors by 2%–16% deviations from the original value, the power consumption of the proposed D-latch is affected similarly to that of the TPDICE-based D-latch and it is much better than that of the Static-latch, DICE, and LSH-1 latches.

The maximum variance ( $\sigma_{max}$ ) and standard deviation ( $dev_{max}$ ) are calculated for the delay and power consumption of the proposed, Static, and TPDICE-based D-latch, DICE, and LSEH-1 D-latches. These variance and standard deviation measurements are for the maximum deviation from the original (W/L) transistors, which is 16%. Maximum variance and deviation are shown in the insert of the plot for each D-latch in Figures 3.11–3.14. The impact of (W/L) variations on the power consumption of the proposed D-latch is low, but the delay deviation of the proposed D-latch is more than that of the Static D-latch. The delay standard deviations of the proposed D-latch, Static, and TPDICE-based D-latch, DICE, and LSEH-1 are 0.04, 0.012, 0.02, 0.18 and 0.14, respectively. The maximum variance of the delay of the proposed D-latch, Static, TPDICE-based D-latch, DICE, and LSEH-1 are 0.05, 0.014, 0.03, 0.26, and 0.19, respectively.

Figure 3.11. (W/L) variation effect on D-latch delay: (a) proposed D-latch; (b) Static D-latch (c) TPDICE-based D-latch (d) DICE (e) LSEH-1 latch (f) delay of D-latches with maximum deviation, 0.16, from original W/L.

Figure 3.12. (W/L) variation effect on power consumption: (a) proposed D-latch (b) Static D-latch (c) TPDICE-based D-latch (d) DICE (e) LSEH-1 latch (f) power consumption of D-latches with maximum deviation, 0.16, from original W/L value.

Figure 3.13. Threshold voltage variation effect on D-latch delay: (a) proposed D-latch (b); Static D-latch (c); TPDICE-based D-latch (d); DICE (e) LSEH-1 latch (f); delay of D-latches with maximum deviation, 0.16, from original threshold voltage.

Figure 3.14 Threshold voltage variation effect on power consumption: (a) proposed D-latch; (b) Static D-latch; (c) TPDICE-based D-latch; (d) DICE; (e) LSEH-1; (f) power consumption of D-latches with maximum deviation, 0.16, from original threshold voltage.

The standard deviation improvement of the (W/L) transistor variability on power consumption of the proposed D-latch, compared with the Static D-latch as reference, is 56.2%. In general, process variations have a negative effect on power consumption and delay.

The gate delay and power consumption variation versus threshold voltages are shown in Figures 3.13 and 3.14, respectively. The threshold voltages of the different transistors are changed by 2%–16% of their original values. As can be seen in Figures 3.13 and 3.14, the delay (D-Q) and power consumption variations of the proposed Dlatch are lower in comparison to those of Static, TPDICE-based D-latch, DICE, and LSEH-1 D-latches. This fact demonstrates a superior reliability of the proposed D-latch as compared to other alternatives. These lower variations of power consumption and delay for the proposed D-latch can be attributed to the lower effect of the positive feedback loop in this design (positive feedback yields huge process variation): in the proposed D-latch positive feedbacks are only activated during holding time and their paths are separated from the transparent path. These feedbacks enter a clock-gating C-element, which may reduce the effect of the positive feedback loop.

The impact of threshold voltage variations on the power consumption of the proposed D-latch is negligible. The delay standard deviations of the proposed D-latch, Static, and TPDICE-based D-latch, DICE, and LSEH-1 are 0.06, 0.062, 0.07, 0.39 and 0.145, respectively. The maximum threshold voltage variance of the delay of the proposed D-latch, Static, TPDICE-based D-latch, DICE, and LSEH-1 are 0.08, 0.08, 0.09, 0.5, and 0.19, respectively. The standard deviation improvement of threshold voltage transistors variability on the delay of the proposed D-latch, compared with that of a Static D-latch set as reference, is 3.2% and improvement for power consumption is 9.1%. In summary, threshold voltage variations have low effect on power consumption and delay on the proposed D-latch in comparison to the other hardened alternatives considered in this study.

## **3.5** Conclusions

In this contribution, a low-cost hardened D-latch is proposed with full immunity against SET and SEU. Additionally, it features a lower power consumption and delay in comparison to those of previous hardened D-latches alternatives, such as DICE, TPDICE-based D-latch, and LSEH-1. For benchmarking, the performance of the Static D-latch is set as reference, and the proposed D-latch provides the closest values in terms of delay and power consumption. The delay and PDP of the proposed D-latch improve 60.3% and 3.67%, respectively, in comparison to those of the reference latch at the expense of a power consumption increase (142%) with regards to the reference latch. A comparison between Static, DICE, TPDICE-based D-latch, LSEH-1, and the proposed D-latches reveals the superior performance of the proposed D-latch and a lesser impact from temperature and process variability in terms of transistor threshold

voltage and aspect ratio. The standard deviation improvement of threshold voltage transistor variability impact on the delay is improved by 3.2%, whereas its impact on the power consumption is improved by 9.1%. Furthermore, it has been shown that the standard deviation improvement of (W/L) transistor variability on the power consumption is 56.2%. Finally, the additional benefits do not come at the expense of a significative increase in cost (PDP, power consumption, area, delay) in comparison to the other hardened alternatives.

Author Contributions: Conceptualization, S.H; methodology, S.H.; software, S.H.; validation, S.H.; formal analysis, S.H., N.R., A.G., E.C.; data curation, S.H.; writing—original draft preparation, S.H.; writing—review and editing, S.H., N.R., A.G., E.C.; supervision, N.R., E.C. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement:

Informed Consent Statement:

Data Availability Statement:

**Conflicts of Interest:** The authors declare no conflict of interest.

# Appendix A

To show how the temperature effects on delay, the following coefficient can be defined.

$$\alpha = \frac{\left(delay - delay_{ref}\right)}{\left(T - T_{ref}\right)delay_{ref}} \tag{A1}$$

In (A1), reference temperature is 20 °C and  $\alpha$  is the delay coefficient by temperature, which is calculated for different D-latches and the proposed D-latch in Table 3.A1. As can be seen, the delay coefficient of the proposed D-latch is lower than those of the other alternatives.

Table 3.A1. Comparative delay coefficient by temperature of D-latches.

| D-Latch                             | Proposed | Static | TPDICE | DICE   | LSEH-1[7] |

|-------------------------------------|----------|--------|--------|--------|-----------|

| Delay coefficient<br>by temperature | 0.0028   | 0.0032 | 0.0034 | 0.0031 | 0.053     |

## References