# Compact Modeling Technology for the Simulation of Integrated Circuits Based on Graphene Field-Effect Transistors

Francisco Pasadas, Pedro C. Feijoo, Nikolaos Mavredakis, Aníbal Pacheco-Sanchez, Ferney A. Chaves, and David Jiménez\*

The progress made toward the definition of a modular compact modeling technology for graphene field-effect transistors (GFETs) that enables the electrical analysis of arbitrary GFET-based integrated circuits is reported. A set of primary models embracing the main physical principles defines the ideal GFET response under DC, transient (time domain), AC (frequency domain), and noise (frequency domain) analysis. Another set of secondary models accounts for the GFET non-idealities, such as extrinsic-, short-channel-, trapping/detrapping-, self-heating-, and non-quasi static-effects, which can have a significant impact under static and/or dynamic operation. At both device and circuit levels, significant consistency is demonstrated between the simulation output and experimental data for relevant operating conditions. Additionally, a perspective of the challenges during the scale up of the GFET modeling technology toward higher technology readiness levels while drawing a collaborative scenario among fabrication technology groups, modeling groups, and circuit designers, is provided.

# 1. Introduction

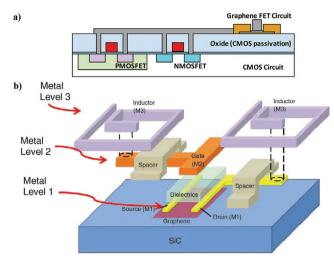

By combining graphene devices with interconnects and other components, innumerable circuits can be designed for analog and radio-frequency (RF) applications,<sup>[1]</sup> preferably in the form of an integrated circuit (IC). The graphene-based circuits could be integrated with the silicon CMOS IC to increase the IC functionality. A possible realization of a hybrid graphene-

| F. Pasadas, P. C. Feijoo, N. Mavredakis, A. Pacheco-Sanchez,<br>F. A. Chaves, D. Jiménez                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Departament d'Énginyeria Electrònica                                                                                              |

| Escola d'Enginyeria                                                                                                               |

| Universitat Autònoma de Barcelona                                                                                                 |

| Bellaterra 08193, Spain                                                                                                           |

| E-mail: david.jimenez@uab.cat                                                                                                     |

| F. Pasadas<br>Departamento de Electrónica y Tecnología de Computadores<br>Universidad de Granada<br>Granada 18071, Spain          |

| D The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/adma.202201691. |

|                                                                                                                                   |

© 2022 The Authors. Advanced Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

## DOI: 10.1002/adma.202201691

silicon IC could consist of a silicon platform that would implement digital circuits according to the CMOS process. In addition to the silicon platform, a graphene platform (e.g., based on graphene transistor technology) for making RF functions exploiting the unique properties of graphene could be fabricated, combining the best of two technologies in a single IC (Figure 1a).<sup>[2]</sup> The graphene platform could be monolithically integrated on a convenient substrate (Figure 1b) such as silicon carbide<sup>[3]</sup> or a flexible polymer<sup>[4]</sup> to exploit the functionality of graphene in specific applications.<sup>[5]</sup> Regardless of the choice between hybrid or monolithic, a compact modeling technology for the graphene platform is required to make predictions of the electrical behavior of

arbitrary circuits for DC, transient (time domain), AC (frequency domain), and noise (frequency domain) analysis. Every type of analysis requires a tailored set of models that capture the physics involved in a consistent way with experimental measurements for the relevant device operating conditions, which form the basis for a technology computer aided design (TCAD). Moreover, the mathematical complexity of the models should be kept low because multiple devices could be involved in a simulation. A TCAD tool is required during manufacturing to make the circuit design-fabrication cycle more efficient.

In this study, we present the progress made toward the definition of a modular compact modeling technology for the graphene field-effect transistor (GFET), which is considered as the building block of the graphene platform in the IC. For a circuit simulation to be realistic, various non-idealities must be modeled at the device level. They include the effect caused by the parasitic network (parasitic resistances, capacitances, and inductances) associated to the contact pads and interconnections, as well as the effect of extrinsic resistances (contact and gate resistance), which significantly reduce the expected device performance. Additionally, the effect of the charges trapped/ detrapped in the dielectric materials and interfaces must be included, which are related with the observed time-dependent drift of the operating bias point. In contrast, as short-channel length devices are needed to upscale the RF performance of graphene devices and circuits, short-channel effects (SCE) must be properly accounted by considering the 2D electrostatics and velocity saturation effect. It is also important to consider the

www.advancedsciencenews.com

**Figure 1.** a) Schematic cross section of a hybrid IC combining silicon and graphene platforms, where the former implements the digital part of the mixed-signal circuit and the latter implements the RF part. Reproduced with permission.<sup>[2]</sup> Copyright 2016, ACS. b) A wafer-scale graphene circuit in which all circuit components, including GFET and inductors, are monolithically integrated on a single silicon carbide wafer. Reproduced with permission.<sup>[6]</sup> Copyright 2012, Elsevier.

self-heating effects (SHE) at high fields that might produce an important reduction of the drain current. In addition, if the excitation frequency is close or above the device intrinsic cutoff frequency, the effect of carrier inertia should be considered, which requires a non-quasi-static (NQS) model. For the noise, the relevant physics must be collected into an appropriate compact model to obtain the noise indicators at the circuit level. This requires an analysis of the different noise sources and their dependence on the substrate, dielectric environment, as well as contact technology. A deep understanding of the mechanisms of local noise propagation to terminal currents and voltages is necessary. At high-frequency (HF) range, a careful analysis of the coupling mechanisms between the channel and the

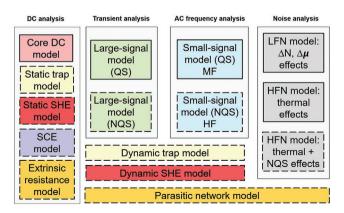

**Figure 2.** Modular compact modeling GFET technology presented in this study. The primary models describing the ideal device are represented by black solid lines, whereas the secondary models describing the device non-idealities are represented by black dashed lines. Acronyms used – SHE: self-heating effects, SCE: short-channel effects, QS: quasi-static, NQS: non-quasi-static, MF: medium frequency, HF: high frequency, LFN: low-frequency noise, HFN: high-frequency noise.

gate(s) is required. These efforts are relevant because figures of merit are limited by noise.

**ADVANCED**

www.advmat.de

A set of models capturing the relevant physics is needed to deal with the different types of electrical analysis, which forms the basis for a compact modeling technology targeting the simulation of ICs based on GFETs. As shown in **Figure 2**, they can be categorized into primary models defining the ideal device response and secondary models accounting for non-ideal effects to provide the necessary refinement to perform realistic circuit simulations. An in-depth explanation of relevant model details and main results for each type of analysis will be given along the Sections of the manuscript, namely DC (Section 2), transient (Section 3), AC (Section 4), and noise analysis (Section 5). In addition, we have benchmarked each model with experimental results to demonstrate its predictive capability.

# 2. DC Analysis

Here, a model accounting for the DC behavior of GFETs is presented. Section 2.1 introduces the intrinsic GFET core DC model, which is based on the Poisson's equation coupled with a drift-diffusion current equation, the former describing the device electrostatics (Section 2.1.1) and the latter describing the electron transport along the graphene channel (Section 2.1.2). In Section 2.2, various non-ideal effects affecting the operation of a GFET are added to the intrinsic model; thus, their inclusion is proven to be necessary to get consistency with experimental results from real devices. Those encompass charges trapped in the dielectric materials and interfaces (Section 2.2.1), SHE (Section 2.2.2), and SCE (Section 2.2.3). Finally, some relevant analytical models for the contact resistance, which can be used toward extending the intrinsic model with the obtained values of this parameter, have been presented (Section 2.2.4).

## 2.1. Core DC Model

Here, we present the model for the electrostatics of a four-terminal GFET in Section 2.1.1, which sets the basis for the later formulation of a drain current model in Section 2.1.2.

## 2.1.1. Electrostatics of a Four-Terminal FET

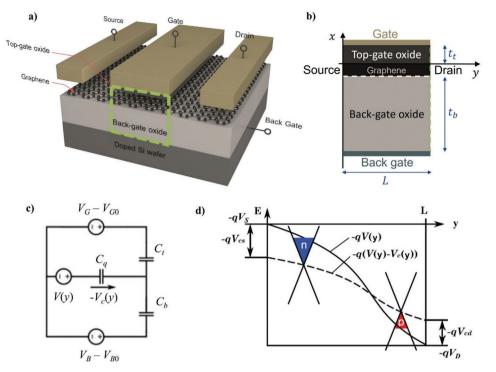

Let us consider a general GFET as that depicted in **Figure 3a**. The graphene sheet under the electric control of the gate electrodes plays the role of the active channel. The electrostatic modulation of the carrier concentration in the 2D channel is achieved via a double-gate stack consisting of top- and back-gate dielectrics and corresponding metal gates (Figure 3b). The graphene sheet is contacted with both a drain and source terminal; carrier transport is produced between both terminals when a non-zero bias is applied. The direction of current transport defines the longitudinal direction ( $\gamma$ ). The transversal direction (x) goes from the top gate to the bottom gate, whereas the *z*-direction goes across the width of the device (W), where *W* is sufficiently large such that the transistor can be considered uniform along the *z* axis. The electrostatics of the GFET

**Figure 3.** a) Schematic depiction of a four-terminal GFET. b) Cross section of the GFET and the domain where the Poisson's equation is evaluated to solve the electrostatics. This area corresponds to the dashed rectangle in (a). c) Equivalent capacitive circuit of the GFET. d) Schematic of the band diagram of the intrinsic device:<sup>[7,8]</sup> Energy, *E*, versus longitudinal position, *y*. The quasi-Fermi level  $E_F = -qV(y)$  and the Dirac energy  $E_D = -q\Psi(y) = -q(V(y) - V_c(y))$  are shown. When the quasi-Fermi level is located at the Dirac energy, the dubbed Dirac point or charge neutrality point is reached.  $V_D$  and  $V_S$  are the drain and source biases, respectively;  $V_{cd}$  and  $V_{cs}$  are the channel potentials at the drain and source sides, respectively. Two Dirac cones illustrate the mixed n/p-type channel of this example. a) Reproduced with permission.<sup>[9]</sup> Copyright 2016, IOP. d) Reproduced with permission.<sup>[8]</sup> Copyright 2014, IEEE.

can be evaluated by applying the Poisson's equation across its structure

$$\nabla \cdot [\varepsilon(x, y) \nabla \psi(x, y, T)] = \rho_{\text{free}}(x, y, T)$$

(1)

where *T* is the temperature,  $\varepsilon$  is the permittivity,  $\psi$  is the electrostatic potential, and  $\rho_{\text{free}}$  is the free charge density. Considering a 1D approximation for the GFET electrostatics along a transversal cut, the following charge-balance equation, which can be represented by the equivalent capacitive circuit shown in Figure 3c, can be obtained:<sup>[10,11]</sup>

$$Q_{\rm net}(\gamma, T) = -C_{\rm t}(V_{\rm G} - V_{\rm G0} - V(\gamma, T) + V_{\rm c}(\gamma, T)) -C_{\rm b}(V_{\rm B} - V_{\rm B0} - V(\gamma, T) + V_{\rm c}(\gamma, T))$$

(2)

where  $Q_{\text{net}}(y,T) = q[p(y,T) - n(y,T)]$  is the net sheet charge density; q is the elementary charge; p and n are the hole and electron carrier densities, respectively.  $C_t = \varepsilon_t/t_t (C_b = \varepsilon_b/t_b)$  is the top- (back-) oxide capacitance per unit area, with  $\varepsilon_t$  ( $\varepsilon_b$ ) being the top (back) dielectric constant and  $t_t$  ( $t_b$ ) the top- (back-) oxide thickness. The top (back) overdrive voltage is  $V_G - V_{G0}$  ( $V_B - V_{B0}$ ), where  $V_G$  ( $V_B$ ) is the top- (back-) gate potential, and  $V_{G0}$  ( $V_{B0}$ ) comprises the work-function difference between the top (back) gate and the graphene channel as well as the effect of additional fixed charge owing to impurities or doping. Because of the presence of non-negligible contact resistances in GFETs (Section 2.2.4), the intrinsic source and drain potentials ( $V_S$  and  $V_D$  at the active channel edges) cannot be shorted

to reference in practice; therefore, we adopted a general formulation where none of the terminals are grounded. Thus, the GFET is driven by terminal voltages defined with respect to some arbitrary reference point. V(y,T) is the quasi-Fermi level along the graphene channel, that is, the electrochemical potential, and it must fulfill the following boundary conditions: 1)  $V(y = 0,T) = V_S$  and 2)  $V(y = L,T) = V_D$  at the source and drain edge-sides, respectively, where *L* is the gate length. V(y,T) is assumed to be the same for both electrons and holes because the generation/recombination times for carriers in graphene are very short (1-100 ps);<sup>[12-14]</sup> therefore, electron and hole quasi-Fermi levels do not deviate significantly from each other.<sup>[7]</sup>  $V_c(y,T)$  represents the position-dependent chemical potential, that is, the shift of the Dirac potential ( $\psi(y, T)$ ) with respect to the quasi-Fermi level. Figure 3d shows a scheme of the electrostatic, electrochemical, and chemical potentials along the channel at an arbitrary bias. Electron and hole concentrations can be calculated as a function of  $V_c(y,T)$  using the following equations, which are a result of the density of states of graphene (deduced from its linear dispersion relation), where the electronic states are occupied according to the Fermi-Dirac statistics:

$$p(y,T) = \frac{\Delta^2}{2\pi(\hbar\nu_F)^2} + \frac{2}{\pi} \left(\frac{k_B T}{\hbar\nu_F}\right)^2 \mathfrak{F}_1 \left[\frac{qV_c(y,T)}{k_B T}\right]$$

$$n(y,T) = \frac{\Delta^2}{2\pi(\hbar\nu_F)^2} + \frac{2}{\pi} \left(\frac{k_B T}{\hbar\nu_F}\right)^2 \mathfrak{F}_1 \left[-\frac{qV_c(y,T)}{k_B T}\right]$$

(3)

where  $\Delta$  is the amplitude of the electrostatic potential inhomogeneity that causes the electron–hole puddles;<sup>[15]</sup>  $\mathfrak{F}_1$  is the Fermi–Dirac integral of first-order;  $k_{\rm B}$  is the Boltzmann constant,  $\hbar$  is the reduced Planck constant, and  $\nu_{\rm F} = \sqrt{3}a\gamma_0/2\hbar$  is the Fermi velocity; where a = 2.49 Å is the graphene lattice constant<sup>[16]</sup> and  $\gamma_0 = 3.16$  eV is the interlayer coupling.<sup>[17]</sup> The term  $\Delta^2/(2\pi(\hbar\nu_{\rm F})^2)$  accounts for the contribution of the puddles to the carrier concentration. The net sheet charge density and the quantum capacitance of graphene, which is defined as  $C_{\rm o}(\gamma, T) = \partial Q_{\rm net}/\partial V_{\rm c}$ , result in<sup>[8]</sup>

$$Q_{\rm net}(\gamma,T) = \frac{2q(k_{\rm B}T)^2}{\pi(\hbar\nu_{\rm F})^2} \left\{ \mathfrak{F}_1 \left[ \frac{qV_c(\gamma,T)}{k_{\rm B}T} \right] - \mathfrak{F}_1 \left[ -\frac{qV_c(\gamma,T)}{k_{\rm B}T} \right] \right\}$$

$$C_q(\gamma,T) = \frac{2q^2k_{\rm B}T}{\pi(\hbar\nu_{\rm F})^2} \ln \left[ 2 \left( 1 + \cosh \left[ \frac{qV_c(\gamma,T)}{k_{\rm B}T} \right] \right) \right]$$

(4)

$V_{\rm c}(\gamma, T)$  could be calculated as a function of the terminal biases ( $V_{\rm G}$ ,  $V_{\rm B}$ ,  $V_{\rm D}$ ,  $V_{\rm S}$ ) from Equations (2) and (4). However, this formulation is not convenient for a compact model compatible with circuit simulators. Using a square-root-based approximation for  $C_{\rm q}$ ,<sup>[18]</sup> it is possible to get an implicit expression for  $V_{\rm c}$  that can be written in terms of elemental functions, which is more suitable for compact modeling purposes

$$C_{q}(\gamma, T) \approx kc_{1}\sqrt{1 + (V_{c} / c_{1})^{2}}$$

$$Q_{net} = \int_{0}^{V_{c}} C_{q}(\tilde{V})d\tilde{V} = \frac{kc_{1}}{2} \left[ V_{c}\sqrt{1 + (V_{c} / c_{1})^{2}} + c_{1} \mathrm{asinh}(V_{c} / c_{1}) \right]$$

(5)

where  $k = 2q^3/(\pi(\hbar v_F)^2)$  and  $c_1 = (k_B T/q) \ln(4)$ .

The chemical potentials at the source  $V_{cs} = V_c(0,T)|_{V=V_s}$ and drain  $V_{cd} = V_c(L,T)|_{V=V_D}$  side-edges are the relevant quantities required to calculate the drain current. They can be easily determined by implementing the Verilog-A algorithm reported in refs. [8, 19] which allows the circuit simulator to solve Equations (2) and (5), favoring a circuit-compatible model.

## 2.1.2. Drain Current Model

Here, we deal with the development of a compact model for the GFET drain current. For such purpose, we assumed that the drift-diffusion theory is applicable. That implies that the carrier mean free path (MFP) is significantly shorter than *L*. The MFP is related to the graphene quality and values below 100 nm have been reported at room temperature.<sup>[15]</sup> Electrons and holes in graphene tend to present mobilities in the same order of magnitude in both experiments and simulations.<sup>[20–22]</sup> Here, we assume an equal mobility for both types of carriers for simplicity, but the models could be easily extended for nonequal mobilities. The drain current of a GFET according to the drift-diffusion theory can then be evaluated as

$$I_{\rm DS} = q W \rho_{\rm sh}(y,T) \mu(y,T) \frac{\partial V(y,T)}{\partial y}$$

(6)

ADVANCED MATERIAL

www.advmat.de

where  $\rho_{\rm sh}(y,T) = p(y,T) + n(y,T)$  is the transport carrier sheet density and  $\mu(y,T)$  is the field-dependent carrier mobility that reads as<sup>[9]</sup>

$$\mu(\gamma,T) = \frac{\mu_{LF}}{\sqrt[\beta]{1 + \left(\frac{\mu_{LF}}{\nu_{sat}(\gamma,T)} \middle| \frac{\partial \psi(0,\gamma,T)}{\partial \gamma} \middle| \right)^{\beta}}}$$

(7)

where  $\beta$  is a parameter of the model describing how sharp the transition between low- and high-field mobilities is and  $\mu_{\text{LF}}$  refers to the low-field carrier mobility. Saturation velocity  $v_{\text{sat}}(\gamma, T)$  is limited by optical phonon scattering according to the following equation:<sup>[23,24]</sup>

$$\nu_{\rm sat}(\gamma,T) = \frac{2\Omega}{\pi\sqrt{\pi\rho_{\rm sh}(\gamma,T)}} \frac{1}{N_{\rm OP}(T)+1} \sqrt{1 - \frac{\Omega^2}{4\pi\nu_{\rm F}^2\rho_{\rm sh}(\gamma,T)}}$$

$$N_{\rm OP}(T) = \frac{1}{\exp\left(\frac{\hbar\Omega}{k_{\rm B}T}\right) - 1}$$

(8)

where  $N_{OP}(T)$  and  $\hbar\Omega$  are the optical phonon occupation and energy, respectively. Low-field mobility and saturation velocity strongly depend on the dielectric materials surrounding the graphene layer, namely on the substrate and top-gate insulator used for the specific GFET geometry. These parameters depend on various scattering mechanisms that drive the carrier transport.

To obtain an explicit expression for Equation (6) in terms of the chemical potential,  $V_c$ , the following simplifications are needed: 1) under the condition of identical electron and hole mobilities,  $\rho_{\rm sh}(y,T)$  is approximated to its second-order Taylor expansion<sup>[8,18]</sup>

$$\rho_{\rm sh}(\gamma,T) \approx \frac{\Delta^2}{\pi (\hbar \nu_{\rm F})^2} + \frac{\pi (k_{\rm B}T)^2}{3(\hbar \nu_{\rm F})^2} + \frac{q^2 V_{\rm c}^2(\gamma,T)}{\pi (\hbar \nu_{\rm F})^2} \tag{9}$$

2) A soft-saturation model ( $\beta = 1$ ) is adopted. This value is consistent with numerical studies of electronic transport based on the Monte Carlo simulations;<sup>[25]</sup> 3)  $\nu_{sat}$  is assumed to be constant ( $\nu_{sat,0}$ ), instead of using Equation (8). This is because the implementation of Equation (8) together with (2) has been found to produce some artifacts that can result in harmonic distortion when large-signal transient simulations are performed. Considering all the simplifications, the following closed-form drain current equation is achieved:

$$I_{\rm DS} = \frac{W\mu_{\rm LF}}{L_{\rm eff}} \left\{ \frac{k}{2} \left( \frac{kc_1V_c(c_1^2 + 2V_c + 4c_2)\sqrt{1 + (V_c/c_1)^2}}{8(C_t + C_b)} - \frac{kc_1^2(c_1^2 - 4c_2)\sinh(V_c/c_1)}{8(C_t + C_b)} + \frac{V_c^3}{3} + c_2V_c \right) \right\}_{V_{\rm cs}}^{V_{\rm cd}}$$

(10)

where  $c_2 = (\pi k_B T)^2/3q^2 + \Delta^2/q^2$ . An effective electrical length,  $L_{\rm eff}$ , incorporating velocity saturation effects can be defined as

$$L_{\rm eff} = L + \frac{1}{C_{\rm t} + C_{\rm b}} \frac{\mu_{\rm LF}}{\nu_{\rm sat,0}} \{Q_{\rm net}\}_{V_{\rm cs}}^{V_{\rm cd}}$$

(11)

Adv. Mater. 2022, 2201691

2201691 (4 of 28)

ADVANCED SCIENCE NEWS \_\_\_\_\_ www.advancedsciencenews.com

# 2.2. Non-Ideal Effects for Enhancing the Prediction Capability of the Core DC Model

To achieve high-yield technology generations as well as reproducible electrical device characteristics toward exploiting GFETs at a circuit level, the trap mechanisms taking place within the device should be understood. Traps are material- or energeticdependent imperfections within the channel or its surroundings, for example, interfaces and oxide, able to capture and release carriers at different rates. Fast capture occurs within the channel and interfaces close to it, whereas the release of these trapped carriers is fast in the channel region and slow at the interfaces. In contrast, traps within the oxide region far from the channel have slow capture and emission time constants.<sup>[26]</sup> Graphene channels and their associated interfaces have been optimized toward a significant reduction of traps and defects in transistor architectures, for example, through passivation<sup>[27,28]</sup> and/or encapsulation techniques.<sup>[29,30]</sup> However, gate oxide has been a major issue in graphene transistors as well as in other emerging<sup>[26]</sup> and mature<sup>[31]</sup> FET technologies owing to scalability limitations;<sup>[26]</sup> thus, deep oxide (border) traps still affect the device performance.<sup>[32–35]</sup> High- $\kappa$  insulators, such as HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, as well as layered 2D insulators, such as hexagonal boron nitride (hBN), have been used to fabricate high-performance GFETs.<sup>[36,37]</sup> Trap-related phenomena in the aforementioned bulk high- $\kappa$  oxides have been observed and studied in silicon devices<sup>[38]</sup> as well as in emerging transistor technologies.<sup>[39]</sup> hBN has been suggested as the optimal dielectric for GFETs owing to the good lattice matching between the 2D channel and the 2D dielectric and minimized dangling bonds.[40-42] However, in addition to the low- $\kappa$  of hBN ( $\kappa \approx 3-4$ ),<sup>[40,43]</sup> which limits the equivalent oxide thickness scalability,<sup>[26]</sup> causing wafer-scale integration issues,<sup>[36]</sup> few works have reported on HF GFETs with hBN as the true gate oxide,<sup>[29,44,45]</sup> which exhibit poor HF performance, in stark contrast to GFETs with high- $\kappa$ oxides.<sup>[46-52]</sup> Furthermore, in contrast to the demonstrated low density of interface traps in hBN/graphene interfaces,<sup>[29,41]</sup> the temperature- and field-dependent carrier capture and emission processes owing to border traps within this 2D dielectric in 2D FETs,<sup>[26]</sup> specifically in GFETs, are not yet understood despite the recent characterization efforts.<sup>[53-55]</sup> A correct description of trap-related effects and their impact on the static and dynamic performance of graphene transistors can reveal true features of a corresponding technology.<sup>[34,35,56–58]</sup> The impact of traps on the transfer device characteristics is described by the static trap model module presented in Section 2.2.1, whereas the dynamic aspects of traps are introduced in Section 3.3.1 to complete the discussion.

The upscaling of RF performance in GFETs can be achieved by the progressive reduction of the channel length. When analyzing a short-channel GFET, velocity saturation is an important factor, but 2D electrostatics should also be considered. The strong electric fields caused at high bias affect the charge distribution along the graphene channel; thus, the 2D electrostatics across the plane perpendicular to graphene must be analyzed. Therefore, we developed a model that solves the 2D Poisson's equation coupled with the drift-diffusion equation, which includes the velocity saturation effect, to consider SCE effectively. In contrast, power dissipation in the graphene channel imperfectly spread out of the device increases its temperature,<sup>[59–61]</sup> triggering SHE. Temperature strongly affects charge transport through carrier concentration and saturation velocity. SHE and SCE will be modeled in Sections 2.2.2 and 2.2.3, respectively.

Finally, in Section 2.2.4, we studied the bias-dependent contact resistance, which embraces the phenomena at the metal–graphene (MG) interface as well as the junction formed between the graphene layer under the metal electrode and the graphene channel.

## 2.2.1. Static Trap Model

The actual performance of GFETs can be revealed by a device model correctly describing the hysteresis in both trap-affected and trap-reduced scenarios. In the literature, graphene transistor models including trap-effects have been reported;<sup>[34,58]</sup> however, their use has been limited either to observe the impact of the traps on the transport properties within a specific trap-affected scenario (forward bias sweep)<sup>[34]</sup> or without considering drain-to-source voltage dependence of the traps.<sup>[58]</sup> Next, we describe our model<sup>[35]</sup> that overcomes the latter issues.

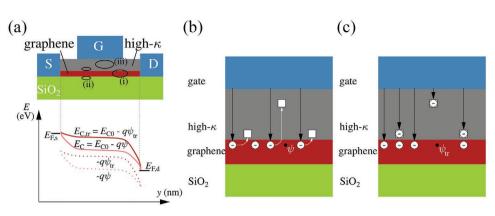

The density of trap centers in a high- $\kappa$  device, including GFETs, is higher in the gated region because all types of traps are present, that is, material, interface, and border traps. Hence, the modeling approach reviewed next focuses on this specific device region. A high- $\kappa$  oxide has been considered without loss of generality, that is, trapping mechanisms in 2D oxides are qualitatively similar to the ones in 3D oxides but differ in temperature and vertical field dependence. Trapping mechanisms in ungated regions can be implicitly included in scattering-related parameters.

Figure 4a shows a schematic cross-section of a top-gated graphene transistor with high- $\kappa$  oxide where trap centers are pointed out (top), and a sketch of the conduction band at a given  $V_{GS}$  in the linear regime is also illustrated (bottom). At a hypothetical state of the traps not affecting the device performance, that is, a trap-free state, the traps under the gate are empty; thus, the field lines emitted from the gate contact affect the channel carriers directly (cf. Figure 4b). Notably, a trap-free state is not possible in real conditions. However, a reduced impact of the charged traps on the I-V characteristics, that is, minimum hysteresis window, can be obtained by controlling the measurement conditions with sophisticated characterization techniques, for example, pulsed measurements.<sup>[32,35,56]</sup> In this study, the latter scenario is considered as a trap-reduced device performance. In a more practical scenario, the traps within the oxide are filled up so that the electrical field lines from the gate end on the traps, causing the channel potential to be shielded from the gate (cf. Figure 4c) and impacting the transport conditions, that is, the operating bias point is shifted leading to a hysteretic device performance. Herein, the latter is named as a trap-affected performance.

To reproduce and understand the impact of traps on critical device figures of merit toward using the devices in circuits, a compact model describing the behavior of trap-affected and trapreduced device performance accurately is required. The former characteristics can be obtained with a staircase characterization

**Figure 4.** a) Top: schematic cross section of a GFET indicating (i) channel, (ii) interface, and (iii) deep oxide traps. Bottom: sketch of the conduction energy band and channel potential under trap-free ( $E_c$ ,  $\psi$ ) and trap-affected ( $E_{c,tr}$ ,  $\psi_{tr}$ ) conditions. b,c) Schematic representations of the gated device region showing traps (squares) and carriers (circles) under trap-free (b) and trap-affected (c) conditions.

whereas an opposing-pulse technique can be used for the latter as shown in ref. [35]. Forward (increasing extrinsic,  $V_{GS,e}$ ) and backward (decreasing  $V_{GS,e}$ ) sweeps are applied in both characterization approaches to show a hysteresis window in the transfer characteristics. An analytical *I*–*V* compact model based on Equations (2) and (6),<sup>[10]</sup> under the condition of one active gate, has been used to describe the experimental data of GFETs by considering the impact of traps on the net charge within the graphene channel. The electrostatic equation of a practical onegate GFET yields a net charge,  $Q_{\text{net,tr}}(y,T)$ , description with the impact of traps given as<sup>[35]</sup>

$$Q_{\text{net,tr}}(y,T) = -C_t[V_G - V_{G0} - V(y,T) + V_c(y,T)] + qN_{tr}$$

(12)

where  $N_{\rm tr} = C_{\rm t}(DV_{\rm tr} - (K_{\rm tr}V_{\rm DS})/2)/q$  is the trap density with the trap-induced potential term  $DV_{\rm tr} - (K_{\rm tr}V_{\rm DS})/2$ .  $DV_{\rm tr}$  and  $K_{\rm tr}$  are the phenomenological model parameters accounting for the shift of  $V_{\rm Dirac}$  owing to traps impact and the  $V_{\rm DS}$  dependence of this shift, respectively. The Dirac voltage, considering both the trap-reduced and trap-affected scenarios, is calculated by considering straightforward conditions such as  $Q_{\rm net,tr}(y,T) \rightarrow 0$  at the charge neutrality point (CNP) as well as an average channel potential over the channel, that is,  $V(y,T) \approx V_{\rm DS}/2$  at similar bias conditions, which yields<sup>[35]</sup>

$$V_{\text{Dirac}} \approx \begin{cases} V_{\text{G0}} + \frac{V_{\text{DS}}}{2}, & \text{trap-reduced} \\ V_{\text{G0}} - DV_{\text{tr}} + \frac{(K_{\text{tr}} + 1)V_{\text{DS}}}{2}, & \text{trap-affected} \end{cases}$$

(13)

To reproduce the traps impact on the performance, the net charge expression in the model should account the corresponding scenario, that is, Equation (2) for the trap-reduced characteristics and Equation (12) for the trap-affected characteristics. Notably, the  $V_{\rm DS}$ -dependence of a trap-affected Dirac voltage owing to hot-carriers<sup>[32,62]</sup> has been considered in this model,<sup>[35]</sup> which is an innovation with respect to other compact models including the impact of traps but neglecting such important effect.<sup>[58]</sup>

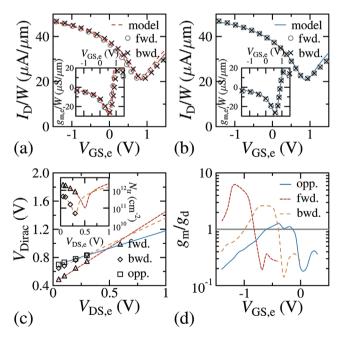

Both trap-affected and trap-reduced experimental transfer characteristics of a back-gated GFET technology with a gate width of 2  $\times$  12  $\mu m$  and a gate length of 300 nm (fabrica-

tion details in ref. [63]), obtained via staircase sweep and an opposing sweep characterization, respectively,<sup>[35]</sup> have been correctly described by the model in the p-type region, as shown in **Figure 5**a,b (model parameters are listed in Table II of ref. [35]). The hole dominant branch of the experimental data has been selected as the reference in the symmetric model, around  $V_{\text{Dirac}}$ , because better RF-related figures of merit are reported in this operation regime for this technology, in contrast to the n-type region.<sup>[35,64]</sup>

ADVANC

www.advmat.de

The model is valid for various  $V_{\rm DS}$  values, from low to higher ones, at different trap-affected states (Figures 2 and

**Figure 5.** a,b) Experimental (markers) and modeling (lines) data of a 300 nm-long GFET: transfer characteristics with forward and backward sweeps showing trap-affected (a) and trap-reduced (b) behavior at  $V_{DS} = 0.3$  V. Insets: transconductance plots at similar bias and conditions. c)  $V_{DS}$ -dependence of the Dirac voltage under different conditions. Inset: absolute value of the trap density for different  $V_{DS}$ . d) Intrinsic transistor gain at  $V_{DS} = -1$  V. a–d) Adapted with permission.<sup>[35]</sup> Copyright 2020, IEEE.

3 in ref. [35]), as indicated by the correct  $V_{\rm DS}$ -dependence of  $V_{\rm Dirac}$  observed in Figure 5c. The lower slope of the trapreduced  $V_{\rm Dirac}$  versus  $V_{\rm DS}$  plot ( $\approx 1/2$ ) with respect to the one obtained for the trap-affected data ( $\approx (K_{\rm tr} + 1)/2$ ) suggests a trap-induced overestimation of  $V_{\rm Dirac}$  at high fields, in contrast to a reproducible performance with the traps impact highly suppressed, that is, trap-reduced data. This is a crucial insight to be considered for the GFET performance in circuit applications.

Additionally, the trap density of the studied device is obtained for the different measurement sweeps from experimental data (see ref. [35] for the procedure) and the model parameters. The model can describe the  $V_{\rm DS}$  dependence of  $N_{\rm tr}$ , as shown in the inset of Figure 5c. Trapping and detrapping mechanisms can be elucidated from the curves for voltages lower and higher than the minimum point, respectively, which corresponds to a change of polarity of the trap-induced potential term. For instance, as indicated by the model curve, trapping processes are active for the forward staircase sweep at 0.3 V <  $V_{\rm DS}$  < 0.5 V, whereas traps are enabled by the release of previous trapped carriers for the backward sweep case at the same bias range, as suggested by the increase of  $N_{\rm tr}$  for the model curve. A correct description of  $N_{\rm tr}$  at different biases, such as the one obtained with this model, enables the obtaining of improved insights in the device physics, for example, on low-frequency noise (LFN) characterization of GFETs.[64]

The intrinsic gain,  $A_{\rm v,i} = g_{\rm m}/g_{\rm ds}$ , calculated from both the intrinsic transconductance ( $g_m = \partial I_{DS} / \partial V_G$ ) and output conductance  $(g_{ds} = \partial I_{DS} / \partial V_D)$ , has been shown with the model calibrated with trap-affected and trap-reduced data (cf. Figure 5d) of the device under study.<sup>[35]</sup> The result indicates higher A<sub>vi</sub> and different V<sub>GS</sub> dependence of this parameter for the trap-affected data than in the trap-reduced scenario. This is attributed to the trap-induced shielding of the channel potential because the changes of the current with respect to the different applied voltages, that is,  $g_{\rm m}$  and  $g_{\rm ds}$ , are affected differently depending on the traps state (measurement history). In addition to the experimental observations at different scenarios,<sup>[35]</sup> this model has shown the largely overlooked impact of traps on the performance of the graphene transistor. The approach used here enables a correct description of reproducible (trap-reduced) characteristics at room temperature toward exploiting such features in GFET-based circuit applications.

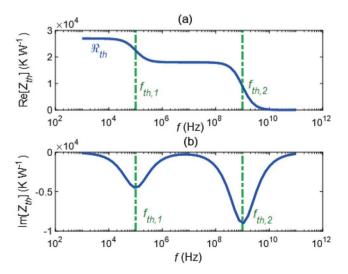

### 2.2.2. Static Self-Heating Model

Source-to-drain current within the graphene channel generates energy by the Joule effect, which can increase the temperature of the device considerably if the heat is not properly dissipated. The increase in graphene temperature, T, with respect to the ambient temperature,  $T_A$ , can be expressed as

$$T - T_{\rm A} = \Re_{\rm th} P_{\rm dis} \tag{14}$$

where  $P_{\rm dis} = |I_{\rm DS}V_{\rm DS}|$  corresponds to the power dissipated in the graphene channel and  $\Re_{\rm th}$  is the effective thermal resistance, which embraces all the paths through which the heat can be dissipated out of the channel.  $\Re_{\rm th}$  can be estimated according

www.advmat.de

to the methodology proposed in refs. [23, 65]. The method considers the combined effect produced by the graphene/dielectric interface, dielectric layer, and substrate thermal conductance. The thermal conductance contributed by the contacts is

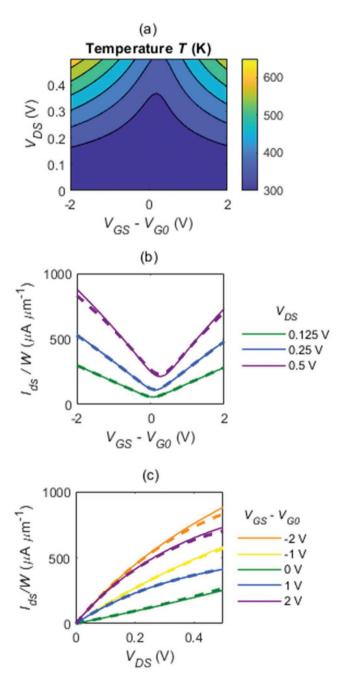

neglected. To demonstrate the impact of SHE, we simulated the device described in ref. [51] assuming a high thermal resistance of  $3 \times 10^4$  K W<sup>-1</sup>. Figure 6a shows the temperature distribution as a function of the bias. Temperatures can reach high values at

**Figure 6.** a) Temperature distribution as a function of the intrinsic bias voltage for a self-heated GFET. b) Transfer characteristics and c) output characteristics of a GFET at 300 K non-affected by SHE (solid) and affected by SHE (dashed).

large supply biases, in the order of the temperatures estimated for similar GFETs.<sup>[66]</sup> Moreover, experimental observations show that self-heating can increase the temperatures of graphene significantly when thermal resistances are large (e.g., with thin insulators).<sup>[67]</sup> The transfer and output characteristics either neglecting SHE (solid lines) or considering SHE (dashed lines) are presented in Figure 6b,c. From the figure, it can be observed that temperature affects the drain current in different ways. The drain current increases in polarizations near  $V_{\text{Dirac}}$ , whereas it decreases for large gate voltages. Near  $V_{\text{Dirac}}$ , the increase in drain current is caused by a higher thermal carrier concentration. However, the temperature reduces carrier mobility and saturation velocity, whose effect dominates for biases far from  $V_{\text{Dirac}}$ . Moreover, current tends to saturate because of self-heating.<sup>[24]</sup> Despite the current saturation, Section 3.3.2 shows that the performance of the SHE-affected device observed in DC does not imply an improvement in the RF figures of merit, as the actual AC small-signal output conductance is larger than the one observed at DC.

## 2.2.3. Short-Channel Model

To study the performance of short-channel GFET, we developed a numerical model that aims to find the self-consistent solution of the 2D Poisson's equation (Equation (1)) in the domain represented in Figure 3a and the current continuity equation (Equation (6)). In addition to velocity saturation, this model accounts for the 2D electrostatics to consider SCE. Because Equation (6) assumes a drift-diffusion scheme, the shortchannel model is valid when the GFET operates in this transport regime. Hence, the model cannot be applied to the pure ballistic regime.<sup>[68]</sup> This implies that the considered channel lengths should be significantly greater than the MFP of carriers in graphene, which is in the 10–100 nm range.<sup>[15,69,70]</sup>

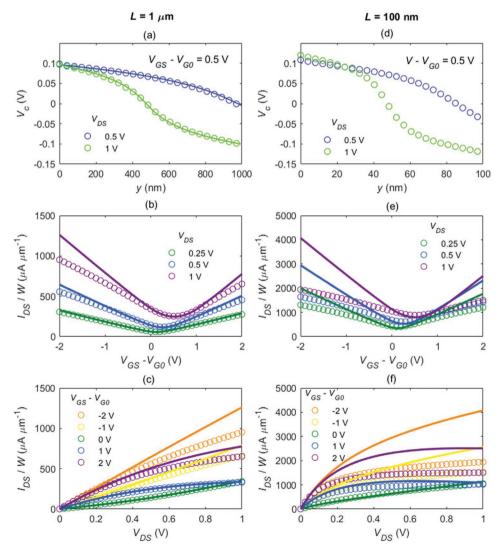

We thoroughly studied SCE for the reference device reported in ref. [51] by varying the channel length. **Figure 7** compares the compact model of Section 2.1 (solid lines) with the selfconsistent model, which considers 2D electrostatics (symbols). The figure shows the chemical potential and I-V curves for

**Figure 7.** a-f) Comparison between the compact model (solid lines) and the numerical model that accounts for SCE (circles) for a 1  $\mu$ m-long channel GFET (a-c) and a 100 nm-long channel GFET (d-f). a,d) Chemical potential along the channel. b,e) Transfer characteristics. c,f) Output characteristics.

the cases of channel lengths of 1  $\mu$ m, where both models give similar results, and 100 nm where models clearly diverge. The results of the short-channel device indicate that SCE imply a redistribution of carriers caused by 2D electrostatic effects:<sup>[9]</sup> carrier concentration close to source and drain edges increases as compared with the long device, as can be observed in the chemical potential distribution along the channel shown in Figure 7a,d. Additionally, the chemical potential slope becomes steeper, and the CNP (defined by the condition  $V_c = 0$ ) is slightly displaced toward the middle of the channel.<sup>[9]</sup>

Figure 7 also shows the differences between the compact model and the self-consistent model in predicting the transfer (Figure 7b,e) and output curves (Figure 7c,f). As for the 1 µm-long GFET, the differences between both models mainly come from the velocity saturation effect, where  $v_{sat,0}$  is kept constant in the compact model whereas it follows the more complex model described by Equation (8) in the self-consistent model. However, the predicted trends are analogous. In contrast, the predictions of both methods differ considerably for the 100 nm-long GFET. For this case, a significant degradation in the transconductance can be observed, which has a direct impact on the RF performance scaling.

#### 2.2.4. Metal-Graphene Contact Resistance

Although GFET has emerged as a promising device for analog/RF applications, the contact resistance ( $R_c$ ) embracing the phenomena arising at the interface between graphene and source/drain metal electrodes remains a major limiting factor that affects the electronic transport properties.<sup>[71–80]</sup> For RF electronic applications, it is a relevant issue with a strong impact on figures of merit such as the maximum frequency of oscillation ( $f_{max}$ ), intrinsic cut-off frequency ( $f_T$ ), and  $A_{v,i}$ .<sup>[9,81,82]</sup> Despite the considerable number of experimental and theoretical studies, the origin of  $R_c$  is still unclear owing to the multiple intrinsic and extrinsic factors affecting it, namely the nature of metals (chemisorbed or physisorbed), geometry of the contact (planar or edge), number of graphene layers, as well as impact of the fabrication process and bias. Therefore, a broad range of experimental values of  $R_c$  have been reported

in the literature even though the same contact metal has been considered.<sup>[83-93]</sup> In a metal-semiconductor junction (Schottky contact), a potential barrier (Schottky barrier) is formed at the interface. In an ideal case, the Schottky barrier height is given by the difference between the metal work function and the semiconductor electron affinity (Schottky-Mott approach). For conventional (3D) semiconductors, a Schottky contact can be turned into an Ohmic contact by lowering the Schottky barrier height with opportune metal choice or lowering the barrier thickness sufficiently, in the order of few nanometers, by heavily doping the semiconductor. Therefore, electrons can go through the barrier driven by the quantum tunneling effect. However, for MG junction, the difference between the dimensional nature of the metal (3D) and graphene (2D) as well as the strong influence of the contact metal and the impact of the device fabrication details on the graphene properties hinder its description by the conventional Schottky-Mott picture. Furthermore, graphene zero energy bandgap prevents the formation of conventional Schottky contact and its small density of states near the Dirac point strongly limits the current injection from the metal.<sup>[94]</sup>

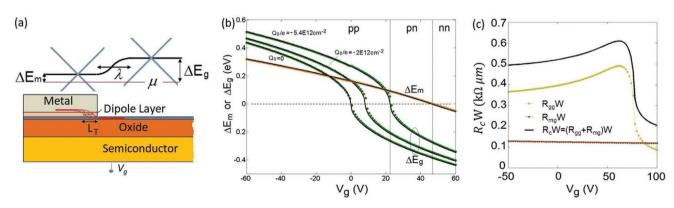

When a finite metal electrode is deposited to cover part of a graphene sheet as in the GFET contact shown in Figure 8a, the following electrostatic effects appear: 1) there is a charge transfer through the interface producing a doping of the graphene underneath, which is characterized by a significant shift  $\Delta E_{\rm m}$  of the graphene Fermi level with respect to its Dirac point. This is owing to the small density of states near the Dirac energy. Not only the difference between metal and graphene work functions should be considered in the process, but also the type of chemical interaction at the surface, namely physisorption or chemisorption.<sup>[96,97]</sup> 2) A potential step is established between graphene under the metal and the graphene channel,<sup>[98,99]</sup> which is produced by a charge transfer between the two graphene regions. As shown in Figure 8a, the potential step is characterized by an effective length,  $\lambda$ , and energy shifts  $\Delta E_{\rm m}$  and  $\Delta E_{\rm g}$  in the graphene under the metal and graphene channel, respectively. In the limit where the contact length is larger than the transfer length,  $L_{T}$ , which is defined as the effective contact length contributing to the injection of carriers in graphene, there is a current crowding effect indicative of

**Figure 8.** a) Sketch of the MG contact on a back-gate structure and the corresponding potential step formed between graphene under the metal and graphene in the channel. The red lines denote the current crowding effects near the contact edge. b) Graphene Fermi level shifts with respect to the Dirac point for different values of doping ( $Q_0/q$ ), with palladium as a metal contact. c) Predicted  $R_c$  and its components,  $R_{mg}$  and  $R_{gg}$ , considering titanium as a metal. a–c) Reproduced with permission.<sup>[95]</sup> Copyright 2015, IOP Publishing.

an  $R_c$  dependence on the contact width instead of the contact area.<sup>[100,101]</sup> Evidence of the current crowding has been reported by photocurrent spectroscopy experiment for graphene–gold contact.<sup>[102]</sup>

Apart from the abovementioned electrostatics, several theoretical studies have been conducted to understand both intrinsic and extrinsic factors in controlling the values of  $R_c$ in graphene-based devices. We can classify the theoretical studies as: 1) ab initio calculations<sup>[87,91,103-109]</sup> and 2) analytical models.<sup>[78,95,96,101]</sup> The ab initio calculations have helped to comprehend the nature of the MG interface at the microscopic level and to suggest ways to engineer contact resistance. For example, they have been useful to explain the spread of  $R_c$  measurements as due to uncontrolled graphene doping and/or the chemistry of the interface. However, these types of models have an extremely high computational cost. In contrast, for the analytical models, as proposed in ref. [101] the transport in the MG junction is described as carrier injection from metal to graphene underneath with probability  $T_{me}$  followed by injection to the graphene channel with probability  $\mathcal{T}_{\rm gg}$ . The conductance of MG contact is expressed in terms of the conduction modes in graphene and the transmission probabilities following the Landauer approach. However, in this model, the mechanism of  $\mathcal{T}_{\mbox{\tiny mg}}$  is ambiguous and it does not consider the 3D and 2D nature of the metal electrode and graphene sheet, respectively. To solve this issue, a theoretical model of carrier transport considering the dimensional nature has been developed in ref. [95]. The physical model is based on the Bardeen transfer Hamiltonian (BTH) method for the calculation of the resistance,  $R_{mg}$ , between the metal and graphene underneath and on the Landauer approach to calculate the resistance,  $R_{gg}$ , arising at the potential step across the junction formed between the graphene under the metal and the graphene channel. The total contact resistance can be calculated as  $R_{\rm c} = R_{\rm mg} + R_{\rm gg}$ . Here, the gate voltage dependence of  $\Delta E_{\rm m}$ and  $\Delta E_{\rm g}$ , in a standard back-gate GFET configuration, is conveniently solved using a 1D model, as illustrated in Figure 8b, where palladium was assumed as the metal electrode. These two quantities are key factors to determine  $R_c$  as a function of the gate voltage. Different types of junctions could be developed depending on the back-gate bias, namely pp-type, pntype, and nn-type junctions. By assuming a chemical doping of the graphene channel  $Q_0/q = -5.4 \times 10^{12}$  cm<sup>-2</sup>, the transitions from pp- to pn-type at  $V_{\rm G} \approx 23$  V and from pn- to nn-type at  $V_{\rm G} \approx 46$  V were captured in accordance with reported measurements.<sup>[101]</sup> Moreover, by combining the BTH method for calculating the specific contact resistivity,<sup>[96]</sup>  $\rho_c$ , with the transmission line model,<sup>[110]</sup> the simple analytical expression

$$R_{\rm mg}(\Delta E_{\rm m}) = \frac{\sqrt{\rho_{\rm c} R_{\rm sh}^{\rm m}} \coth\left(\frac{L_{\rm c}}{L_{\rm T}}\right)}{W_{\rm c}}$$

(15)

is found; thus, its gate voltage dependence for arbitrary metals is predicted. Here,  $R_{\rm sh}^{\rm m}$  is the sheet resistance of graphene under the metal;  $L_{\rm c}$  and  $W_{\rm c}$  are the contact dimensions. Additionally,  $R_{\rm gg}$  strictly depends on the effective length,  $\lambda$ , of the potential step that builds up between the graphene under the metal and the graphene channel, which can be calculated as  $R_{gg}^{-1}(\Delta E_{m}, \Delta E_{g}) = 2e^{2}W_{c}(h\pi)^{-1}\int_{-k_{F}}^{k_{F}}\mathcal{T}_{gg}dk_{y}$ (16)

4DVANCED

www.advmat.de

where  $k_{\rm F} = \min (|\Delta E_{\rm m}|, |\Delta E_{\rm g}|)/\hbar v_{\rm F}$  and  $\mathcal{T}_{\rm gg}$  is the transmission probability of Dirac fermions across the potential step given by Cayssol et al.<sup>[98]</sup> According to this model, depending on the metal electrode and a possible chemical doping of the graphene channel, the two components of  $R_{\rm c}$  could be either similar in magnitude or of very different orders. It has been established that  $R_{\rm gg}$  is the dominant component for nickel and titanium electrodes, whereas there is a competition between both components for palladium. For illustrative purposes, the breakdown of  $R_{\rm c}$  in its two components for a titanium-contacted GFET is reproduced in Figure 8c.

Recently, a physical model of  $R_c$  in titanium-contacted graphene-based FETs<sup>[78]</sup> has been developed considering an interfacial layer including oxidized Ti and polymethyl methacrylate residues at the Ti–G interface from the processing conditions of the contact. The study indicates that  $R_c$  is highly dependent on the properties of the interfacial layer. Similar to ref. [101]  $R_c$  is calculated as

$$R_{c}^{-1} \propto \int_{-\infty}^{\infty} dE_{1}G(qE_{1} - \Delta E_{m}, t_{1}) \int_{-\infty}^{\infty} dE_{2}G(qE_{2} - \Delta E_{g}, t_{2}) \int_{-k_{F}}^{k_{F}} dk_{\gamma} \mathcal{T}_{\text{total}}$$

(17)

where

$$\mathcal{T}_{\text{total}} = \mathcal{T}_{\text{mg}} \mathcal{T}_{\text{gg}} / [1 - (1 - \mathcal{T}_{\text{mg}})(1 - \mathcal{T}_{\text{gg}})]$$

(18)

is the total carrier transmission probability and the Gaussian functions G(E, t) with effectives broadening  $t_1$  and  $t_2$  have been considered to get a more realistic model. Parameter  $t_1$  considers the coupling between the metal and the quasi-bound graphene states underneath;  $t_2$  is a parameter embedding information of the random disorder potential in the graphene channel, which depends on the minimum sheet carrier concentration.

The probability of carrier transmission through the potential is given in ref. [98]. The carrier transmission,  $T_{mg}$ , through Ti–TiO<sub>x</sub>–graphene interface depends on the tunneling mechanisms and it has been modeled based on quantum-mechanical tunneling theory using the WKB approximation.

The above comprehensive physics-based calculation of  $R_c$  can be used as a confident reference for the values of this parameter in a device model. For compact modeling approaches, however,  $R_c$  in GFETs has been either extracted from experimental data-based methodologies<sup>[75–77,79]</sup> (cf. Section 4.2.3) or been considered as a model parameter whose value is obtained by fitting the experimental I-V curves (cf. Section 3.2). Furthermore, parameter extraction techniques based on test-structures or analysis of transport experimental data<sup>[81,89,111,112]</sup> have been developed toward obtaining an immediate  $R_c$  value. Further details of these extraction methodologies are provided in Section 4.2.3.

## 3. Transient Analysis

When a time-varying signal is applied to a GFET terminal, the dynamic operation of the device is strongly influenced by internal capacitive effects. Therefore, it is necessary to develop a large-signal model of intrinsic GFET capacitances. Various capacitive models for general FETs have been developed over the years. Basically, they can be categorized into two groups: 1) Meyer-like<sup>[113]</sup> and 2) charge-based capacitance models. The advantages and shortcomings of both model groups applied to conventional FETs have been widely discussed and implemented in circuit simulators.<sup>[114,115]</sup>

Meyer-like models are widely used in incumbent technologies because of their simplicity and fast computation. They assume that the intrinsic capacitances are reciprocal (i.e.,  $C_{ij} = C_{ji}$ ). Notably, this hypothesis might give unphysical results when dealing with some class of circuits (such as switched capacitor filters); furthermore, earlier models based on this assumption could not ensure charge conservation.<sup>[116,117]</sup>

Conversely, the charge-based models ensure both charge conservation and non-reciprocity of intrinsic capacitances in a FET. Owing to some corrections assembled by Ward and Dutton,<sup>[118]</sup> the charge-conservation issue was solved by introducing a capacitive matrix, which adds a bit of complexity. In refs. [11, 119–121] we have provided graphs of bias-dependent  $C_{dg}$  and  $C_{gd}$  for grapheneand MoS<sub>2</sub>-based FETs, showing that the reciprocity of capacitances in emergent 2D technologies cannot be assumed for all transistor operation regimes. However, most of the GFET capacitance models reported so far rely on the Meyer's reciprocity assumption without evaluating the implications of adopting it.<sup>[122–126]</sup> Therefore, a comparison of the RF performance prediction between the Meyer-like models against a charge-based approach is provided in ref. [119] indicating that significant errors could arise.

Considering all the aforementioned, we presented a largesignal model for the GFET elsewhere and summarized it in Section 3.1.<sup>[11,127]</sup> Thereafter, to illustrate the working of the model, we have presented the dynamic response of several circuits exploiting the graphene ambipolarity in Section 3.2. Later in Section 3.3, we considered significant non-ideal effects that must be modeled to enhance the predictive capability of the large-signal model. The effects include the impact of the trapped charges in Section 3.3.1 and the NQS effects owing to carrier inertia in Section 3.3.2. Dynamic SHE will be treated in the context of small-signal analysis later in Section 4.2.2. As for the large-signal case, dynamic SHE would need some adaptation, which is not yet investigated. Finally, to account for the impact of parasitic elements when a transient circuit analysis is performed, a parasitic network model of the GFET should be considered in the simulation. That will be discussed in the context of AC analysis in Section 4.2.3.

## 3.1. Large-Signal Model

Assuming a quasi-static (QS) operation, the entering terminal currents in the time domain can be expressed by considering that the charges per unit area at any time controlled by the time-varying terminal voltages, ( $v_G(t)$ ,  $v_B(t)$ ,  $v_D(t)$ , and  $v_S(t)$ ), are identical to those found if DC voltages ( $V_G$ ,  $V_B$ ,  $V_D$ , and  $V_S$ ) were used.

$$i_{\rm m}(t) = \frac{dQ_{\rm m}}{dt} + I_{\rm m} \tag{19}$$

www.advmat.de where *m* stands for G, D, S, and B which denote the top gate, drain, source, and back gate, respectively. The possible leakage current through the top and back insulators is neglected, that is,  $I_{\rm G} = I_{\rm B} = 0$ . In addition, to guarantee charge conservation,  $I_{\rm D} = -I_{\rm S} = I_{\rm DS}$ , where  $I_{\rm DS}$  is calculated according to

that is,  $I_{\rm G} = I_{\rm B} = 0$ . In addition, to guarantee charge conservation,  $I_{\rm D} = -I_{\rm S} = I_{\rm DS}$ , where  $I_{\rm DS}$  is calculated according to Equation (10). A four-terminal FET can be modeled using a set of 16 intrinsic capacitances, including 4 self-capacitances and 12 transcapacitances. The capacitance matrix is formed by these capacitances, where each element,  $C_{ij}$ , describes the dependence of the charge at terminal *i* with respect to a varying voltage applied to terminal *j*, assuming that the voltage at any other terminal remains constant. Therefore, Equation (19) can be written as

$$\begin{bmatrix} i_{G} \\ i_{D} \\ i_{S} \\ i_{B} \end{bmatrix} = \begin{bmatrix} C_{gg} - C_{gd} & -C_{gs} - C_{gb} \\ -C_{dg} & C_{dd} & -C_{ds} - C_{db} \\ -C_{sg} - C_{sd} & C_{ss} - C_{sb} \\ -C_{bg} - C_{bd} & -C_{bs} & C_{bb} \end{bmatrix} \begin{bmatrix} dv_{G}/dt \\ dv_{D}/dt \\ dv_{B}/dt \end{bmatrix} + \begin{bmatrix} 0 \\ I_{DS} \\ -I_{DS} \\ 0 \end{bmatrix}$$

$$C_{ij} = -\frac{\partial Q_{i}}{\partial V_{i}}, \ i \neq j; \ C_{ij} = \frac{\partial Q_{i}}{\partial V_{i}}, \ i = j. \qquad i, j = G, D, S, B$$

$$(20)$$

Each row must sum to zero for the matrix to be referenceindependent, and each column must sum to zero for the device description to be charge-conservative.<sup>[128]</sup> Notably, only 9 out of the 16 intrinsic capacitances are independent. In addition, we can take advantage of the relations between top- and back-gate capacitances,<sup>[11,129]</sup> namely  $C_{bd} = C_{gd}$  ( $C_b/C_t$ );  $C_{bs} = C_{gs}$  ( $C_b/C_t$ );  $C_{db} = C_{dg}$  ( $C_b/C_t$ );  $C_{sb} = C_{sg}$  ( $C_b/C_t$ );  $C_{gg} = -C_{bg}(C_t/C_b) + C_tWL$ ;  $C_{bg} = C_{gb} = -C_{bb}(C_t/C_b) + C_tWL$ ; reducing the independent set of intrinsic capacitances of a four-terminal GFET to only four; for instance,  $C_{gs}$ ,  $C_{gd}$ ,  $C_{dg}$ , and  $C_{sd}$ .

Considering all the aforementioned, the modeling of the dynamic response of a GFET requires a charge model relating the terminal charges to the terminal voltages. From the electrostatics given in Equation (2), the following relations are derived:<sup>[11]</sup>

$$Q_{\rm G} + Q_{\rm B} = -W \int_{0}^{\rm L} Q_{\rm net}(y) dy; \begin{cases} Q_{\rm G} = Q_{0} - \frac{C_{\rm t}W}{C_{\rm t} + C_{\rm b}} \int_{0}^{\rm L} Q_{\rm net}(y) dy \\ -Q_{\rm B} = Q_{0} + \frac{C_{\rm b}W}{C_{\rm t} + C_{\rm b}} \int_{0}^{\rm L} Q_{\rm net}(y) dy \end{cases}$$

(21)

where  $Q_0 = WLC_tC_b(V_G - V_{G0} - V_B + V_{B0})/(C_t + C_b)$ . The charge controlled by the drain and source terminals is calculated based on the Ward–Dutton linear charge partition scheme, which guarantees charge conservation<sup>[118]</sup>

$$Q_{\rm D} = W \int_{0}^{L} \frac{\gamma}{L} Q_{\rm net}(\gamma) d\gamma$$

$$Q_{\rm S} = -(Q_{\rm G} + Q_{\rm B} + Q_{\rm D}) = W \int_{0}^{L} (1 - \frac{\gamma}{L}) Q_{\rm net}(\gamma) d\gamma$$

(22)

Both terminal charges and intrinsic capacitances can conveniently be written using  $V_c$  as the integration variable, as it was done to model  $I_{DS}$  (cf. Section 2.1.2). Because  $I_{DS}$  is the same at any point y in the channel (by considering compensated generation/recombination processes), the equations required to evaluate the terminal charges and intrinsic capacitances are obtained from the drift-diffusion transport model as follows:

$$dy = \frac{\mu_{\rm LF}W}{I_{\rm DS}} \rho_{\rm sh}(V_{\rm c}) \frac{dV}{dV_{\rm c}} dV_{\rm c} - \frac{\mu_{\rm LF}}{\nu_{\rm sat}} \frac{d\psi}{dV_{\rm c}} | dV_{\rm c} |$$

$$y = \frac{\mu_{\rm LF}W}{I_{\rm DS}} \left( \int_{V_{\rm cs}}^{V_{\rm c}} \rho_{\rm sh}(V_{\rm c}) \frac{dV}{dV_{\rm c}} dV_{\rm c} \right) - \frac{\mu_{\rm LF}}{\nu_{\rm sat}} \left| \int_{V_{\rm cs}}^{V_{\rm c}} \frac{d\psi}{dV_{\rm c}} dV_{\rm c} \right|$$

(23)

where

$$\frac{dV}{dV_c} = 1 + \frac{d\psi}{dV_c} = 1 + \frac{C_q(V_c)}{C_t + C_b}$$

Т

$\mu_{LF}$

$V_{G0}$

$V_{B0}$

$R.W. R_dW$

Δ

Т

$\mu_{LF}$

$V_{G0}$

The drain current model presented in Section 2.1.2 is combined with the charge-based compact intrinsic capacitance description as shown in Equation (20) to assemble a large-signal model of GFETs. The modeling approach presented here has been validated against numerical simulations

a) Input parameters of the GFET - Device A

1300 cm<sup>2</sup>/Vs

300 K

0 V

-1.062 V

0.140 eV

6.6·10<sup>5</sup> m/s

1.1 kΩ·µm

b) Input parameters of the GFET - Device B

2200 cm<sup>2</sup>/Vs

300 K

1 V

0 V

(Figure 9c)<sup>[11]</sup> as well as with experimental data from fabricated GFETs.[127]

## 3.2. Dynamic Response of GFET-Based RF Applications

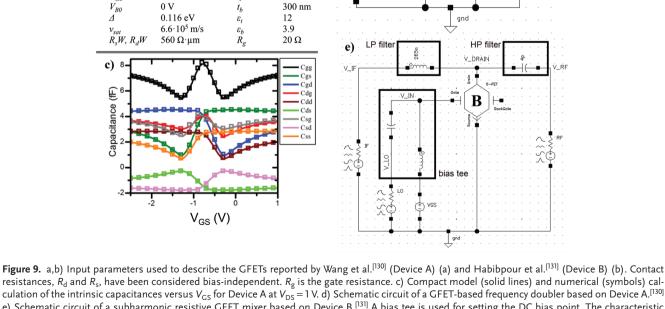

To demonstrate the predictive capabilities of the large-signal model presented,<sup>[127]</sup> we consider various exemplary circuits, namely: the frequency doubler and the subharmonic mixer.<sup>[130,131]</sup> The GFET used in each of the circuits is referred as device A and B (with their corresponding parameters given in Figure 9a,b), respectively. In Figure 9c, a set of independent intrinsic capacitances for the device A is plotted as a function of the gate voltage, showing a clear non-linear behavior of the GFET around the Dirac voltage. It can be observed that the Meyer's reciprocity does not hold.[11]

A graphene-based frequency doubler leverages the quadraticlike transfer characteristic (I<sub>DS</sub> vs V<sub>GS,e</sub> curve) of a GFET. If such a transfer characteristic is not perfectly parabolic and/or symmetric, which is the practical case, the output voltage contains the doubled frequency and other higher-order harmonics, resulting in harmonic distortion. As for device A configured in the topology depicted in Figure 9d, with the nearly symmetric transfer characteristic around  $V_{\text{Dirac}} = -1.15$  V shown in

VBB

VDD

Vout

G-FET

d)

Vin

500 nm

840 nm

300 nm

5 nm

12

3.9

$20 \Omega$

1 µm

5 nm

20 µm

300 nm

I

W

t,

th

$\mathcal{E}_{t}$

$\varepsilon_{h}$

R

L

W

t,

$t_b$

resistances,  $R_d$  and  $R_s$ , have been considered bias-independent.  $R_g$  is the gate resistance. c) Compact model (solid lines) and numerical (symbols) calculation of the intrinsic capacitances versus  $V_{GS}$  for Device A at  $V_{DS} = 1 V$ . d) Schematic circuit of a GFET-based frequency doubler based on Device A.<sup>[130]</sup> e) Schematic circuit of a subharmonic resistive GFET mixer based on Device B.<sup>[131]</sup> A bias tee is used for setting the DC bias point. The characteristic impedance is 50 Ω. c) Reproduced with permission.<sup>[1]</sup> Copyright 2016, IEEE. d,e) Reproduced with permission.<sup>[127]</sup> Copyright 2016, IEEE.

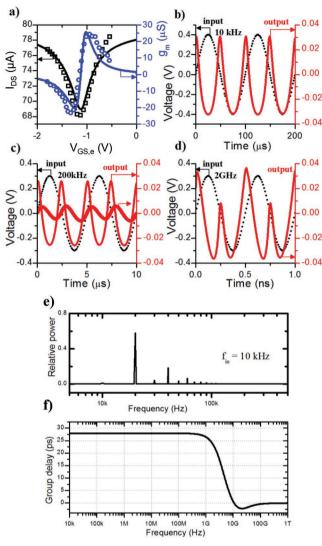

**Figure 10.** a) Experimental measurements (symbols) and simulations (solid lines) of the DC transfer characteristics and the extrinsic transconductance of a GFET-based frequency doubler.<sup>[130]</sup> The device is biased at  $V_{DS,e} = 1 \text{ V}$ ,  $V_{BS,e} = 40 \text{ V}$ , and  $V_{GS,e} = -1.15 \text{ V}$ . b) Input and output waveforms considering an input frequency of  $f_{in} = 10 \text{ kHz}$  and amplitude A = 400 mV. c) Input and output waveforms considering an input frequency of  $f_{in} = 200 \text{ kHz}$  and amplitude of A = 300 mV. A thicker solid line shows the output waveform when a parasitic capacitance ( $C_{pad} = 600 \text{ pF}$ ) is placed between the drain/source and the back gate, considering the effect of the electrode pads. d) Input and output waveforms considering an input frequency of  $f_{in} = 2 \text{ GHz}$  and amplitude of A = 300 mV. e) Power spectrum obtained via Fourier transforming the output signal shown in (b). f) Group delay versus frequency of the GFET-based frequency doubler. a–f) Reproduced with permission.<sup>[127]</sup> Copyright 2016, IEEE.

**Figure 10**a, the output waveforms after considering different input frequencies are shown in Figure 10b–d. For the input signal with amplitude *A* and lowest frequency,  $f_{in} = 10$  kHz, the output waveform consists of the doubled frequency with amplitude  $\approx A/10$ , with a clear distortion coming from other higher order harmonics (Figure 10b). A Fourier transform of such waveform is shown in Figure 10e, revealing that 60% of the output RF power is concentrated at the doubled frequency of 20 kHz.

When the input signal is increased up to  $f_{\rm in} = 200$  kHz and beyond, a significant decay of the output signal amplitude was observed in the experiment,<sup>[130]</sup> with a voltage gain of ~ A/100 likely because of the presence of a parasitic capacitance (estimated in  $C_{\rm pad} = 600$  pF) between the GFET sourcedrain terminals and its back gate. When including the  $C_{\rm pad}$ , the predicted output waveform is similar to that in the experiment for an input frequency of 200 kHz (Figure 10c). If the input frequency is increased further to 2 GHz, as shown in Figure 10d, the output waveform displays the doubled frequency, although with a greater distortion because the group delay is not constant with the frequency according to Figure 10f, indicating that the phase is not linear with the frequency.

Furthermore, with the use of a single GFET (Figure 9e), a subharmonic mixer can be designed to take advantage of the device non-linearity. This way, the device is fed with two different frequencies (the local oscillator, LO, signal at  $f_{\rm LO}$  and the RF signal at  $f_{\rm RF}$ ) and a mixture of several frequencies appears at the output port, including both original input frequencies; the sum of the input frequencies; the difference between the input frequencies; the intermediate frequency (IF),  $f_{\rm IF}$ ; and other intermodulations.<sup>[132]</sup> According to the graphene-based mixer topology shown in Figure 9e, the LO signal and DC bias are applied to the gate port through a bias-tee, whereas the RF signal is applied to the drain of the GFET through a high-pass filter, and the IF is extracted with a low-pass filter, both assumed with cut-off frequencies of 800 and 30 MHz, respectively.

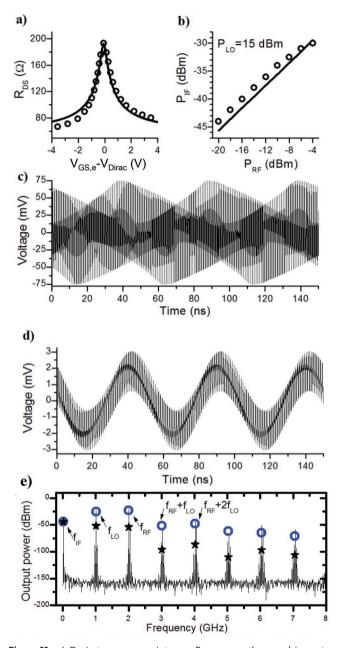

The drain-to-source resistance,  $R_{\rm DS} = V_{{\rm DS},e}/I_{\rm DS}$ , versus the gate bias is shown in **Figure 11**a. To reach subharmonic operation, the device is biased at  $V_{{\rm GS},e} = V_{{\rm Dirac}} = 1$  V through a bias tee. In contrast, Figure 11b shows the mixer IF output power versus the RF input power, where a near constant conversion loss rate of  $\approx 25$  dB is obtained. The transient evolution of the signal collected at the drain is shown in Figure 11c, as well as the signal collected at the IF port (Figure 11d), which oscillates as expected at  $f_{\rm IF} = |f_{\rm RF} - 2f_{\rm LO}| = 20$  MHz given that  $f_{\rm LO} = 1.01$  GHz and  $f_{\rm RF} = 2$  GHz. Finally, the spectrum of the signal collected at the drain is presented in Figure 11e, with an output power of  $\approx -49$  dBm. Lower levels of odd harmonics are observed as well, which are attributed to the non-perfect symmetry of  $R_{\rm DS}$  versus  $V_{\rm GS,e}$ .

# 3.3. Non-Ideal Effects for Enhancing the Large-Signal Model Prediction Capability

A brief description of the dynamic trap-related phenomenon in GFETs is presented in Section 3.3.1. The implementation of this module into the GFET modeling framework presented in this work is still an ongoing effort; hence, the corresponding subsection should be considered a useful guide for approaching this development. A systematic study on NQS effects in GFETs is provided in Section 3.3.2.

# 3.3.1. Dynamic Trap Model

Trapping and detrapping dynamic processes in MOS-like transistors can be characterized by their corresponding capture and

Figure 11. a) Drain-to-source resistance,  $R_{DS}$ , versus the overdrive gate voltage, with  $R_{DS} = R_d + R_s + R_{ch}$ , where  $R_{ch}$  is the channel resistance, and  $R_{\rm d}$  and  $R_{\rm s}$  are the extrinsic contact resistances at the drain and source sides, respectively. Solid lines correspond to simulations and the symbols to the experimental results.<sup>[131]</sup> b) IF output power as a function of the RF input power. The device is biased at the Dirac voltage  $V_{GS,e}$  =  $V_{\text{Dirac}}$  and  $P_{1,0} = 15$  dBm. c) Transient evolution of the signal collected at the drain at  $V_{GS,e} = V_{Dirac}$ . The following conditions have been assumed:  $P_{LO} = 15$  dBm and  $f_{LO} = 1.01$  GHz;  $P_{RF} = -20$  dBm and  $f_{RF} = 2$  GHz. d) Transient evolution of the IF signal collected at the IF port under the same conditions as in (c). The separation between peaks is 50 ns, which corresponds to  $f_{IF} = |f_{RF} - 2f_{LO}| = 20$  MHz. e) Simulated spectrum (solid lines) of the signal collected at the drain (shown in (c)) and the measured power peaks (blue circles) reported in ref. [131]. The stars correspond to the simulation results of power peaks of the signal collected at the IF port (shown in (d)). a-e) Reproduced with permission.<sup>[127]</sup> Copyright 2016, IEEE.

emission time constants,  $\tau_c$  and  $\tau_e$ , respectively. These phenomena can occur over a wide time span depending on the location of the traps centers within the device (cf. Section 2.2.1). as well as on the bias and temperature conditions.<sup>[133,134]</sup> In devices with high- $\kappa$  oxides, for example, GFETs, the dynamic performance is strongly affected by the capture and release of carriers,<sup>[35,135,136]</sup> mainly located at the gate oxide and channel interfaces, because the trap-induced shift of the channel potential modify the bias conditions (transfer curve hysteresis) to achieve specific dynamic characteristics.[35,136] Additionally, trapping phenomena have an impact on the device measurement history, that is, on the initial state of shielding of the channel potential from the gate-source voltage. This impact could not be reduced by a technology-dependent quiescent time approach,<sup>[51,81]</sup> if either  $\tau_c$  or  $\tau_e$  (or a combination of both) is larger than the quiescent pulse duration. Hence, the dynamic modeling approach for graphene transistors should consider the trap time constants for a correct description and projection of the device performance. Furthermore, a reliable compact model considering a description for trap mechanisms can aid the technology development by revealing the device dynamic performance affected by traps under different pulse biasing conditions, as demonstrated in other emerging technologies.<sup>[137,138]</sup> The latter can be immediately exploited in specific application scenarios, for example, high-speed GFET-based modulators designs,<sup>[139,140]</sup> and it can be boosted by an accurate modeling of the dependence of the trap-affected/reduced device performance on the pulse biasing conditions.

www.advmat.de

Trap dynamics in graphene transistors have been systematically characterized<sup>[141,142]</sup> using silicon technology-based models<sup>[143]</sup> yielding the traps activation energy distributions and trap time constant distributions of the capture and emission processes. Individual values of trap-related time constants have been experimentally characterized in different GFET technologies ranging from few nanoseconds to the order of few hours.<sup>[32,33,144-146]</sup> Trap time constants have been obtained by fitting the transient current response over specific non-quiescent conditions with constant pulse widths using empirical exponential models.<sup>[32,33,144,145]</sup> A capture process is usually related to such extracted trap time constants in these cases; hence, the emission time constants are ignored. Studies with different pulse duration reveal both  $\tau_c$  and  $\tau_e$ , as demonstrated in ref. [146] where the latter is obtained with pulses larger than the time required for an apparent initial steady-state of the current.

Currently, physics-based models for  $\tau_c$  and  $\tau_e$  in GFETs have not been reported in the literature. However, previously developed high- $\kappa$  dielectric MOS-models of oxide traps, for example, a non-radiative multiphonon model<sup>[147]</sup> (already applied to other 2D transistor technologies),<sup>[148]</sup> can be adapted to GFETs because statistical similarities between trapping processes in the latter and in incumbent technologies have already been observed.<sup>[141,142]</sup> This model predicts  $\tau_c$  and  $\tau_e$  as a function of the position and energy of the trap, applied bias, and temperature.

A numerical device simulation solution, enabled by the drift-diffusion-based description of transport in graphene transistors,<sup>[149,150]</sup> can be developed by considering the trapassisted phenomena, including  $\tau_{c/e}$ -dependent capture and emission rates, in both the Poisson's equation and the

continuity equation<sup>[151,152]</sup> as already implemented in other drift-diffusion-based simulators describing different transistor technologies.<sup>[152–155]</sup> In contrast, an immediate approach to adapt the compact graphene transistor model considering traps in a static regime described in Section 2.2.1 for the dynamic description can be conducted by defining the trap density  $N_{\rm tr}$ in Equation (12) in terms of the steady-state trap density  $N_{\rm tr.ss}$ along with  $\tau_c$  or  $\tau_e$ , as implemented previously in a different compact model.<sup>[156]</sup> The challenging characterization of  $N_{tr,ss}$ has been overcome in ref. [156] using an empirical function depending on the vertical fields and some fitting parameters. An improvement of the compact GFET model discussed in this work (cf. Section 2.1), including the dependence of both lateral and vertical fields as well as  $\tau_c$  and  $\tau_e$  in the definition of  $N_{\rm tr}$  is left for future studies. Alternatively, for circuit design purposes, a practical approach considering an adjunct trap network, as demonstrated in studies of emerging transistor technologies,[58,137,138,157] with different time constants defined by RC networks can be an option to include directly in the compact model the impact of the different capture and emission trapping processes within the device.<sup>[39,137,138]</sup>

## 3.3.2. Non-Quasi-Static Large-Signal Model

Depending on the input frequency of the time-varying signal, two operating regimes can be distinguished, QS and NQS. In the QS regime, the fluctuation of the varying terminal voltages is sufficiently slow such that the channel charge can follow the voltage variations. This regime applies whenever the transition time for the voltage to change is larger than the transit time of the carriers from source to drain. Contrarily, the NQS regime where carrier inertia effects are important should be considered. When dealing with circuit simulations, assuming a QS regime is not appropriate for long-channel GFETs operating at HFs or when the load capacitance is extremely small.<sup>[128,158]</sup> Applications of QS approach could result in important errors when predicting phase margins or the stability of wideband amplifiers.<sup>[159]</sup>

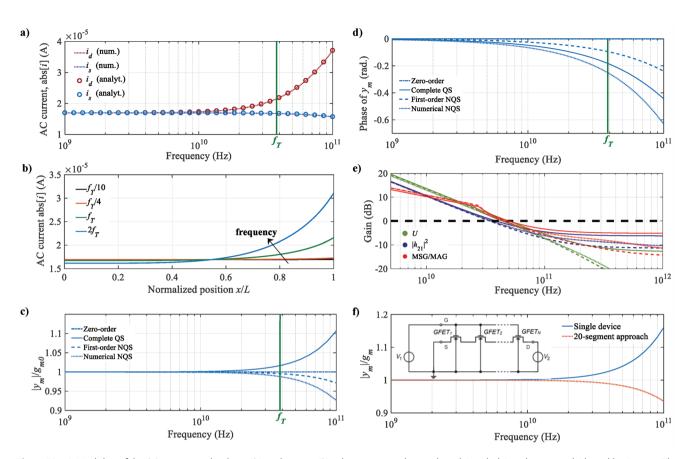

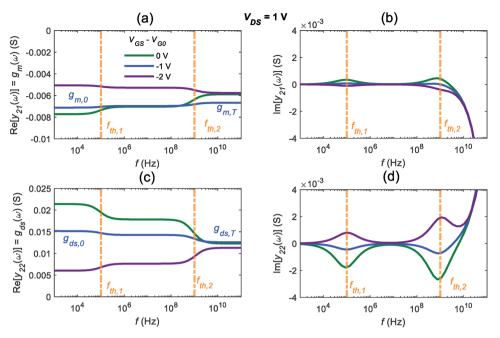

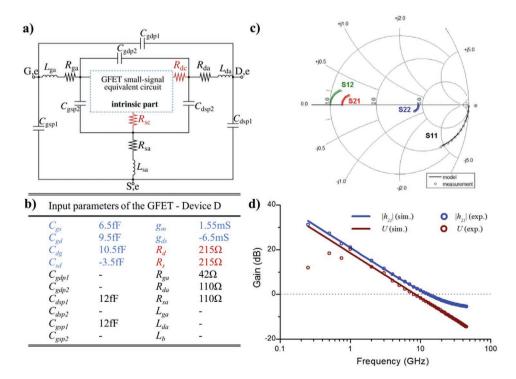

A straightforward approach for modeling a transistor at speeds where the QS regime breaks down involves splitting the channel length in many shorter sections; thus, the QS approach still holds within each section.<sup>[128,160,161]</sup> To track the breakdown of the QS regime, we consider the frequency-dependent admittance  $y_m = y_{dg} - y_{gd}$  as a convenient indicator of the electrical gate control on the transistor channel over frequency. Thus, a decrease of  $|y_m|$  is interpreted as the loss of the gate control over the channel charge because of the significant carrier inertia originated at HF.<sup>[128,162]</sup> Considering the 1 µm-long prototype GFET described in Figure 12a, a simulation of normalized  $|y_m|$  from the QS model is shown in Figure 13f. The selected bias to perform the calculation is  $V_{\rm G}$  = 1.5 V,  $V_{\rm D}$  = 1 V, and  $V_{\rm B} = V_{\rm S} = 0$  V. The result is compared with that obtained after connecting 20 identical GFETs of length L/20 = 50 nm in series (sharing all the same gate, as shown in the inset of Figure 13f), where the array effectively allows the capture of NQS effects. At medium frequencies, both approaches, QS and NQS, predict the same normalized |ym|. However, the upward-going magnitude of normalized |y<sub>m</sub>| predicted by the QS model for the 1 µm-long GFET working at HF is clearly unrealistic, as it

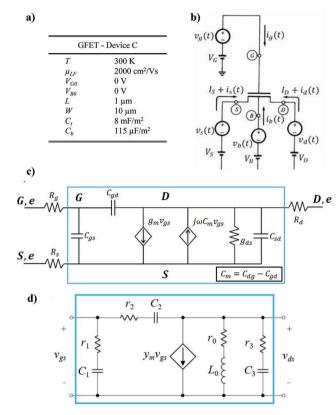

**Figure 12.** a) Input parameters used to describe a prototype GFET. b) Schematic of a four-terminal FET operating under small-signal regime showing the terminal DC and AC voltages as well as currents. To guarantee charge conservation, the sum of the terminal currents must be zero; thus,  $I_D = -I_S$ , where the DC top- and back-gate currents are  $I_G = I_B = 0$ ; and  $i_g(t) + i_b(t) + i_d(t) + i_s(t) = 0$ . c) QS charge-based smallsignal model suited to three-terminal GFETs. The equivalent circuit of the intrinsic device is framed in blue. d) Equivalent circuit of a GFET in two-port configuration describing the first-order NQS behavior using lumped elements. b,d) Reproduced with permission.<sup>[162]</sup> Copyright 2020, IEEE. c) Reproduced with permission.<sup>[119]</sup> Copyright 2017, IEEE.

suggests an enhancement in the forward gate-to-drain action. This behavior results contrary to the expectation that, at such frequencies, control of the gate on the drain current is gradually lost due to the carrier inertia in the graphene channel. These predictions for GFETs are in qualitative agreement with the NQS studies that have been conducted for conventional silicon-based MOSFETs.<sup>[128,159]</sup>

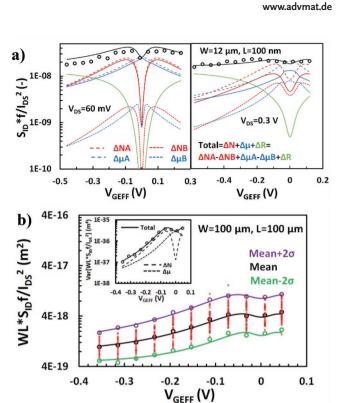

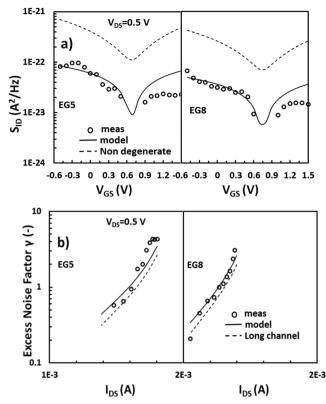

# 4. AC Analysis