REDES DEPENDIENTES DE LA TEMPORIZACIÓN BASADAS EN MÉTODOS DE SINCRONIZACIÓN ULTRA-PRECISOS

S O S U S.

R

TIME-SENSITIVE NETWORKS BASED ON ULTRA-ACCURATE SYNCHRONIZATION MECHANISMS

JORGE SÁNCHEZ GARRIDO

## UNIVERSIDAD DE GRANADA

## REDES DEPENDIENTES DE LA TEMPORIZACIÓN BASADAS EN MÉTODOS DE SINCRONIZACIÓN ULTRA-PRECISOS

## TIME-SENSITIVE NETWORKS BASED ON ULTRA-ACCURATE SYNCHRONIZATION MECHANISMS

JORGE SÁNCHEZ GARRIDO

Directores antonio javier díaz alonso eduardo ros vidal

Programa de Doctorado TECNOLOGÍAS DE LA INFORMACIÓN Y LA COMUNICACIÓN

Departamento de Arquitectura y Tecnología de los computadores Escuela Técnica Superior de Ingenierías en Informática y Telecomunicaciones ATC TIC-117

Noviembre 2020

Editor: Universidad de Granada. Tesis Doctorales Autor: Jorge Sánchez Garrido ISBN: 978-84-1306-766-7 URI: <u>http://hdl.handle.net/10481/66660</u>

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of the University of Granada's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink.

Jorge Sánchez Garrido:

*Redes dependientes de la temporización basadas en métodos de sincronización ultra-precisos ,* © Creative Commons Attribution-NonCommercial-NoDerivs 3.0 License Noviembre 2020

A mi madre, por todo ...

Y a mi familia: a mi padre y a mi hermano, que se encuentra en estos mismos quehaceres, a mi querido abuelo, y a mis tíos que siempre estuvieron al lado.

#### RESUMEN

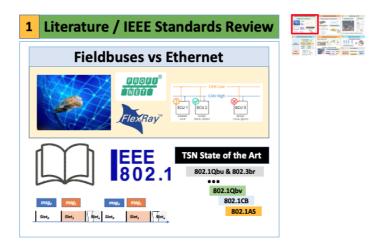

Las comunicaciones deterministas son un requisito esencial en múltiples aplicaciones, tales como las plantas industriales, las redes de automoción, o los sistemas de aeroespacial. Los buses de campo han venido empleándose de forma tradicional en estos ámbitos para suplir sus necesidades de comunicación e intercambio de datos. A modo de ejemplo, algunos protocolos muy conocidos para estos ámbitos son los buses CAN o FlexRay en automoción, o Spacewire para los vehículos espaciales. Algunas de estas soluciones pueden ser propietarias o necesitar del uso de equipamiento especializado. Por lo tanto, el panorama existente en las tecnologías de buses de campo es bastante diverso, con una gama de soluciones que puede incluir interfaces que van desde lo puramente analógico (HART) hasta aquéllas que son completamente digitales. Estas últimas suelen emplear interfaces de tipo serie y, en particular, tecnologías Ethernet. De hecho, existe una fuerte tendencia a implementar buses de campo usando bloques funcionales de Ethernet estándar (como en el caso de Profinet). Estas soluciones compensan la falta de capacidades de comunicación determinista de las interfaces Ethernet convencionales que, sin embargo, son altamente eficientes para transmitir datos con un ancho de banda considerable, aunque únicamente pueden realizar su entrega con un servicio de tipo best-effort (de mejor esfuerzo). No obstante, el giro hacia las interfaces basadas en Ethernet para implementar buses de campo ha demostrado que esta filosofía tiene ventajas inherentes, como mayor rendimiento y una compatibilidad entre dispositivos más amplia. Esto, a su vez, fue el germen de un cambio global que buscaba definir interfaces Ethernet genéricas basadas en estándares que fueran deterministas. En consecuencia, las principales repercusiones de estos cambios se han visto, en primer lugar, con la aparición de la conmutación de audio y vídeo para Ethernet (audio/video bridging - AVB), a la que posteriormente siguieron las redes sensibles a la temporización (TSN).

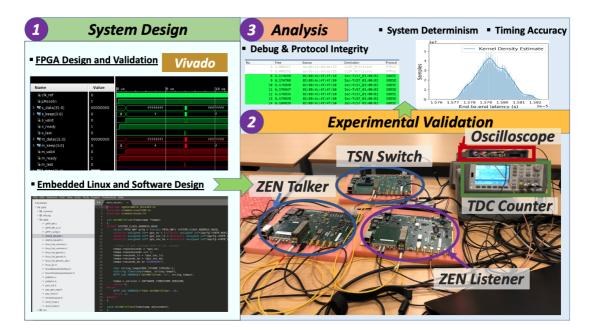

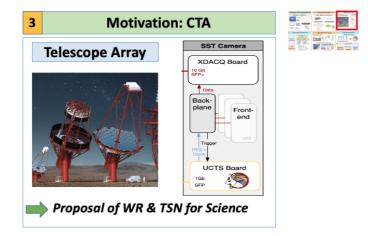

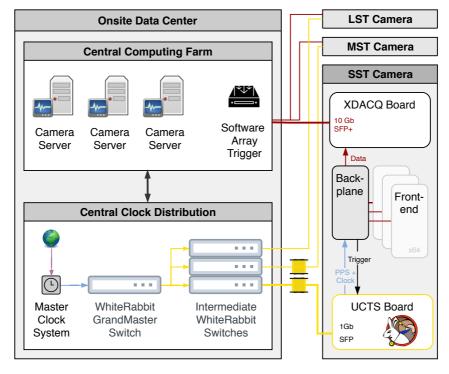

En esta tesis se exploran aspectos avanzados en cuanto a la construcción, implementación y validación de sistemas TSN. De este modo, en la Parte I, se le proporciona al lector una descripción general de las tecnologías y especificaciones principales que gobiernan las redes TSN. Asimismo, ponemos en contexto el uso y la definición de perfiles para TSN, al tiempo que enfatizamos su papel fundamental como garantes de la adopción generalizada de TSN en múltiples industrias y aplicaciones, al proporcionar las "plantillas" que definen de forma maestra el diseño y parámetros que debe cumplir un sistema TSN para adaptarse a una aplicación determinada. A continuación, presentamos las metodologías experimentales, herramientas, material de laboratorio, y el diseño de los bancos de pruebas que utilizamos en las etapas de desarrollo y caracterización experimental. De este modo, conseguimos construir sistemas TSN convergentes al combinar todos estos elementos. La convergencia de flujos de datos en TSN es la propiedad fundamental que llevará al eventual reemplazo de los buses de campo, dado que los sistemas TSN pueden manejar tanto datos críticos, como flujos best-effort, y protocolos de sincronización simultáneamente. En este contexto, también desglosamos un caso de uso con la sincronización de White Rabbit (WR) en el Array de Telescopios de Cherenkov (CTA) como una motivación en la que se ilustra cómo al integrar esta tecnología con TSN se posibilita el despliegue de los mismos para aplicaciones científicas.

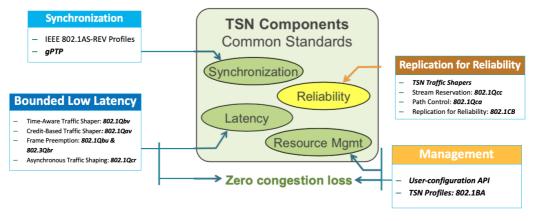

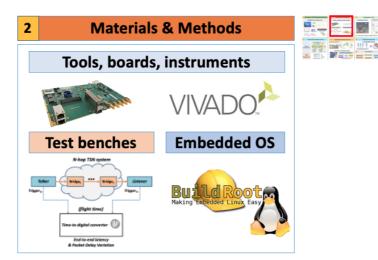

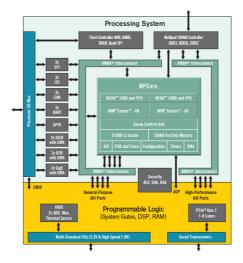

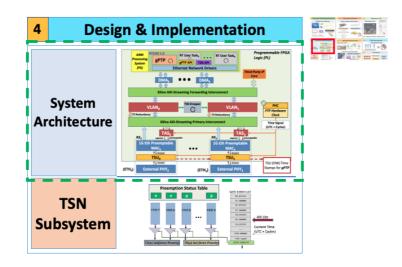

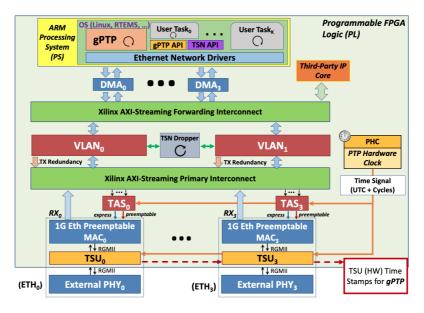

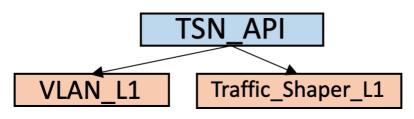

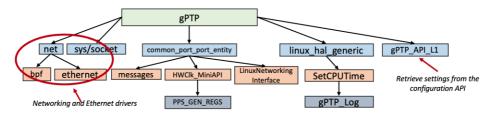

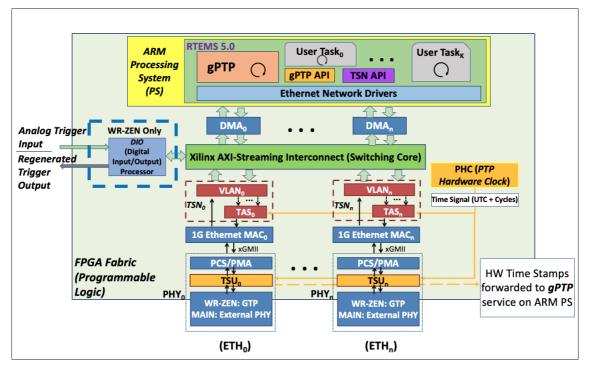

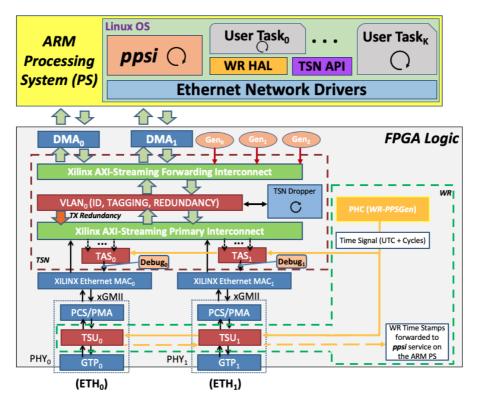

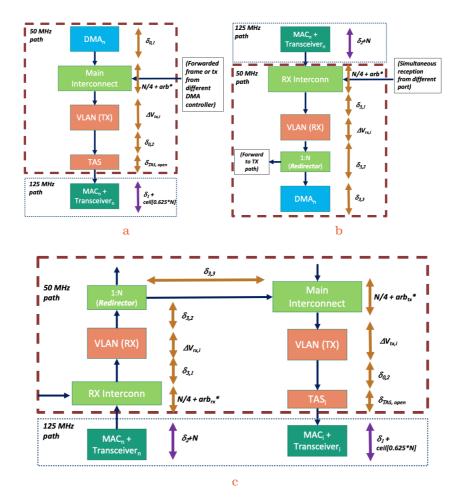

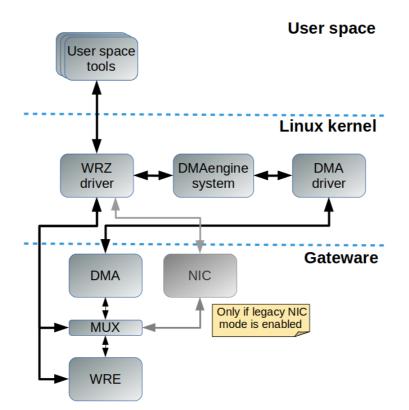

La Parte II de la memoria se dedica al desarrollo e implementación del sistema TSN. De este modo, presentamos las plataformas hardware empotradas y las placas de desarrollo de nuestro sistema, que están basadas en los dispositivos Zynq-7000 de Xilinx: la placa WR-ZEN y la placa Main. Además, también desglosamos su arquitectura software y hardware durante esta sección. Comenzamos con los diferentes subsistemas FPGA que se combinan en nuestro diseño para construir el nodo TSN (Ethernet, sincronización, sistema de conmutación, y los propios módulos de TSN), para seguidamente pasar a examinar los elementos software que les proporcionan soporte (sistema operativo, interfaces de programación, drivers de red, ...). Al diseño de los componentes del sistema TSN se les dedica especial atención, con un capítulo separado en el que se explica de forma detallada el diseño del clasificador de tráfico (TAS), el módulo de VLAN, la MAC de Ethernet y el TAS mejorados con la funcionalidad de interrupción de tramas (frame preemption), así como los módulos para la redundancia. Esto, además, nos llevó a diseñar una arquitectura genérica que es compatible con las principales funcionalidades y componentes de TSN que se sustenta sobre un diseño que hace un uso moderado de los recursos de la FPGA: 802.1AS (gPTP), 802.1Qbv (TAS), 802.1Qbu (TAS con preemption), 802.3br (MAC de Ethernet con preemption), 802.1CB (transmisiones redundantes), 802.1Q (etiquetado con VLAN e identificación de flujos de tráfico).

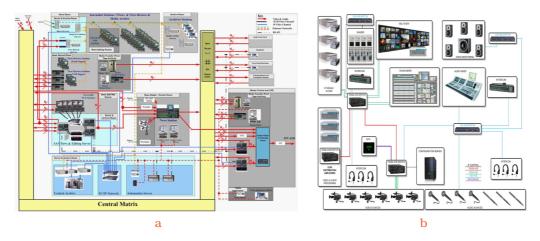

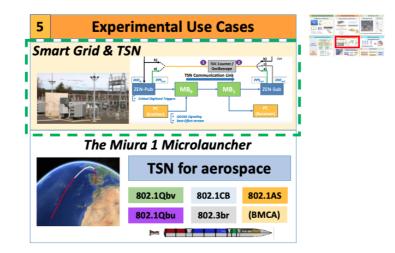

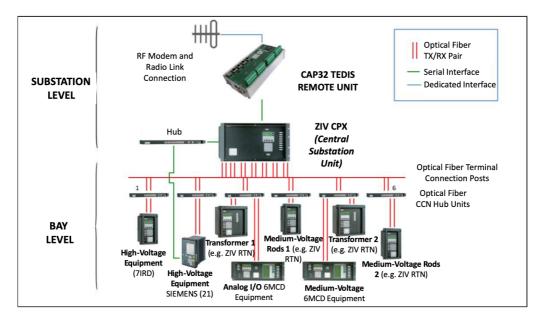

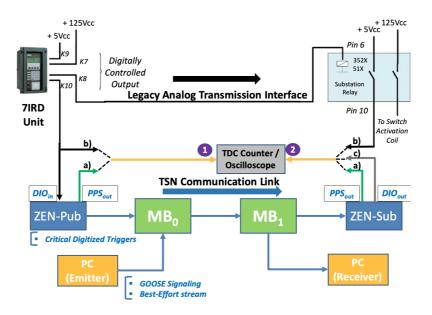

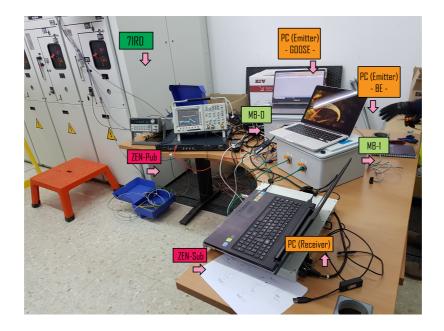

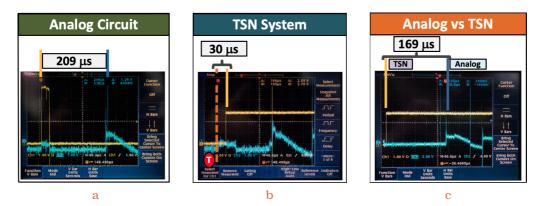

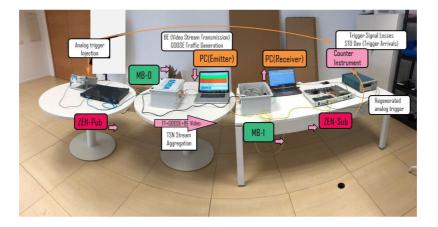

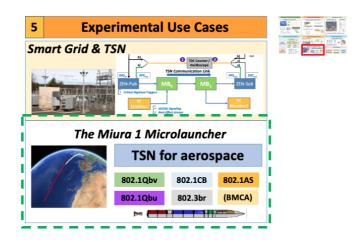

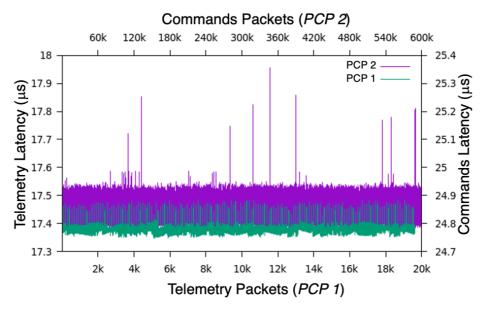

Nuestros casos de uso experimentales se detallan en la Parte III, donde aplicamos TSN en escenarios industriales y de aeroespacial. Comenzamos explorando la aplicación de TSN a una subestación eléctrica, que representa nuestro caso de uso en industrial. En este escenario, procedimos a reemplazar las interfaces de señalización analógica de la subestación por un sistema TSN, el cual también era capaz de agregar todos los datos y protocolos presentes en la subestación. Esto permitió verificar que era posible emplear una red TSN para este escenario de forma efectiva, al ser capaz de entregar los datos críticos de manera más rápida y con mayor fiabilidad que las interfaces convencionales de la subestación. De modo adicional, también establecimos que el determinismo del sistema estaba condicionado por la configuración del usuario. También hemos realizado la implementación de un caso de uso prometedor en aeroespacial al diseñar e implementar los nodos de aviónica del microlanzador Miura 1. En este marco, analizamos las principales consideraciones para diseñar dicho sistema de aviónica, presentamos su arquitectura, y caracterizamos su rendimiento de manera exhaustiva. Como resultado, demostramos que nuestra implementación de TSN puede reemplazar de forma eficaz a los buses de campo habituales en los vehículos para espacio, que podrían quedar desplazados en favor de una solución basada en componentes comerciales (COTS). Además, aprovechamos el buen funcionamiento del sistema en nuestros resultados para hacer una primera propuesta de un perfil de TSN para espacio.

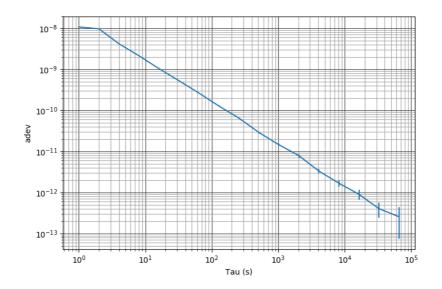

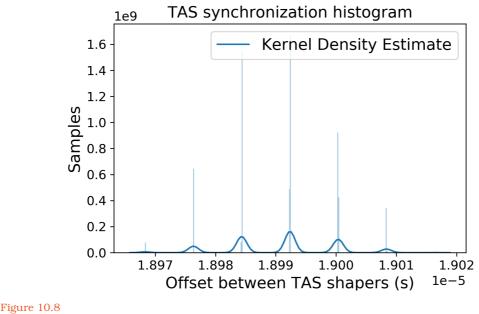

La integración experimental de la sincronización WR con el sistema de TSN se detalla en la **Parte IV** de la memoria, en donde se dedica un capítulo entero a presentar la investigación conjunta que se llevó a cabo con los investigadores de la Universidad Técnica de Dinamarca (DTU) durante la estancia del doctorado. Una parte importante de la estancia en DTU tuvo como objetivo estudiar la producción automática de parámetros de configuración para sistemas de TSN con herramientas especializadas. De este modo, en el capítulo se explica el desarrollo de la arquitectura "híbrida" con WR y la posterior caracterización de sus retardos internos de procesamiento, cuyo conocimiento era necesario para usar estas herramientas. Seguidamente, presentamos resultados preliminares en los que llegamos a la conclusión de que, a pesar de que se ha conseguido integrar la sincronización WR de forma exitosa con el sistema TSN, todavía hacen falta mejoras adicionales en nuestra arquitectura para mejorar su determinismo. Ésta será una de las principales áreas a cubrir en el trabajo futuro.

La **Parte V** muestra las conclusiones del trabajo de la tesis. De este modo, se enfatiza el haber realizado la implementación exitosa de un sistema TSN determinista basado en una arquitectura para FPGA que es altamente personalizable a la vez que adaptable, por lo que se puede ajustar y parametrizar a múltiples dispositivos y escenarios. En este contexto, cabe destacar la realización con éxito de casos de uso para las Smart Grids y para la aviónica del microlanzador del Miura 1. También se han mostrado resultados preliminares de una integración experimental con WR para explorar la posible aplicación de sistemas TSN en infraestructuras científicas, así como otros aspectos avanzados en relación con la generación automática de parámetros de configuración. Se concluye con una evaluación del nivel general de cumplimiento de los objetivos iniciales del trabajo y proponiendo una hoja de ruta para la mejora y actualización del sistema en el trabajo futuro. Por último, hemos incluido algunas consideraciones en los Apéndices sobre temas seleccionados relacionados con el desarrollo de drivers de red en entornos Linux empotrados.

#### ABSTRACT

Deterministic communications are an essential requirement for a variety of different application domains, such as the industrial plants, the automotive networks, or the aerospace systems. Traditionally, they have relied on the use of specialized fieldbuses to fulfill their communication needs. Some well-known examples are the CAN or the FlexRay buses for the automotive, or Spacewire for space vehicles. Some of these solutions are either proprietary or may require that they be used in combination with specialized equipment. Hence, the landscape of fieldbus communications is fairly diverse, presenting a range of differing solutions that range from the purely analog interfaces (e.g., HART) all the way to the fully digital ones. These latter cases typically make use of serial digital interfaces, and particularly there is a growing trend that seeks to build functioning implementations of different subtypes of fieldbuses out of standard Ethernet components (e.g., Profinet). These solutions make up for the lack of deterministic communication capabilities of ordinary Ethernet interfaces, which can do a great job at transmitting substantial amounts of data with large throughputs, although they can only provide a best-effort type of service for the delivery of data. Nonetheless, the shift towards Ethernetbased interfaces for the construction of fieldbuses has made the community realize that their use has apparent advantages, such as enhanced performance and streamlined compatibility and integration. This in turn was the germ of a larger shift towards the definition of generic, standard-based deterministic Ethernet interfaces. Consequently, this has materialized into the emergence of audio/video bridging (AVB) first, and then it was followed by the upgrade of time-sensitive networking (TSN).

This thesis explores advanced topics with respect to the construction, implementation, and validation of TSN systems. Hence, in *Part I*, we provide the reader with an overview of the main technologies and specifications that lie at the foundation of TSN networks. We also introduce the use and definition of profiles for TSN and emphasize their pivotal role in ensuring that the adoption of TSN will be widespread in multiple industries and applications, as they provide well-defined "templates" tailored to the requirements of a specific application domain. After that, we present the experimental methodologies, tools, laboratory material, and the layout of the test benches that we used during the development and experimental characterization stages. We built convergent TSN network systems with the use of these elements. This convergence is the fundamental property that will allow the eventual replacement of fieldbuses. Hence, TSN networks can handle critical data, best-effort traffic, and timing synchronization protocols simultaneously. In this context, we also introduce a motivational case with White Rabbit (WR) synchronization in the Cherenkov Telescope Array to illustrate how an integration with TSN could pave the way for the use of TSN networks for scientific infrastructures.

**Part II** of the manuscript is devoted to the implementation and development of our TSN system. We introduce our embedded hardware platforms and development boards based on the Zynq-7000 devices from Xilinx: the WR-ZEN and the Main Board. Furthermore, we present the main software and hardware components of our architecture in this section.

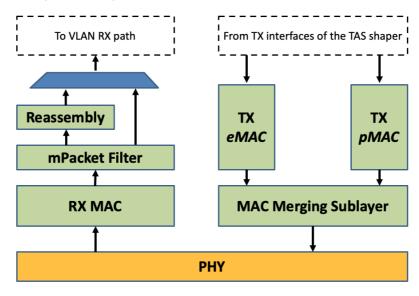

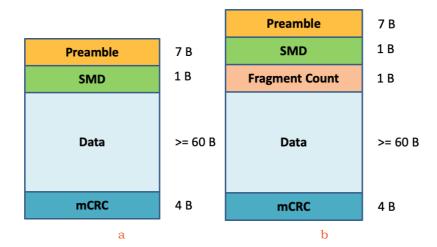

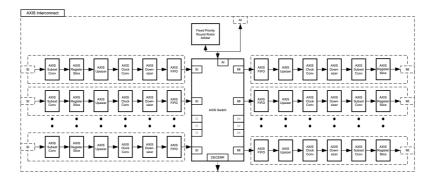

We start by looking at the various FPGA subsystems that have be combined to build a TSN node (Ethernet, timing, switching, and the TSN cores themselves), and then we examine the corresponding software elements for supporting them (the operating system, application programming interfaces, network drivers, ...). We make special emphasis in the description of the implementation, design, and construction of the elements of the TSN system by devoting a specialized section for their documentation. This is where we provide an in-depth explanation of the design of the time-aware traffic shaper (TAS), the VLAN module, the preemptable Ethernet MAC, the preemptable TAS, and the modules for the seamless redundancy feature. Hence, we present the design of a generic architecture with the capability for supporting the main subcomponents of TSN while making moderate use of FPGA resources: 802.1AS (gPTP), 802.1Qbv (TAS), 802.1Qbu (preemptable TAS), 802.3br (preemptable MAC), 802.1CB (seamless redundancy), 802.1Q (VLAN-tagging and traffic identification).

We present our experimental use cases with TSN in the industrial and aerospace domains in Part III. We start by exploring the application of TSN to an electrical substation. This is our industrial case where we replace the analog signaling interfaces of the substation with a TSN system that can also aggregate all the substation protocols and data that are present in this scenario. We verified that a TSN system could be put to this use effectively as it could deliver critical data faster and more reliably than the traditional substation interfaces. In addition, we found that the attainable determinism of the system was dependent on the user settings. We also present a promising use case for aerospace in this part of the manuscript: the design and implementation of the avionics nodes of the Miura 1 microlauncher. In this framework, we show the main design considerations of the system, present its architecture, and carry out a thorough characterization of its performance. All of this demonstrates that our TSN implementation can effectively replace the usual fieldbuses for aerospace and, thus, implement a functional avionics system with off-the-shelf components (COTS) instead. Furthermore, we take advantage of these results to make an early proposal of the elements that should be included in an aerospace profile for TSN.

We introduce an experimental integration of WR timing and our TSN system in **Part IV** of the manuscript, where we devote a chapter to presenting the research that we conducted jointly with collaborators from the Technical University of Denmark (DTU) during a research visit. A substantial part of the research at DTU aimed to study the automatic production of configuration settings for our TSN system with specialized tools. Hence, the chapter presents the "hybrid" architecture with WR timing alongside a characterization of internal processing delays required by the tool. We present some preliminary results where we conclude that, even though we have successfully integrated our system with WR timing, we still need to supply additional improvements to our architecture to improve its determinism. This will be explored in the future work.

**Part V** contains the conclusions of the thesis project. Thus, we show that we have implemented a deterministic TSN system using a highly customizable FPGA architecture, that is also adaptable, and that can be fitted and targeted to multiple devices and scenarios. In this context, we emphasize our successful implementation of the system for major use cases in the Smart Grid and for the avionics of the Miura 1 microlauncher. Also, we have shown the preliminary results of our integration with WR timing for exploring the application of TSN to scientific infrastructure and other advanced topics related to

the automatic generation of configuration parameters. We conclude by assessing the overall level of compliance of our initial objectives and with the proposal of an upgrade path for the system as future work. Lastly, we have included some considerations in the Appendixes on select topics relating to network driver development for embedded Linux environments.

*The world needs inventors - great ones. You can be one. If you love what you do and are willing to do what it really takes, it's within your reach.*

- Steve Wozniak

#### AGRADECIMIENTOS

Le quiero agradecer a mis directores, Javier Díaz y Eduardo Ros, por su apoyo constante, orientación, y las oportunidades que me han dado. Gracias a ellos salgo con una visión mucho más madura, meditada y reforzada del papel que las tecnologías de comunicación determinista desempeñan a la hora de resolver problemas de ingeniería acuciantes en el mundo real.

Abordar todo este trabajo habría sido imposible sin el apoyo del grupo de investigación en sincronización de la Universidad de Granada, o si no hubiera contado con la ayuda inestimable de colaboradores en el Instituto Andaluz de Astrofísica (IAA) o en la empresa Seven Solutions, gracias a los cuales esta tesis ha podido explorar aspectos técnicos, experimentales, y casos de uso que son difíciles de encontrar en la universidad y que han enriquecido aún más su contenido.

Sobre el trabajo del comienzo de la tesis, me quería acordar de Antonio Miguel López, por toda la ayuda que me dio con los drivers de Linux, de Antonio Jurado por el apoyo en los experimentos de CTA, y de Pablo Marín por su trabajo en los TDCs de la ZEN-CTA. De José Luis Gutiérrez, por explicarme sobre sistemas empotrados y White Rabbit. Sobre el trabajo de TSN, le agradezco a Beatriz Aparicio del IAA su contribución a módulos importantes de la arquitectura, y por su orientación y consejos para el diseño de sistemas en espacio. También le estoy agradecido enormemente a Seven Solutions y a su equipo de TSN por su trabajo en la sincronización, en RTEMS, y en módulos principales del sistema. En concreto, a Rafael Rodríguez, Luis Medina, Jorge Machado, y Marco Fuentes. He aprendido muchísimo con vosotros y he podido participar en proyectos muy interesantes y apasionantes. En general, a todos los que han estado involucrados en los proyectos de TSN, desde el diseño de las placas a la validación. También me quiero acordar de Francisco Barranco, por darnos otra área de aplicación y estudio en videovigilancia.

¡Muchísimas gracias a todos!

## CONTENTS

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iii                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| List of Tables XX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xv                                                             |

| Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vii                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

| Introduction and State of the Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                              |

| INTRODUCCIÓN         1.1       Motivación tras el desarrollo de comunicaciones abiertas y deterministas.         1.2       Objetivos principales         1.3       El marco de trabajo de la tesis         1.4       Visión general de la estructura de la tesis                                                                                                                                                                                                                                                                                                                                    | 3<br>4<br>6<br>9<br>10                                         |

| <ul> <li>2.1 Motivation. The drive to develop open, deterministic communications.</li> <li>2.2 The main objectives</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13<br>14<br>15<br>18<br>19                                     |

| 3.1       Real-time communication with fieldbuses       2         3.1.1       Level of performance       2         3.1.2       Representative applications and use cases       2         3.1.3       The shift towards deterministic Ethernet       2         3.2       The drive for fully deterministic Ethernet       2         3.2.1       A presentation of motivational use cases       2         3.2.2       A brief description of Audio/Video Bridging       2         3.3       Overview of TSN and its functionalities       2         3.4       An introduction to TSN profiles       2 | 21<br>22<br>23<br>23<br>24<br>25<br>26<br>28<br>30<br>34<br>36 |

| 4.1The WR-ZEN and other WR-capable boards44.2The development environment: Xilinx Zynq-7000 SoCs and FPGAs44.3The laboratory instrumentation44.3.1The networking equipment44.3.2The measurement equipment44.3.3The FPGA debugging equipment44.3.4Other laboratory equipment44.3.5Network inspection tools4                                                                                                                                                                                                                                                                                           | 39<br>40<br>41<br>42<br>43<br>43<br>44<br>44<br>44<br>44       |

| 4.4       | The experimental and design methodology                        | 44      |

|-----------|----------------------------------------------------------------|---------|

| 4.4.1     | The general approach for TSN devices                           | 45      |

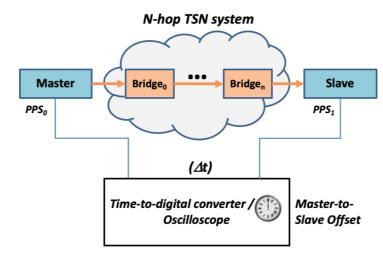

| 4.4.2     | Timing transfer accuracy                                       | 45      |

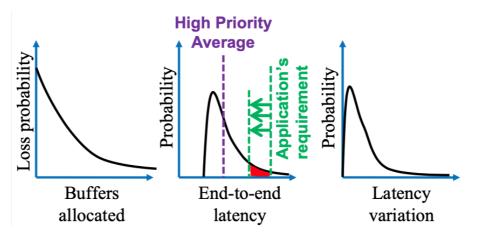

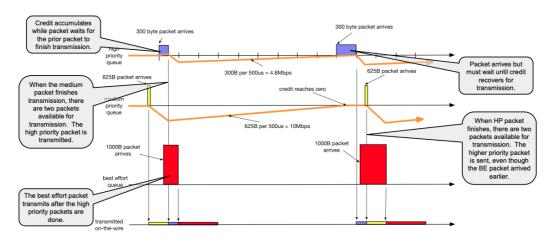

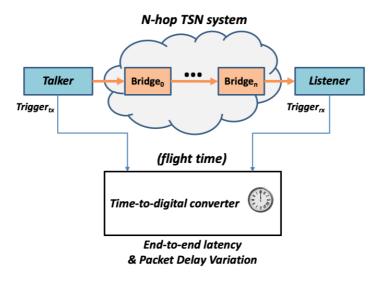

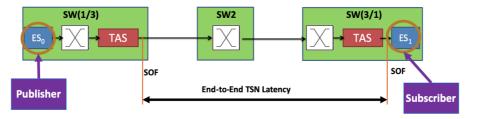

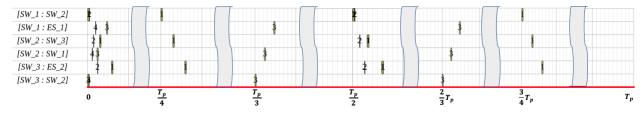

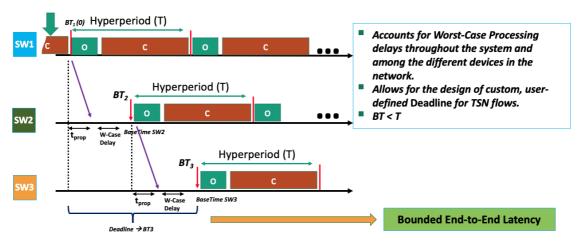

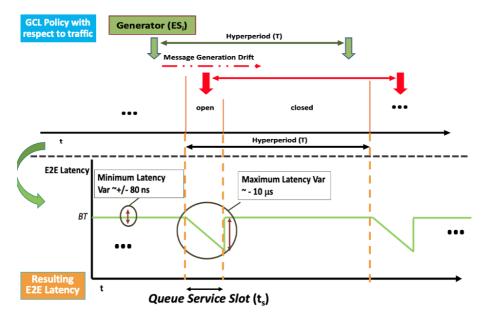

| 4.4.3     | The end-to-end latency and determinism at data forwarding      | 46      |

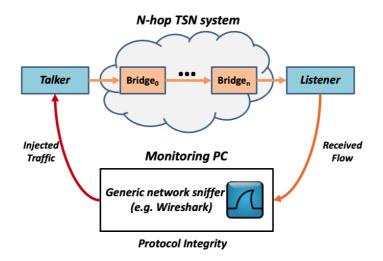

| 4.4.4     |                                                                | 47      |

| 4.4.5     |                                                                | 48      |

| 4.4.6     |                                                                | -<br>48 |

| 4.4.7     |                                                                | 50      |

| 1.1.7     |                                                                | 5-      |

| 5 THE DEV | VELOPMENT OF A WR TIME-STAMPING BOARD FOR CTA                  | 53      |

| 5.1       | ABSTRACT                                                       | 54      |

| 5.2       | Introduction                                                   | 55      |

| 5.2.1     |                                                                | 55      |

| 5.2.2     |                                                                | 56      |

| 2         | Overview of the Cherenkov Telescope Array                      | 57      |

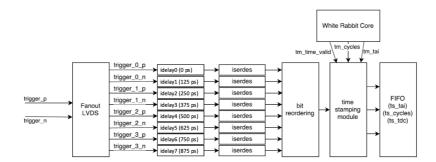

|           | UCTS Design with the WR-compatible ZEN-CTA Node for the Small- | 51      |

|           | Sized Telescopes                                               | 59      |

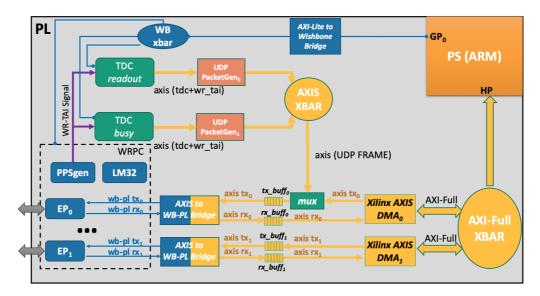

|           | The DMA Upgrade and Time Stamp Transmission                    | 62      |

|           |                                                                | 63      |

| 5.5.1     |                                                                | -       |

| 5.5.2     | 1                                                              | 65      |

| 5.5.3     | 1                                                              | 66      |

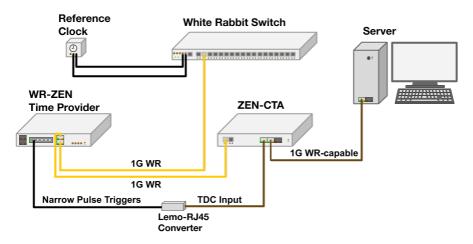

|           | Experimental Setup                                             | 66      |

| 5.6.1     | 1 1                                                            | 67      |

| 5.6.2     | 0 1 1                                                          | 68      |

| 0         | .2.1 Characterization of the TDC                               | 68      |

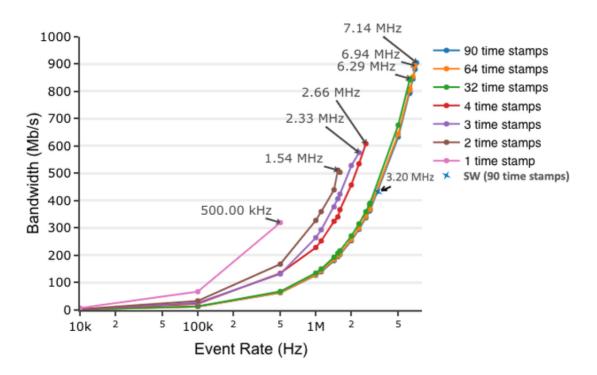

| 5         | .2.2 Event Rate vs Bandwidth                                   | 69      |

|           | Outcome of the Experiments                                     | 71      |

| 5.7       | Conclusions and Future Work                                    | 72      |

| 5.8       | Follow-up to the article. Integration with TSN components      | 73      |

|           |                                                                |         |

|           | and Inclose station of a TCN Naturalium Contains               | 75      |

| II Design | and Implementation of a TSN Networking System                  | 75      |

| 6 тне сов | NSTRUCTION OF A TSN NODE                                       | 77      |

|           | General structure of a TSN node                                | 78      |

|           | The usual roles of operation of TSN nodes                      | 80      |

|           | The software environment of a TSN node                         | 82      |

| 6.3.1     |                                                                | 82      |

| 6.3.2     |                                                                | 82      |

| 5         |                                                                |         |

| 6.3.3     |                                                                | 84      |

| 6.3.4     |                                                                | 85      |

| 6.3.5     |                                                                | 86      |

| 6.3.6     | 0                                                              | 87      |

| 6.3.      |                                                                | 88      |

| 6.3.      | 8                                                              | 88      |

| 6.3.      | .6.3 The debug and supervision component                       | 88      |

| 6.3.7     | 0 5 0                                                          | 89      |

| 6.4       | Design of the networking subsystem                             | 89      |

|   | 6.4.1 T   | he Xilinx DMA Engine                                               | 89  |

|---|-----------|--------------------------------------------------------------------|-----|

|   | 6.4.2 T   | he Ethernet medium access controller                               | 90  |

|   | 6.4.3 T   | he packet coding sublayer and physical medium attachment           | 90  |

|   | 6.4.4 T   | he physical layer transceivers                                     | 91  |

|   | 6.4.5 N   | etwork drivers for embedded Linux environments                     | 91  |

|   | 6.4.5.1   | A device tree entry                                                | 92  |

|   | 6.4.5.2   | The main driver code                                               | 92  |

|   | 6.4.5.3   | The driver variants                                                | 93  |

|   | 6.5 Integ | gration with the timing subsystem                                  | 93  |

|   |           |                                                                    |     |

| 7 |           | MPLEMENTATION OF THE TSN SUBSYSTEM                                 | 95  |

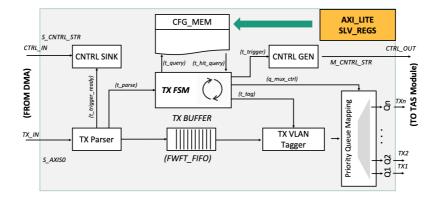

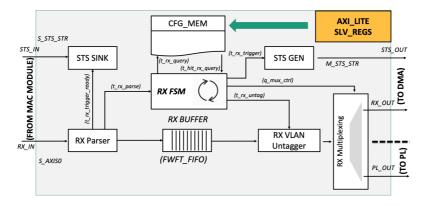

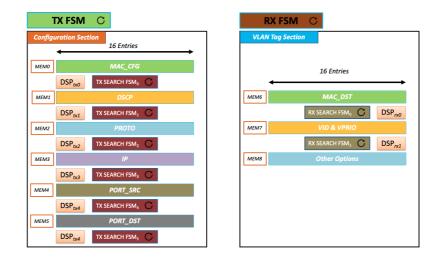

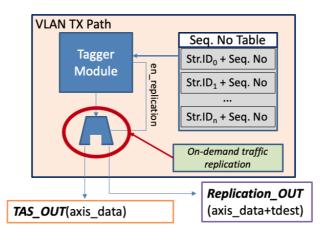

|   | -         | VLAN module                                                        | 96  |

|   | -         | he VLAN block design diagram                                       | 97  |

|   | 7.1.1.1   | The TX data path                                                   | 97  |

|   | 7.1.1.2   | The RX data path                                                   | 98  |

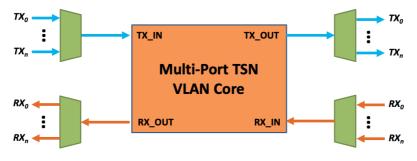

|   | 7.1.1.3   | Sharing of multiple Ethernet ports over a single TSN VLAN core     |     |

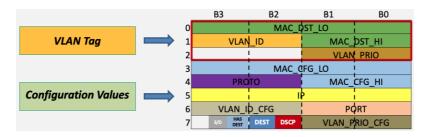

|   | •         | he VLAN configuration table                                        | 99  |

|   | 7.1.2.1   | The VLAN tag section                                               | 100 |

|   | 7.1.2.2   | The Configuration Values section                                   | 101 |

|   | 7.1.2.3   | Identifying traffic classes with the VLAN Configuration Table .    | 102 |

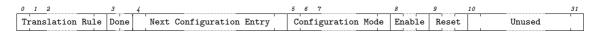

|   | 7.1.3 Si  | upplying the configuration: the Slave configuration registers      | 105 |

|   | 7.1.3.1   | Description of the configuration registers                         | 105 |

|   |           | he configuration sequence in the Slave registers for the VLAN core | 112 |

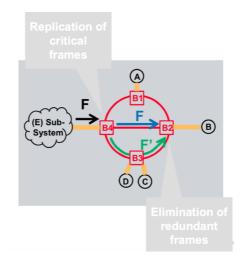

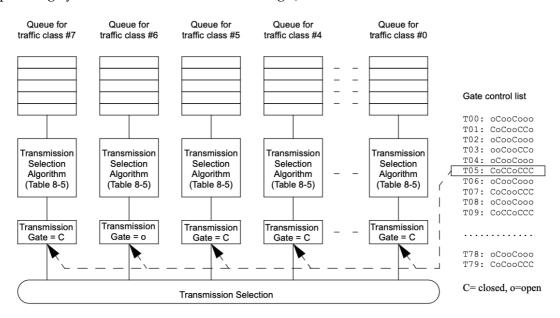

|   |           | s for Seamless Redundancy                                          | 114 |

|   | •         | lentification of TSN streams                                       | 114 |

|   | -         | equence Number Generation                                          | 114 |

|   |           | eplication (Stream Splitting)                                      | 115 |

|   |           | limination of duplicates (Stream Filtering)                        | 115 |

|   |           | verview of the operation of the FRER features                      | 115 |

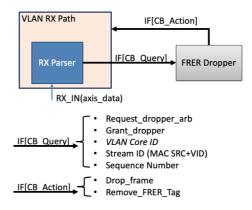

|   | _         | he TSN FRER Dropper module                                         | 117 |

|   | 7.2.6.1   | The AXI-Streaming RX query interface                               | 118 |

|   | 7.2.6.2   | The CRC-32 pseudohash block                                        | 119 |

|   | 7.2.6.3   | The CRC-Hash Table and the Table Lookup Mechanism (pHash)          | 119 |

|   | 7.2.6.4   | The window table                                                   | 119 |

|   | 7.2.6.5   | The timeout counter bank                                           | 119 |

|   | 7.2.6.6   | The Dropper finite state machine                                   | 120 |

|   | 7.2.6.7   | The AXI-Streaming TX response interface                            | 120 |

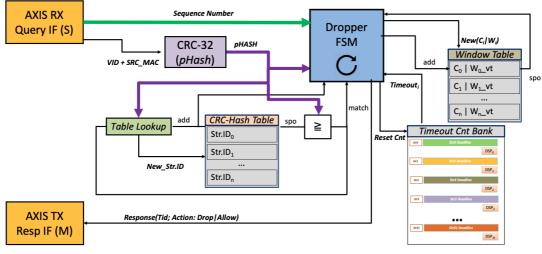

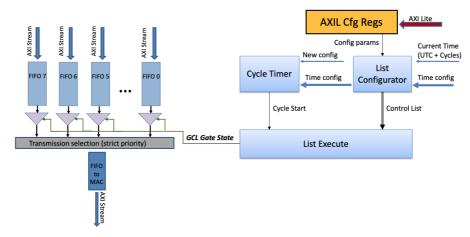

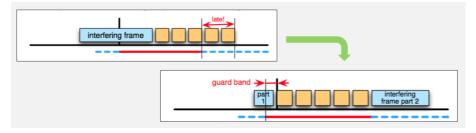

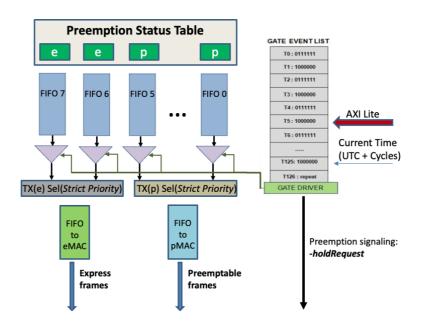

|   |           | time-aware traffic shaper                                          | 120 |

|   | 7.3.1 O   | verview of the operation of the time-aware traffic shaper          | 122 |

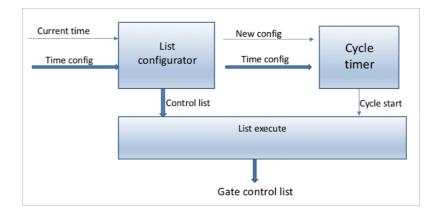

|   | 7.3.1.1   | The List Configurator FSM                                          | 123 |

|   | 7.3.1.2   | The cycle timer FSM                                                | 123 |

|   | 7.3.1.3   | The list execute FSM                                               | 124 |

|   | 7.3.1.4   | Relationship to the operation of the TAS core                      | 124 |

|   |           | onfiguration of the time-aware traffic shaper                      | 124 |

|   | 7.3.2.1   | Slave o: the FIFO configuration register                           | 125 |

|   | 7.3.2.2   | Slave 1: the time interval configuration register                  | 126 |

|   | 7.3.2.3   | Slave 2: the used time interval register                           | 127 |

|   | 7.3.2.4   | Slave 3: the control list length register                          | 127 |

| 7.3.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Slave 4: the cycle time register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 127                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.3.2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Slave 5: the cycle time extension register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                    |

| 7.3.2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Slave 6: the operational cycle time extension register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                    |

| 7.3.2.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Slave 7: the administrative base time register (least significant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                    |

| 7.3.2.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Slave 8: the administrative base time register (intermediate bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |

| 7.3.2.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Slave 9: the administrative base time register (most significant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bits)129                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Slave 10: the operational base time register (least significant bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Slave 11: the operational base time register (intermediate bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Slave 12: the operational base time register (most significant b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Slave 13: the error register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

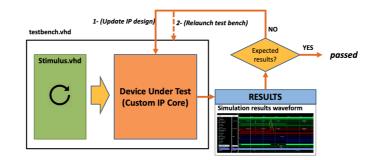

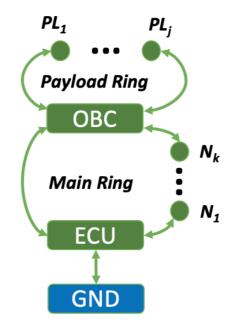

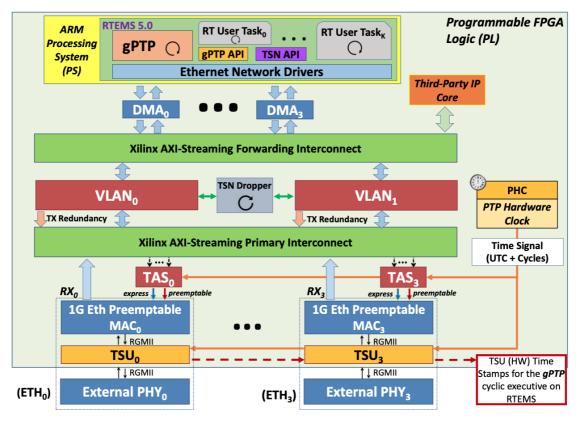

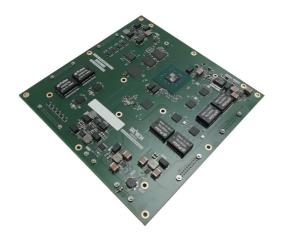

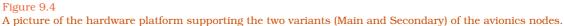

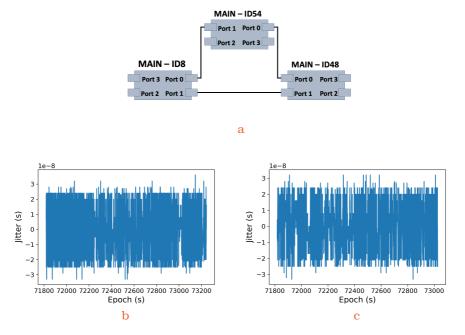

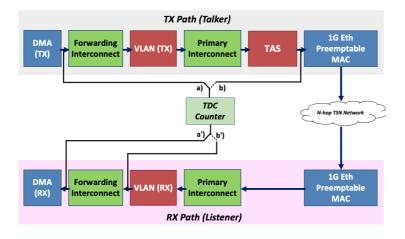

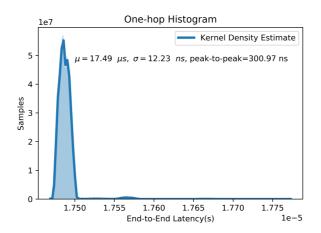

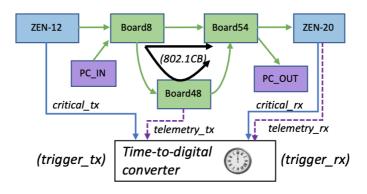

| 7.3.2.15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | The configuration sequence of the time-aware traffic shaper .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                  |