### Universidad de Granada Centro de Investigación en Tecnologías de la Información y las Comunicaciones

Programa de Doctorado en Física y Ciencias del Espacio Doctoral Thesis

### Application of the Pseudo-MOSFET Technique on Silicon-On-Insulator Wafers

Author: Cristina Fernández Sánchez Advisors: Noel Rodríguez Santiago Francisco J. Gámiz Pérez

A thesis submitted in fulfilment of the requirements for the Doctor degree

at the

Nanoelectronics Research Group Departamento de Electrónica y Tecnología de Computadores

21st May, 2016

Editor: Universidad de Granada. Tesis Doctorales Autora: Cristina Fernández Sánchez ISBN: 978-84-9163-010-4 URI: http://hdl.handle.net/10481/44457

## Abstract

### Keywords

Pseudo-MOSFET, SOI, Split-C(V), effective capacitance area, effective field, carrier mobility, FD-SOI MOSFETs, Graphene-On-Insulator, sensor platform.

### Abstract

This work has been focused on a deep and systematic study of the point-contact Pseudo-MOSFET characterization technique.

Firstly, theoretical models for the Pseudo-MOSFET have been described and developed for ultrathin Si wafers, and for those with also ultrathin BOX. They have been validated with several simulations. Then, some Pseudo-MOSFET samples with different thickness and surface (passivated/non-passivated) have been analyzed and characterized.

Later, the combination of the Split-C(V) technique with the Pseudo-MOSFET configuration has allowed to obtain the carrier mobility in bare SOI wafers as a function of the inversion charge. Nevertheless, since the evaluation of this parameter depends strongly on the value of the effective area considered for calculations, this area has been examined as a function of the characteristics of the set up configuration.

Taking into account the variability of the area with experimental configuration parameters, a mathematical model has been proposed to calculate the effective surface in any characterization scenario. The model has been verified with the experimental results.

On the other hand, the carrier mobility have been also studied in Pseudo-MOSFET samples. In order to achieve the optimum enhancement for the mobility, the specific values for the backgate bias have been calculated using Poisson-Schrödinger numerical simulations combined with Split-C(V) experimental results.

To conclude, new applications associated to point-contact techniques have been analyzed such us the use of the Pseudo-MOSFET as a sensor platform. In addition, several studies have been carried out on Poly-silicon or Graphene-On-Insulator samples demonstrating the flexibility of the point-contact methods to evolve with emerging substrates.

### Resumen

### Palabras clave

Pseudo-MOSFET, SOI, Split-C(V), área efectiva, campo eléctrico efectivo, movilidad, FD-SOI MOSFETs, Graphene-On-Insulator, plataforma sensora.

### Resumen

El trabajo presentado ha consistido en un amplio y sistemático estudio sobre la técnica de caracterización eléctrica denominada Pseudo-MOSFET.

Inicialmente, se describieron y desarrollaron modelos teóricos para obleas Pseudo-MOS con láminas de Si ultradelgadas, así como para aquellas con BOX ultradelgados. Estos modelos se validaron con varias simulaciones. Más adelante, numerosas muestras de Pseudo-MOSFETs con diferentes espesores y superficies (pasivada/no pasivada) fueron analizadas y caracterizadas experimentalmente.

Posteriormente, la combinación de la conocida técnica Split-C(V) con la configuración Pseudo-MOSFET permitió obtener la movilidad de los portadores en una oblea SOI a través del valor de la carga de inversión. No obstante, ya que la evaluación de este parámetro depende en gran medida del área efectiva, dicha área fue examinada y calculada según las características de la configuración experimental.

Teniendo en cuenta la variabilidad del área con los parámetros asociados a la configuración experimental, se ha propuesto un modelo matemático que permite calcular la superficie efectiva usando cualquier configuración en el Pseudo-MOSFET. Dicho modelo ha sido validado con resultados de laboratorio.

Por otro lado, la movilidad de los portadores en obleas SOI ha sido también estudiada. Así pues, con el fin de conseguir el valor óptimo de la movilidad, se calcularon las tensiones de puerta con las que polarizar el Pseudo-MOSFET usando simulaciones numéricas y combinándolas con resultados experimentales de Split-C(V).

Para terminar, se analizaron nuevas aplicaciones asociadas a las técnicas de puntas de contacto, tales como el uso del Pseudo-MOSFET como plataforma sensora. Además, otros estudios sobre obleas de Poly-Si o Grafeno-sobre-Aislante se llevaron a cabo demostrando así la flexibilidad de estos métodos para evolucionar con los nuevos sustratos emergentes.

### **Declaration of Authorship**

Cristina Fernández Sánchez, as Ph.D. Candidate, and Noel Rodríguez Santiago and Francisco J. Gámiz Pérez, as Ph.D. Advisors and Professors of Electronics at the Departamento de Electrónica y Tecnología de Computadores of the Universidad de Granada in Spain,

CERTIFY:

that the research work contained in the present report, entitled **Application of the Pseudo-MOSFET Technique on Silicon-On-Insulator Wafers**, has been performed under the full guidance of the Ph.D. supervisors and, as far as our knowledge reaches, during the work, it has been respected the rights of others authors to be cited, when their publications or their results have been used.

Granada, 21st May, 2016.

Author: Cristina Fernández Sánchez Advisors: Noel Rodríguez Santiago Francisco J. Gámiz Pérez

" There is a will, there is a way." Anonymous

## Contents

| D  | eclar | ration of Authorship                                                                                                                                                         |       | vii                    |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|

| C  | onter | $\mathbf{nts}$                                                                                                                                                               |       | xi                     |

| Li | st of | f Figures                                                                                                                                                                    |       | $\mathbf{x}\mathbf{v}$ |

| Li | st of | f Tables                                                                                                                                                                     | x     | xiii                   |

| A  | bbre  | viations                                                                                                                                                                     | 2     | cxv                    |

| 1  | Intr  | roduction to SOI Materials and Devices                                                                                                                                       |       | 1                      |

|    | 1.1   | Motivations                                                                                                                                                                  |       | 1                      |

|    | 1.2   | SOI wafers fabrication                                                                                                                                                       |       | 3                      |

|    | 1.2   | 1.2.1 Separation by IMplatation OXygen, SIMOX                                                                                                                                |       | 4                      |

|    |       | 1.2.2   Bond-And-Etch-Back, BESOI                                                                                                                                            |       | 5                      |

|    |       | 1.2.3 Epitaxial Layer TRANsfer, ELTRAN                                                                                                                                       |       | 6                      |

|    |       | 1.2.4 Smart-Cut <sup><math>TM</math></sup>                                                                                                                                   |       | 7                      |

|    | 1.3   | Advantages of SOI technology                                                                                                                                                 |       | 8                      |

|    | 1.4   | SOI devices classification                                                                                                                                                   |       | 9                      |

|    | 1.5   | SOI wafers characterization                                                                                                                                                  |       | 10                     |

|    |       | 1.5.1 Four-point probe                                                                                                                                                       |       | 10                     |

|    |       | 1.5.2 Two-point probe                                                                                                                                                        |       | 11                     |

|    |       | 1.5.3 Second Harmonic Generation, SHG                                                                                                                                        |       | 12                     |

|    | 1.6   | Defects of SOI materials                                                                                                                                                     |       | 13                     |

|    | 1.7   | Conclusions                                                                                                                                                                  | <br>• | 14                     |

| 2  | Elec  | ctrical Characterization of Bare SOI Wafers                                                                                                                                  |       | 15                     |

|    | 2.1   | The Pseudo( $\Psi$ )-MOSFET technique $\ldots \ldots \ldots$ |       | 15                     |

|    |       | 2.1.1 Principle and operation                                                                                                                                                |       | 15                     |

|    |       | 2.1.2 Methodology                                                                                                                                                            |       | 16                     |

|    |       | 2.1.3 Static characteristics                                                                                                                                                 |       | 16                     |

|    |       | 2.1.4 Y-function                                                                                                                                                             |       | 18                     |

|    | 2.2   | Theoretical models for ultrathin passivated $\Psi$ -MOSFETs                                                                                                                  |       | 19                     |

|    |       | 2.2.1 Two-interfaces model                                                                                                                                                   |       | 19                     |

|    |       | 2.2.1.1 Model for passivated $\Psi$ -MOSFET                                                                                                                                  | <br>• | 22                     |

|    |       | 2.2.1.2 Model for non-passivated $\Psi$ -MOSFET                                                                                                                              | <br>• | 23                     |

|    |       | 2.2.2 Three-interfaces model                                                                                                                                                 |       | 23                     |

|   |      | 2.2.2.1 Analytical model $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 2^4$                        |

|---|------|----------------------------------------------------------------------------------------------------------------------|

|   |      | 2.2.2.2 Capacitive model                                                                                             |

|   | 2.3  | Impact of the setup parameters on experimental current characteristics 27                                            |

|   |      | 2.3.1 Implications by changing the probe pressure                                                                    |

|   |      | 2.3.2 Implications of changing the probes interdistance                                                              |

|   |      | 2.3.3 Measurements on different cells                                                                                |

|   |      | 2.3.4 Implications of repeating the measurement                                                                      |

|   | 2.4  | Conclusions                                                                                                          |

| 3 | Nov  | vel Insights In Pseudo-MOSFET Technique 33                                                                           |

|   | 3.1  | Capacitance measurements                                                                                             |

|   |      | 3.1.1 C-V characteristics                                                                                            |

|   | 3.2  | Impact of experimental conditions on capacitance curves                                                              |

|   |      | 3.2.1 Variation of the AC input signal level 39                                                                      |

|   |      | 3.2.2 Variation of the probes pressure 39                                                                            |

|   |      | 3.2.3 Variation of the number of probes and the probe spacing 42                                                     |

|   |      | 3.2.4 Variation of the BOX layer thicknesses. Substrate effect                                                       |

|   | 3.3  | The Split- $C(V)$ technique $\ldots \ldots 44$ |

|   | 3.4  | The effective area in point-contact capacitance measurements                                                         |

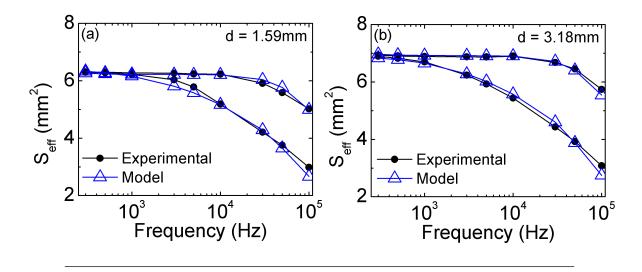

|   |      | 3.4.1 Impact of the frequency on $S_{eff}$                                                                           |

|   |      | 3.4.2 Relation between $C_{BOX}$ and $S_{eff}$                                                                       |

|   |      | 3.4.3 Carrier density determination                                                                                  |

|   |      | $3.4.4 Model development \dots 48$                                                                                   |

|   |      | 3.4.5 Simulation results                                                                                             |

|   |      | 3.4.6 Experimental results                                                                                           |

|   |      | $3.4.6.1$ Two-needle configuration $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 52$        |

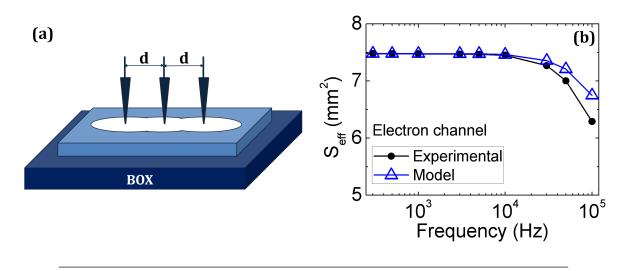

|   |      | $3.4.6.2$ Three-needle configuration $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 55$             |

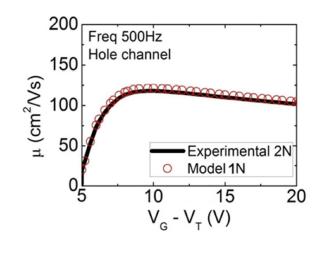

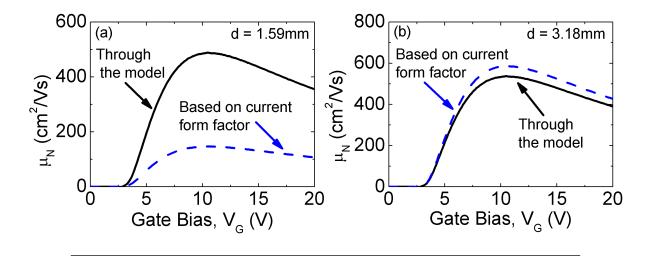

|   |      | 3.4.7 Extraction of $\mu_{eff}$                                                                                      |

|   | 3.5  | Conclusions                                                                                                          |

| 4 | Effe | ective Mobility Extraction in Bare SOI Substrates 57                                                                 |

|   | 4.1  | Introduction                                                                                                         |

|   | 4.2  | The role of the top-interface on the effective electric field                                                        |

|   |      | 4.2.1 Discussion of the electrostatic potential                                                                      |

|   |      | 4.2.2 Effective electric field model                                                                                 |

|   | 4.3  | Results on mobility                                                                                                  |

|   | 4.4  | Conclusions                                                                                                          |

| 5 | App  | olications of Point-Contact Techniques 69                                                                            |

|   | 5.1  | Poly-silicon samples                                                                                                 |

|   |      | 5.1.1 Electrical characterization                                                                                    |

|   |      | 5.1.1.1 Dependence on the probe pressure $\ldots \ldots \ldots \ldots \ldots \ldots $ 70                             |

|   |      | 5.1.1.2 Dependence on the drain voltage $\ldots \ldots \ldots \ldots \ldots \ldots \ldots $                          |

|   |      | 5.1.1.3 Dependence on delay time                                                                                     |

|   |      | 5.1.1.4 Mobility results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$                                    |

|   | 5.2  | Graphene-On-Insulator samples                                                                                        |

|   |      | 5.2.1 Methodology                                                                                                    |

|   |            | 5.2.2  | I-V charac   |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|---|------------|--------|--------------|--------------|----------|---------|----------|------------------------|-----|------|-----|-----|-----|---|-----|---|-----|-----|

|   |            |        |              | nitial cali  |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            |        |              | mpact of     |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            |        |              | Resistance   |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            |        |              | Obtaining    |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | 5.2.3  | C-V chara    |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | 5.3        | Detern | nination of  |              | -        |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | 5.3.1  | Developm     |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | 5.3.2  | Experimen    |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | 5.4        | Conclu | sions        |              |          |         |          |                        |     | •••  |     | ••• | • • | • | • • | • |     | 85  |

| 6 | Con        |        | ns and Fu    |              | -        |         |          |                        |     |      |     |     |     |   |     |   |     | 87  |

|   | 6.1        |        | achievemen   |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | 6.2        | Future | research to  | opics        |          |         |          |                        |     | •••  |     | • • |     | • | ••• | • |     | 88  |

|   |            |        |              |              |          | _       |          |                        |     |      |     |     |     |   |     |   |     |     |

| Α |            |        | of the Ef    |              |          | ·       |          |                        |     |      |     |     |     |   |     |   |     | 89  |

|   | A.1        |        | uction       |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | A.2        |        | Depleted SC  |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | A.3        |        | point of e   |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | A.4        | -      | f bias regio |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            |        | Ultrathin    |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | <u>م</u> ۲ | A.4.2  | Thick-BO     |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | A.5        | Conclu | isions       |              |          |         |          |                        |     | • •  |     | ••• | • • | • | •   | • | ••• | 95  |

| В | Nar        |        | ronics Lal   |              |          |         |          |                        |     |      |     |     |     |   |     |   |     | 97  |

|   | B.1        | Introd | uction       |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | B.1.1  | Semicondu    |              | -        |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | B.1.2  | Parameter    | •            |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

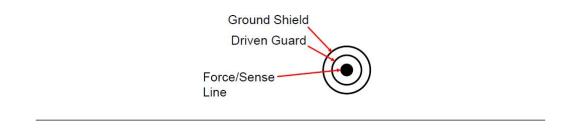

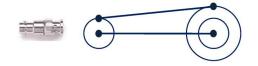

|   |            | B.1.3  | Triaxial ca  |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            |        | Impedance    |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | B.1.5  | JANDEL       |              | -        |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | B.1.6  | Janis prob   |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | B.1.7  | BNC-Tria     | -            |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            |        |              | Pseudo-M     |          | -       |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | B.1.8  | Semi-auto    | -            | Č.       |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | B.1.9  | Microscop    | e            |          |         |          |                        |     | • •  |     | • • | • • | • | ••• | • |     | 104 |

| С |            |        | n Process    |              |          |         |          | -                      |     |      |     |     |     |   |     |   |     | 107 |

|   | C.1        |        | ption of the | -            |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

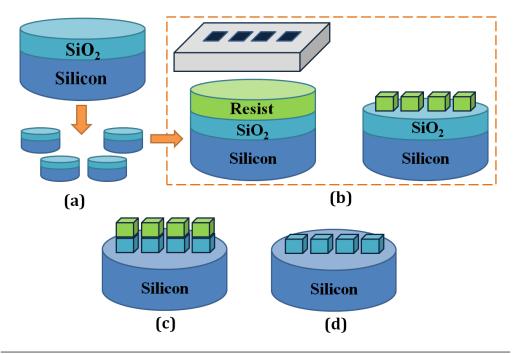

|   |            | C.1.1  | Step 1. Cu   |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | C.1.2  | Step 2. Pl   | _            |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   |            | C.1.3  | Step 3. Re   |              |          |         | 1 C      |                        |     |      |     |     |     |   |     |   |     |     |

|   | <i>a</i> - | C.1.4  | Step 4. Re   |              |          |         |          |                        |     |      |     |     |     |   |     |   |     |     |

|   | C.2        |        | cterization  |              | · ·      |         |          |                        |     |      |     |     |     |   |     |   |     |     |

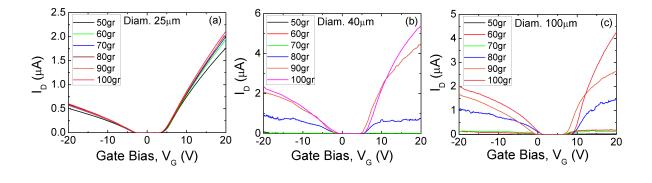

|   |            | C.2.1  | I-V charac   | eteristics a | ıs a fun | ction o | of the j | $\operatorname{probe}$ | dia | mete | er. |     |     | • |     | • |     | 112 |

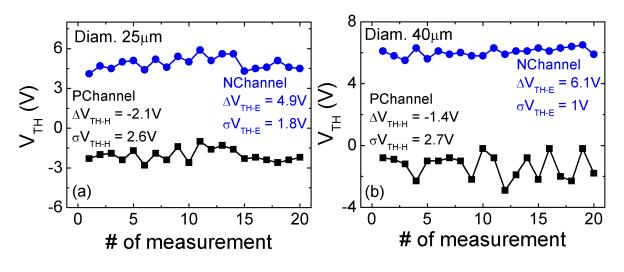

| C.2.3         | I-V measurements with different probe inter-distances | . 114 |

|---------------|-------------------------------------------------------|-------|

| C.2.4         | C-V Measurements with different probe inter-distances | . 114 |

| C.2.5         | Obtaining of the carrier mobility                     | . 116 |

| D List of put | olications                                            | 117   |

| Bibliography  |                                                       | 119   |

## List of Figures

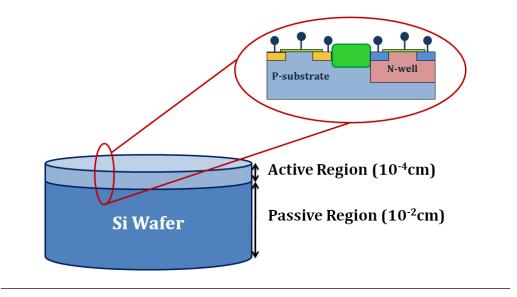

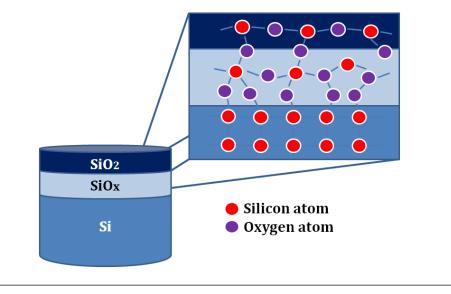

| 1.1  | Cross section of the superficial layer in a bulk wafer                                                                    | 2   |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

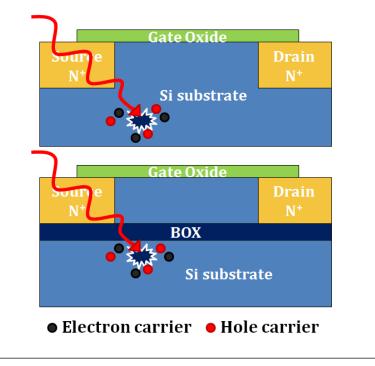

| 1.2  | Effect of the ionizing radiation in bulk and SOI wafers                                                                   | 2   |

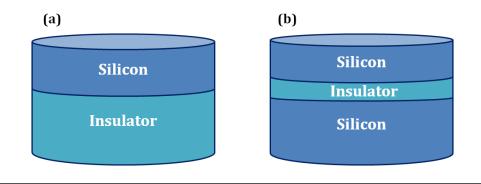

| 1.3  | Types of SOI structures: (a) when the Si layer is created directly on a substrate,                                        |     |

|      | and (b) when a insulator is formed inside a Si substrate.                                                                 | 3   |

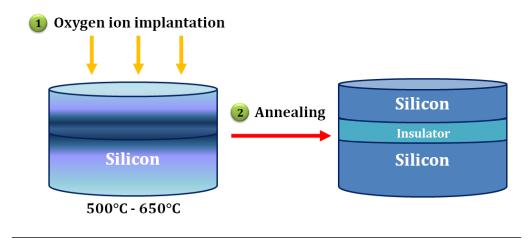

| 1.4  | The principle of SIMOX: a heavy-dose oxygen implantation into silicon followed                                            |     |

|      | by a very high temperature annealing step produces a buried layer of Silicon                                              |     |

|      | dioxide, below a thin crystalline Si film $[HRK^+87]$ .                                                                   | 4   |

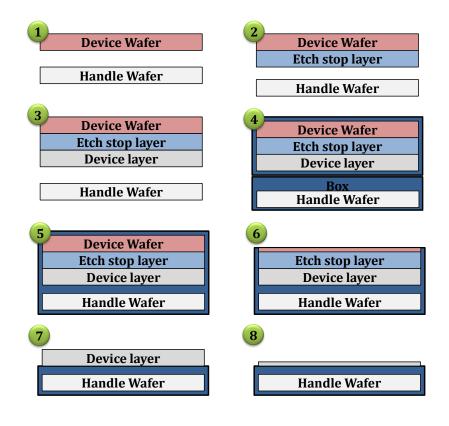

| 1.5  | Schematic representation of BESOI process for SOI wafer manufacturing [GR93].                                             | 5   |

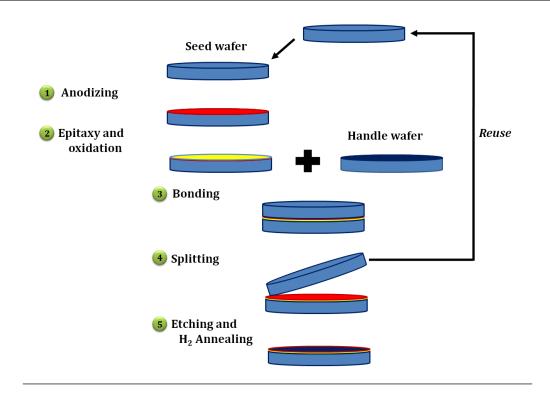

| 1.6  | Schematic representation of ELTRAN process for SOI wafer manufacturing [YSS94].                                           | 7   |

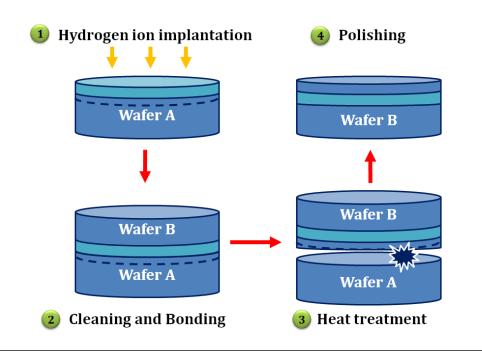

| 1.7  | Schematic illustration of the fabrication steps for a standard Unibond SOI wafer                                          |     |

|      | with Smart-Cut <sup><math>TM</math></sup> technique [CC03].                                                               | 8   |

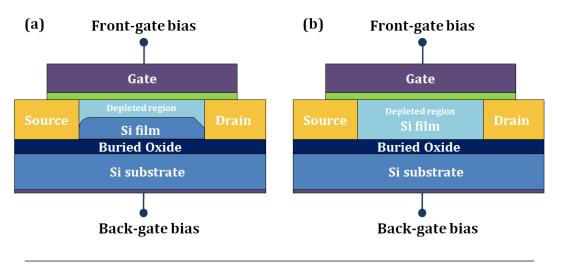

| 1.8  | Schematic of a partially (a) and a fully (b) depleted SOI MOSFET.                                                         | 9   |

| 1.9  | Schematic of the 4-point probe setup.                                                                                     | 10  |

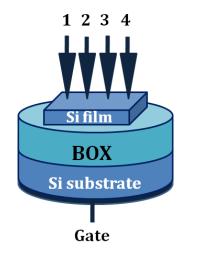

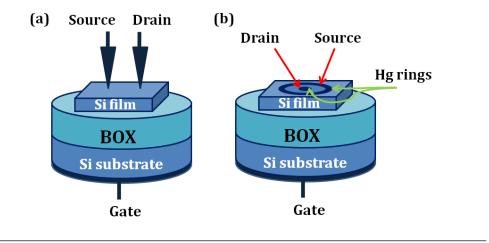

| 1.10 | $\Psi$ -MOSFET configuration with (a) metallic pressure probes, or (b) mercury probes.                                    | 11  |

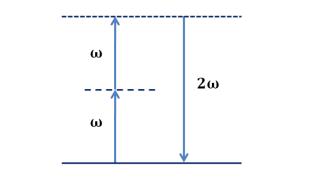

| 1.11 | Energy levels diagram involved in SHG process [APL <sup>+</sup> 07]                                                       | 12  |

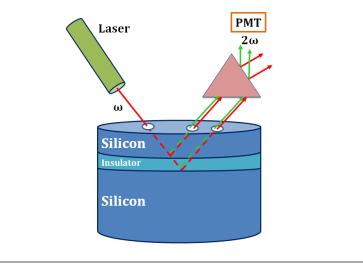

| 1.12 | Schematic of the Second Harmonic Generation technique.                                                                    | 12  |

| 1.13 | When the Silicon is bounded to an oxide, a region of defects is automatically                                             |     |

|      | originated at the interface.                                                                                              | 14  |

|      |                                                                                                                           |     |

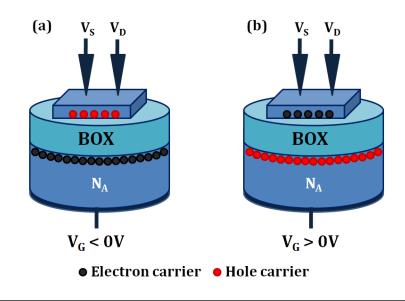

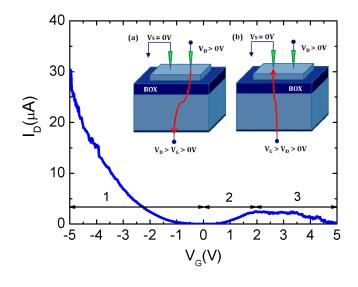

| 2.1  | A P-type $\Psi$ -transistor operating in strong (a) accumulation (hole channel) and                                       |     |

|      | (b) inversion regime (electron channel).                                                                                  | 16  |

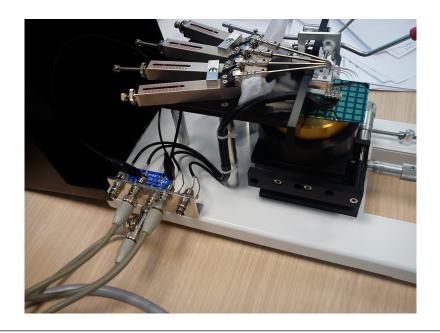

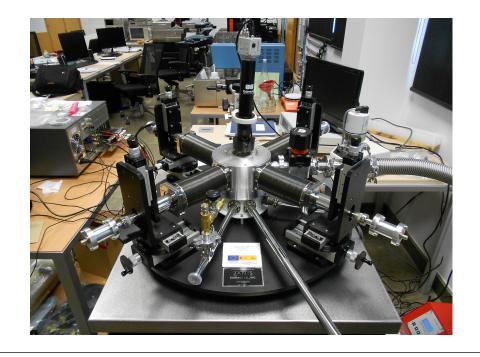

| 2.2  | The Jandel Universal probe station used to perform point-contact measurements                                             | 1 🗖 |

|      | is connected to the Agilent B1500A semiconductor analyzer through triaxial cables.                                        | 17  |

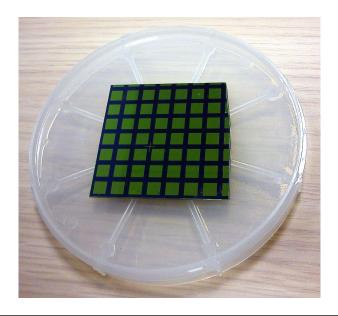

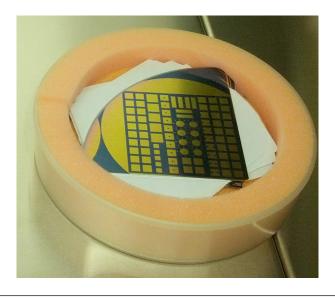

| 2.3  | The Pseudo-MOSFET technique is applied to SOI wafers divided in 5 mm $\times$ 5                                           | 1 🗁 |

| 0.4  | mm island and separated each other by 2 mm wide trenches of $SiO_2$                                                       | 17  |

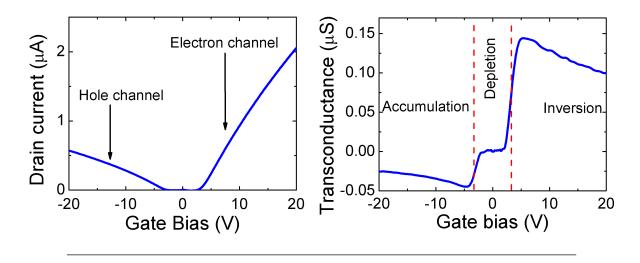

| 2.4  | Examples of $I_D(V_G)$ and $g_m(V_G)$ experimental characteristics which demonstrate                                      |     |

|      | the ambipolar behavior of a Pseudo-transistor. Non-passivated wafer, $t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, $V_D = 20$ mV. | 18  |

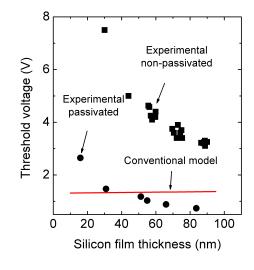

| 2.5  | Comparison between experimental values of threshold voltage in (circles) pas-                                             | 10  |

| 2.0  | sivated and (squares) non-passivated samples [HAHC07] and the conventional                                                |     |

|      | Pseudo-MOSFET model [CML00]                                                                                               | 20  |

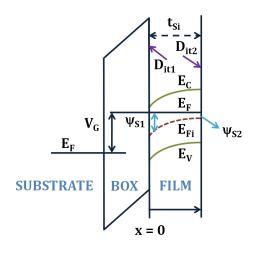

| 2.6  | $\Psi$ -MOSFET energy-band diagram for positive values of $V_G$ . The substrate-BOX                                       | 20  |

| 2.0  | interface is ignored in this first approach.                                                                              | 20  |

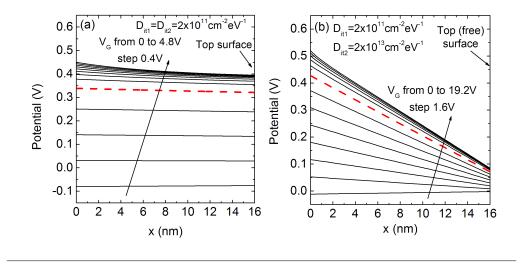

| 2.7  | In-depth potential profiles from BOX interface to free surface for a 16nm-thick                                           | -0  |

|      | $\Psi$ -MOSFET. (a) Passivated surface with quasi-flat profiles. (b) Non-passivated                                       |     |

|      | surface with linear potential variation. Profiles at threshold are presented with                                         |     |

|      | dashed line. $N_A = 10^{15} cm^{-3}, t_{BOX} = 145 \text{ nm.}$                                                           | 21  |

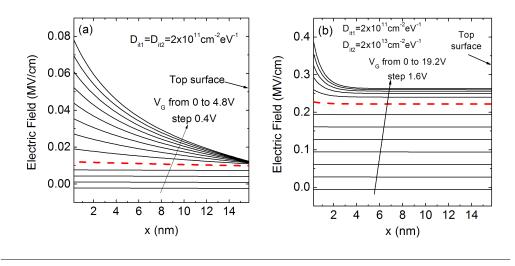

| 2.8  | Electric field profiles from BOX interface to free surface for a 16nm-thick $\Psi$ -MOSFET with (a) passivated surface and (b) non-passivated surface. Profiles at threshold are presented with dashed line. $N_A = 10^{15} cm^{-3}$ , $t_{BOX} = 145$ nm                                                                                                                                                                                                                                        | 21       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.9  | In-depth potential profiles from free surface to BOX interface in a $\Psi$ -MOSFET                                                                                                                                                                                                                                                                                                                                                                                                               |          |

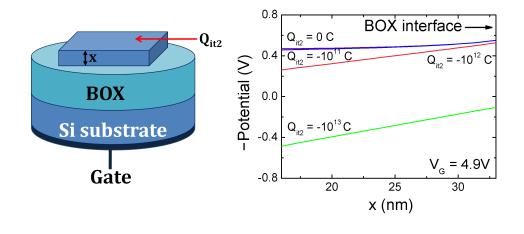

|      | for a certain gate bias upper to threshold voltage. Different trap charges at the top surface have been considered. $N_A = 10^{15} cm^{-3}$ , $t_{Si} = 20$ nm, $t_{BOX} = 145$ nm.                                                                                                                                                                                                                                                                                                              | 22       |

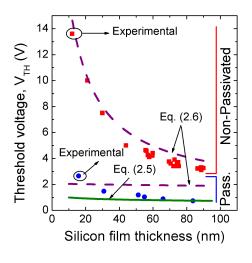

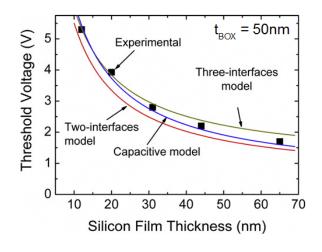

| 2.10 | Threshold voltage versus film thickness. Comparison between models and experimental data: (squares) non-passivated surface with $D_{it2} = 2 \times 10^{13} cm^{-2} eV^{-1}$ and (circles) passivated surface with $D_{m} = 2 \times 10^{11} cm^{-2} eV^{-1}$                                                                                                                                                                                                                                    |          |

|      | and (circles) passivated surface with $D_{it2} = 2 \times 10^{11} cm^{-2} eV^{-1}$ . $D_{it1} = 2 \times 10^{11} cm^{-2} eV^{-1}$ , $t_{Si} = 20$ nm, $t_{BOX} = 145$ nm.                                                                                                                                                                                                                                                                                                                        | 23       |

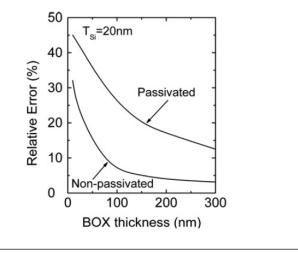

| 2.11 | Relative error calculated from threshold voltages obtained through simulations when third interface BOX-substrate is accounted for and when is not (adapted from [RCM <sup>+</sup> 11]).                                                                                                                                                                                                                                                                                                         | 24       |

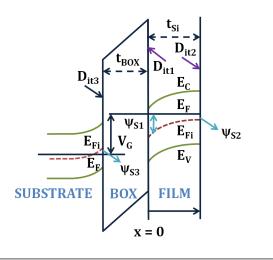

| 2.12 | $\Psi$ -MOSFET energy-band diagram for positive values of $V_G$ taking into account<br>the effect of BOX-substrate interface $(D_{it3})$ .                                                                                                                                                                                                                                                                                                                                                       | 24<br>24 |

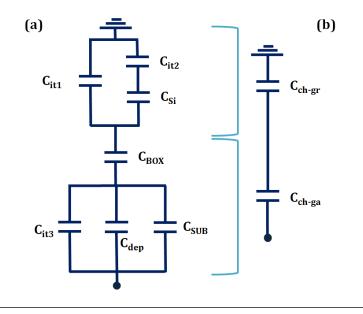

| 2.13 | Equivalent three-interface capacitance model of a $\Psi$ -MOSFET: (a) general and                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 2.14 | (b) simplified circuit (after associating some capacitances)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25       |

|      | Section 2.2.1 with experimental data from non-passivated wafers. $D_{it1} = 2 \times 10^{11} cm^{-2} eV^{-1}$ , $D_{it2} = 2 \times 10^{13} cm^{-2} eV^{-1}$ , $D_{it3} = 10^{11} cm^{-2} eV^{-1}$ .                                                                                                                                                                                                                                                                                             | 26       |

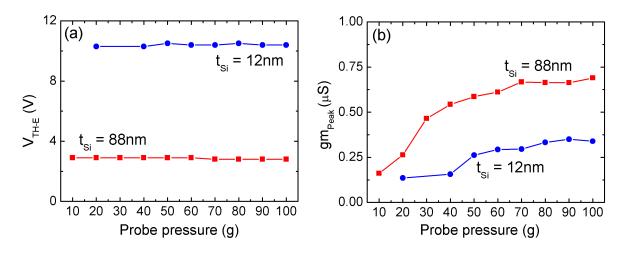

| 2.15 | Variation of (a) the threshold voltage and (b) the peak value for the transcon-<br>ductance as a function of the probe pressure when an electron channel is induced                                                                                                                                                                                                                                                                                                                              |          |

| 2.16 | in two of non-passivated samples. $V_D = 20 \text{ mV} \dots \dots \dots \dots \dots \dots \dots$<br>6 Current characteristics obtained as a function of the gate bias. At 80g the needles                                                                                                                                                                                                                                                                                                       | 27       |

|      | penetrate totally into the substrate. $t_{Si}=88~{\rm nm},t_{BOX}=25~{\rm nm},V_D=20~{\rm mV}.$ .                                                                                                                                                                                                                                                                                                                                                                                                | 28       |

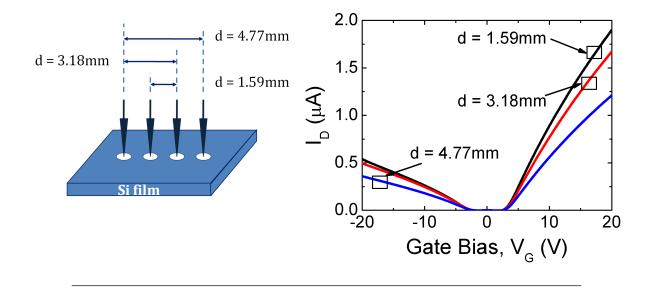

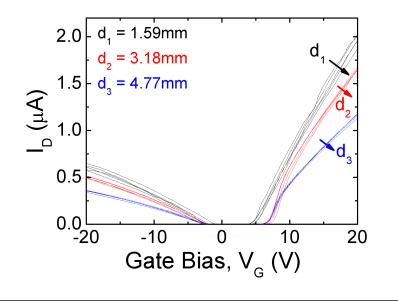

| 2.17 | (Left) Distance between probes selection. (Right) Current characteristics ob-<br>tained as a function of the gate bias for different probe interdistances. Non-<br>passivated wafer, $t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, $V_D = 20$ mV, P = 80 g                                                                                                                                                                                                                                               | 29       |

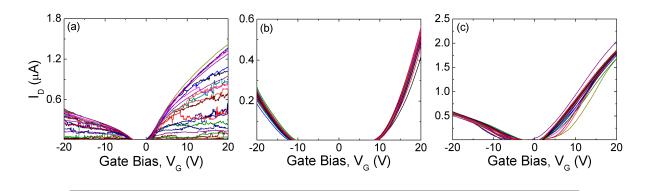

| 2.18 | <sup>6</sup> Current characteristics obtained as a function of the gate bias for the samples: (a)<br>1-A ( $t_{Si} = 17.3 \text{ nm}, t_{BOX} = 146.9 \text{ nm}$ ); (b) MU003 ( $t_{Si} = 12 \text{ nm}, t_{BOX} = 145 \text{ nm}$ , Non-passivated surface), and (c) MU005 ( $t_{Si} = 12 \text{ nm}, t_{BOX} = 145 \text{ nm}$ ,                                                                                                                                                              |          |

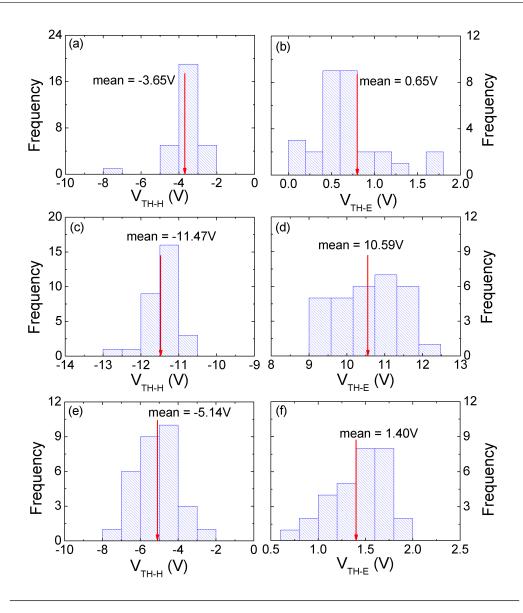

| 2.19 | Passivated surface). $V_D = 20 \text{ mV}$ , P = 80 g                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30       |

|      | for (a)-(c)-(e) holes and (b)-(d)-(f) electron channels. Samples: (a)-(b) 1-A ( $t_{Si} = 17.3 \text{ nm}, t_{BOX} = 146.9 \text{ nm}$ ); (c)-(d) MU003 ( $t_{Si} = 12 \text{ nm}, t_{BOX} = 145 \text{ nm}$ , Non-passivated surface), and (e)-(f) MU005 ( $t_{Si} = 12 \text{ nm}, t_{BOX} = 145 \text{ nm}$ , Passivated surface). $V_D = 20 \text{ mV}, P = 80 \text{ g}. \dots \dots$ | 31       |

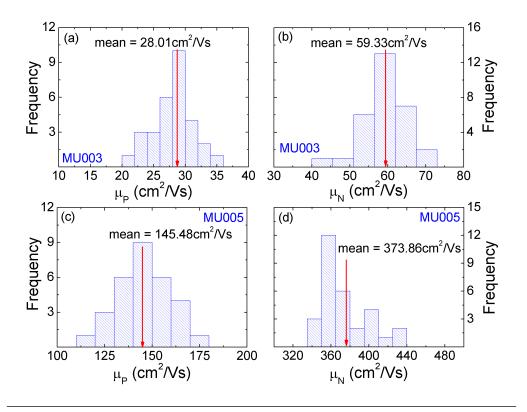

| 2.20 | Histograms associated to the carrier mobility extracted from I-V characteristics<br>for (a)-(c) holes and (b)-(d) electron channels. Samples: (a)-(b) MU003 ( $t_{Si} = 12$                                                                                                                                                                                                                                                                                                                      | 01       |

|      | nm, $t_{BOX} = 145$ nm, Non-passivated surface), and (c)-(d) MU005 ( $t_{Si} = 12$ nm, $t_{BOX} = 145$ nm, Passivated surface). $V_D = 20$ mV, P = 80 g.                                                                                                                                                                                                                                                                                                                                         | 32       |

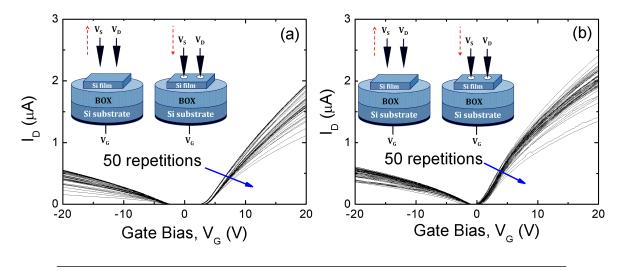

| 2.21 | Fifty consecutive current characteristics extracted as a function of the gate bias<br>for two different wafers at the same location. (a) Non-passivated and (b) passi-                                                                                                                                                                                                                                                                                                                           |          |

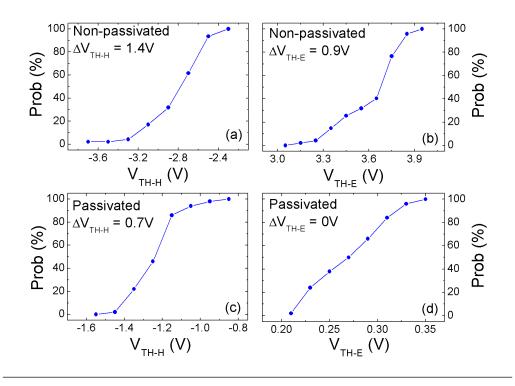

| 0.00 | vated wafers. $t_{Si} = 88 \text{ nm}, t_{BOX} = 145 \text{ nm}, V_D = 20 \text{ mV}. \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                               | 33       |

| 2.22 | Cumulative representations of $V_{TH-H}$ and $V_{TH-E}$ for two samples. (a) Non-<br>passivated and (b) passivated wafer. $t_{Si} = 88 \text{ nm}, t_{BOX} = 145 \text{ nm}, V_D = 20 \text{ mV},$<br>P = 80  g.                                                                                                                                                                                                                                                                                 | 33       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

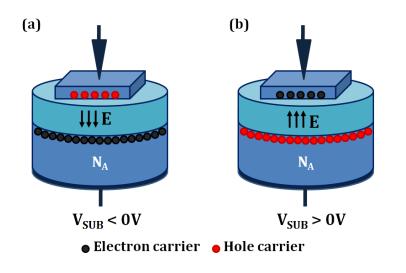

| 3.1  | The SOI sample can be treated as a capacitor formed by the BOX and the Silicon layers. The direction of the electric field depends on the polarity of the DC bias applied through the impedance analyzer.                                                                                                                                   | 36       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

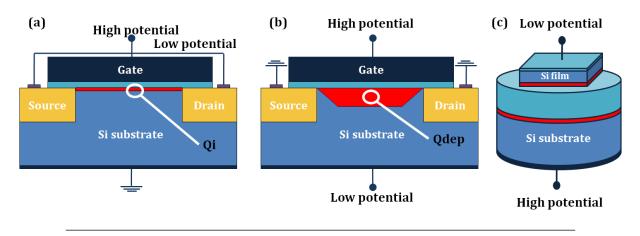

| 3.2  | Schematic of the configurations used for the extraction of the (a) gate-to-channel<br>and (b) gate-to-substrate capacitance in bulk MOSFETs. The connection of the<br>low and high potentials are pointed out in each case. (c) Comparison with the<br>SOI wafer case.                                                                      | 36       |

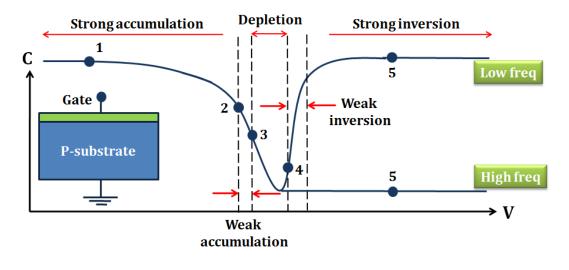

| 3.3  | C-V relation for an n-channel MOS capacitor as a function of the bias applied to the gate.                                                                                                                                                                                                                                                  | 37       |

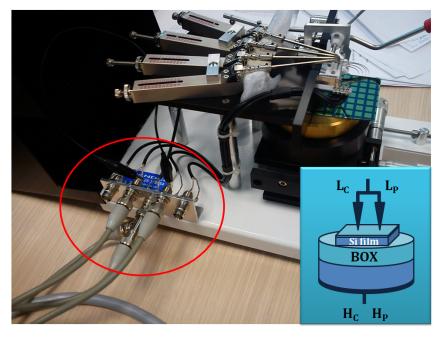

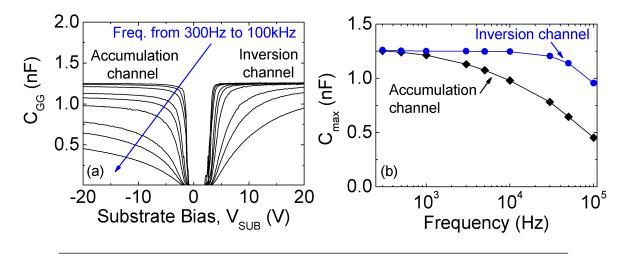

| 3.4  | Experimental setup of how capacitance measurements were adapted to the Pseudo-<br>MOSFET configuration.                                                                                                                                                                                                                                     | 38       |

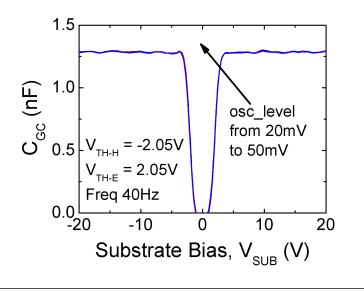

| 3.5  | Gate-to-channel capacitance curves obtained using a two-needle configuration when the AC level is modified from 20 mV to 50 mV (step 10 mV). Non-passivated wafer, $t_{Si} = 88$ nm, $t_{BOX} = 145$ nm.                                                                                                                                    | 39       |

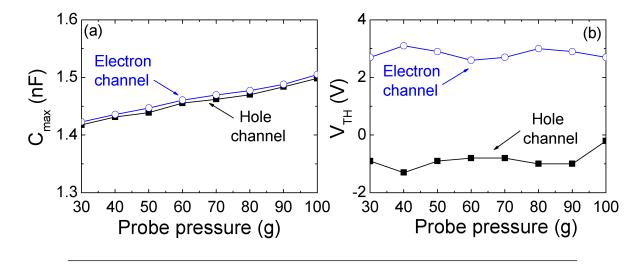

| 3.6  | (a) Maximum capacitance values at 100Hz and (b) threshold voltages for hole and electron channels obtained as a function of the probe pressure in a two-needle configuration. Non-passivated wafer, $t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, Freq. 100 Hz.                                                                                     | 40       |

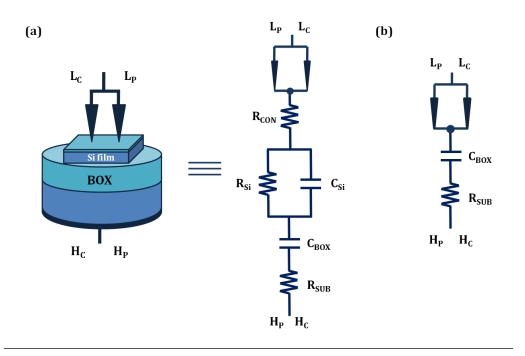

| 3.7  | (a) Equivalent impedance circuit associated to a Pseudo-MOS structure. (b) Simplified impedance model used in this work.                                                                                                                                                                                                                    | 41       |

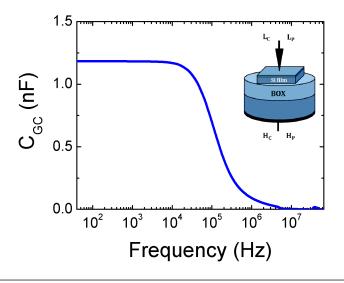

| 3.8  | Capacitance curves measured using one needle on the surface as a function of the excitation signal frequency from 40 Hz to 60 MHz.                                                                                                                                                                                                          | 41       |

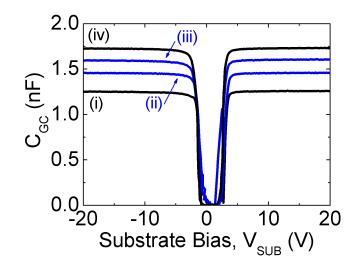

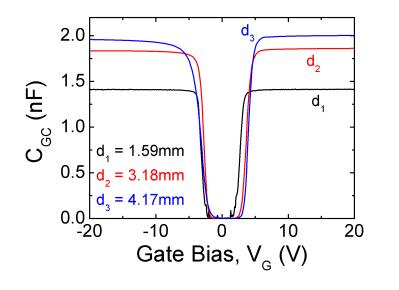

| 3.9  | Experimental capacitance characteristics with: case (i), one needle on the surface;<br>case (ii), two needles on the surface separated $d = 1.59$ mm; and case (iii), $d = 3.18$ mm; case (iv), three needles separated $d = 1.59$ mm. Non-passivated wafer,<br>$t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, oscillation level 20 mV.              | 42       |

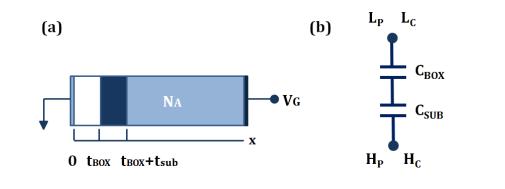

| 3.10 | (a) When the frequency is high enough, a depletion region in the substrate of a                                                                                                                                                                                                                                                             |          |

| 3.11 | SOI wafer appears. (b) Electrical equivalent circuit                                                                                                                                                                                                                                                                                        | 43<br>43 |

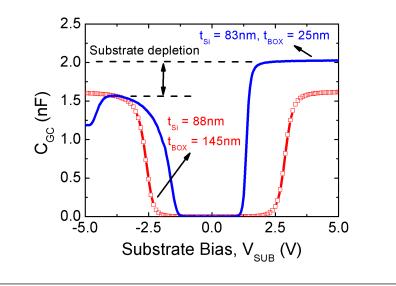

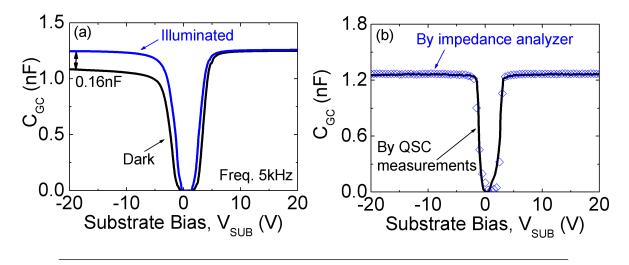

| 3.12 | (a) Gate-to-channel capacitance curves as a function of the substrate bias ob-<br>tained for different frequencies using one needle on the surface. (b) Maximum<br>value of the curves obtained as a function of the frequency. Non-passivated wafer,<br>$t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, oscillation level 20 mV                      | 45       |

| 3.13 | (a) Variation of the capacitance characteristics when the wafer is illuminated<br>and when it is not. (b) Gate-to-channel capacitance curves as a function of the<br>substrate bias obtained by the impedance analyzer at 300 Hz (dashed lines) and<br>by QSC measurements (continuous line). Non-passivated wafer, $t_{Si} = 88$ nm,       |          |

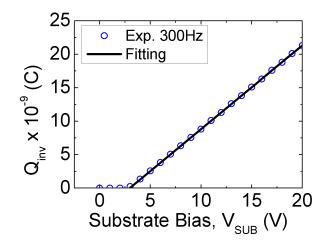

| 3.14 | $t_{BOX} = 145$ nm, oscilation level 20 mV                                                                                                                                                                                                                                                                                                  | 46       |

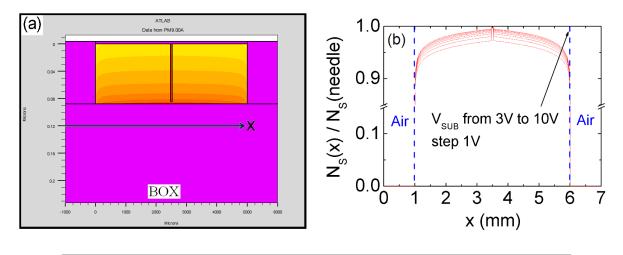

| 3.15 | sions of the cell and interface states at borders. $t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, $V_{SUB} = 10$ V. (b) Ratio between the concentration along the film and the concentration in the needle (at 84 nm depth from the Si surface) for substrate biases from 3 V to 10 V. The doping concentrations for the silicon film and the needle | 47       |

|      | region are per surface unit.                                                                                                                                                                                                                                                                                                                | 48       |

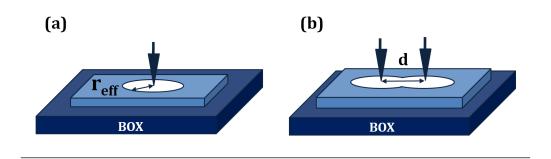

| 3.16 | Schematic representation of the area covered by the carriers in (a) single-needle<br>and (b) two-needle configurations.                                                                                                                                                                                                                                                                                                                                                        | 49       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

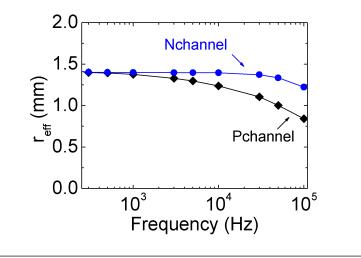

| 3.17 | Effective radius extracted from capacitance curves used for Figure 3.12.(a). Non-                                                                                                                                                                                                                                                                                                                                                                                              |          |

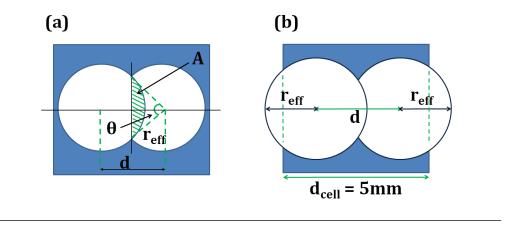

| 3.18 | passivated wafer, $t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, oscillation level 20 mV Schematics illustrating the definition of the effective surface, $S_{eff}$ for two needles placed on the surface. (a) When an overlap occurs, the region A must be sub-tracted twice. (b) The physical boundaries of the etched silicon island limit the                                                                                                                                       | 49       |

| 3.19 | effective surface for large needle separation.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50       |

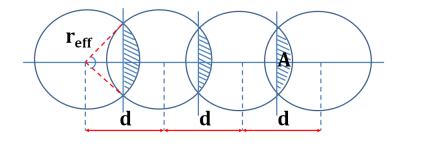

|      | guration. To do this, it was necessary to take the number of the probes used in<br>the measurements into account and also the number of the overlapped regions.                                                                                                                                                                                                                                                                                                                | 51       |

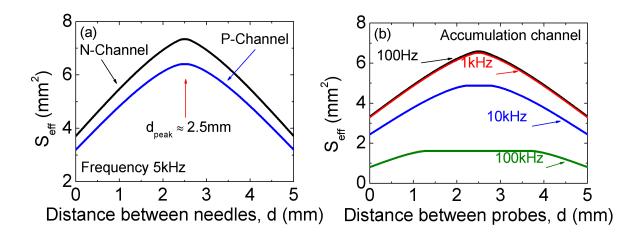

| 3.20 | (a) Effective surface obtained using the model proposed in Eqs. [3.10]-[3.13]. $S_{eff}$ increases and decreases depending on the influence of the overlap and border regions ( $d_{cell} = 5 \text{ mm}$ ). (b) Effective surface simulated with the model proposed considering several frequencies. If the frequency is high enough, the maximum value of $S_{eff}$ will be the sum of the areas generated by each probe (a constant value in a certain range of distances). | 52       |

| 3.21 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53       |

| 3.22 | (a) Effective surface in three-needle configuration. (b) Extracted effective surface by using Eq. [3.6] with three needles placed on the wafer surface and the model                                                                                                                                                                                                                                                                                                           |          |

| 3.23 | proposed in Eq. [3.14]. Non-passivated wafer, $t_{Si} = 88 \text{ nm}$ , $t_{BOX} = 145 \text{ nm}$ Comparison between mobility results obtained using in Eq. [3.15] the $S_{eff}$ value measured by two-needle configuration (black line), and the theoretical $S_{eff}$ value calculated using Eq. [3.10] where the effective radius was measured in one-needle configuration (open symbols). Non-passivated wafer, $t_{Si} = 88 \text{ nm}$ , $t_{BOX} = 145$               | 53       |

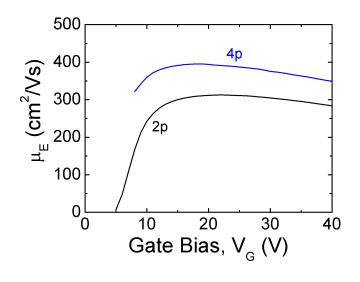

| 3.24 | nm.<br>Comparison between mobility results obtained by Split-C(V) technique ( $S_{eff}$<br>calculated using Eq. [3.10], solid line), and by considering the Pseudo-MOSFET<br>area ( $S_{eff} = 0.75 \times d^2$ , dashed line). (a) d = 1.59mm; (b) d = 3.18mm. Non-<br>passivated wafer, $t_{Si} = 88$ nm, $t_{BOX} = 145$ nm, freq = 300 Hz.                                                                                                                                 | 54<br>55 |

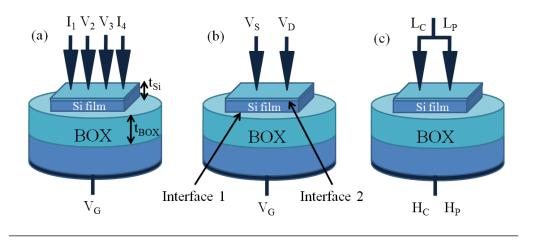

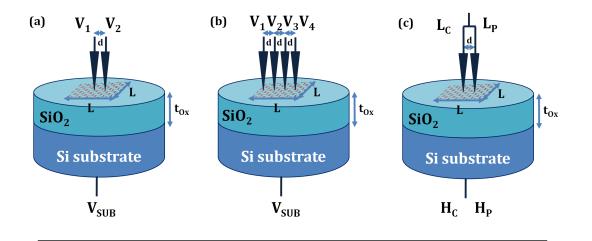

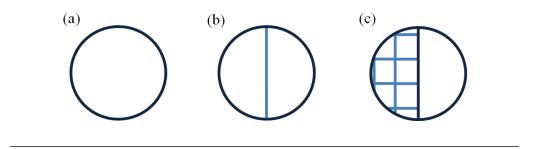

| 4.1  | Point-contact characterization methods on bare SOI wafers: (a) four point-contact configuration, (b) two point-contact configuration (Pseudo-MOSFET technique), and (c) configuration for Split-C(V) measurements when two needles are employed. $C$ and $P$ represents the current and voltage connections respectively                                                                                                                                                       | 58       |

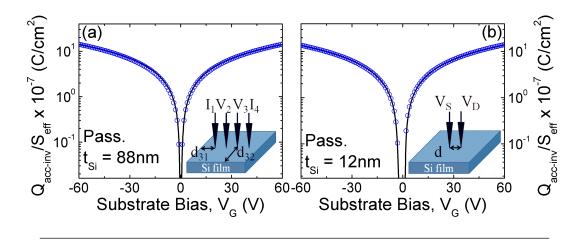

| 4.2  | Comparison of the accumulation/inversion charge per area unit obtained from<br>experimental results by the Split-C(V) technique (solid lines) and from simu-<br>lations after calibration (open symbols), as a function of the substrate bias for the<br>passivated wafers considered. (a) Four-needle configuration, $t_{Si} = 88$ nm. The<br>distances $d_{31} \approx 0.12$ mm and $d_{32} \approx 2.5$ mm represent the separation between the                             |          |

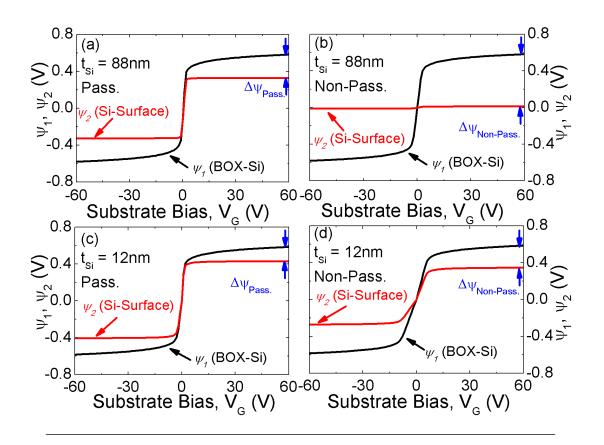

| 4.3  | contacts and the Si-island edges. (b) Pseudo-MOSFET configuration, $t_{Si} = 12$<br>nm. Distance between contacts $d = 1.59$ mm. $t_{BOX} = 145$ nm Electrostatic potential obtained from numerical simulations at BOX/Si-film ( $\psi_1$ ) and Si-film/native oxide ( $\psi_2$ ) interfaces as a function of the substrate bias. Passivated wafers (a) & (c), non-passivated wafers (b) & (d). $t_{Si} = 88$ nm (a) & (b),                                                    | 60       |

|      | $t_{Si} = 12 \text{ nm}$ (c) & (d). $t_{BOX} = 145 \text{ nm}$                                                                                                                                                                                                                                                                                                                                                                                                                 | 60       |

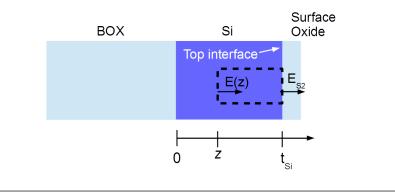

| 4.4 | Vertical cross-section of the Silicon-On-Insulator structure (BOX/Si/Surface-Oxide) A Gauss surface (dashed lines) enclosing the Si/surface-oxide interface and the Silicon film is considered to determine the local electric field at a position $z$                                                                                                                                                                                                                                                             | 61       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

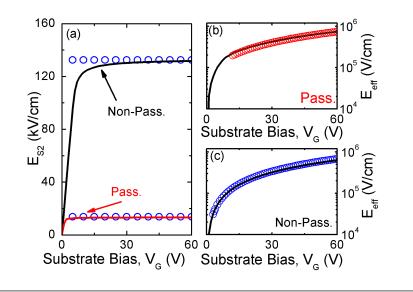

| 4.5 | (a) Comparisons between $E_{S2}$ as a function of the substrate voltage for passivated<br>and non-passivated SOI wafers from simulation data (solid line), and using the<br>semi-empirical model of Eq. [4.7] (open symbols). (b) & (c) Comparisons between<br>the effective electric field obtained by Eq. (4.6) using the simulation results (solid<br>line), and by Eq. (4.7), employing the experimental data above the threshold                                                                              |          |

|     | condition (open symbols). $t_{Si} = 12$ nm. $t_{BOX} = 145$ nm                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63       |

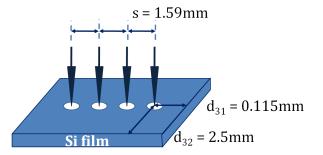

| 4.6 | Distances from the needles to the edges of the cell when a 4-point configuration                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64       |

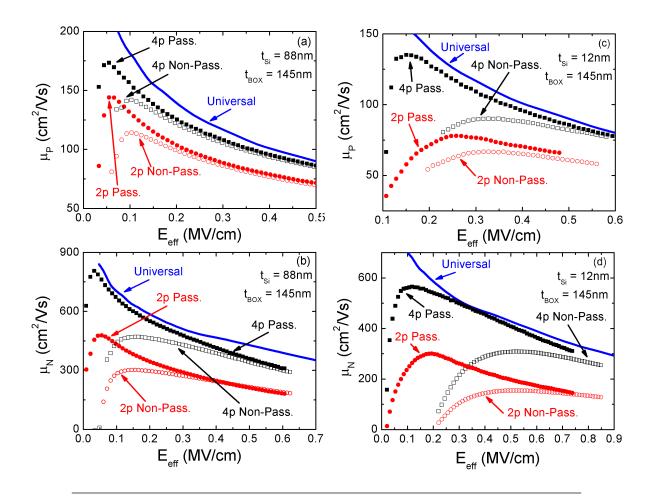

| 4.7 | is performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64<br>65 |

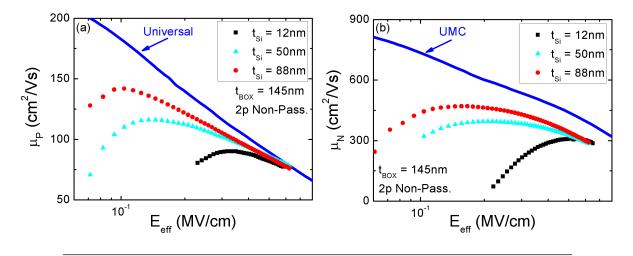

| 4.8 | Experimental mobility curves for (a) holes and (b) electrons versus the effective electric field (logarithmic scale) for three different non-passivated SOI samples. The extraction is based on a two point-contact (Pseudo-MOSFET) setup with the adequate geometric factors $fg$ from Table 4.2. Substrate bias was modified from from 0 to $-60$ V and from 0 to $+60$ V for the hole and electron channels characterization respectively. $t_{BOX} = 145$ nm. UMC curves are included for comparison [TTIT94]. | 67       |

| 5.1 | Schematic illustration of (a) crystalline and (b) poly-crystalline atomic struc-<br>tures. In (a) the atoms form regular repeating arrangements. (b) is composed by                                                                                                                                                                                                                                                                                                                                                |          |

| 5.2 | numerous crystalline structures with different orientations                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70<br>71 |

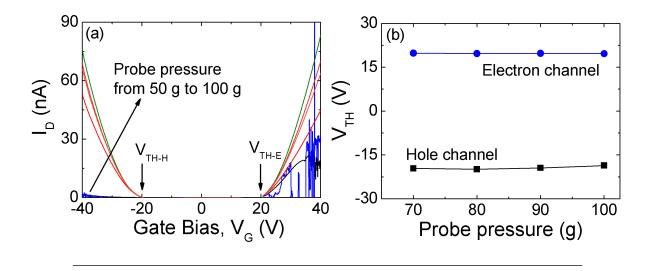

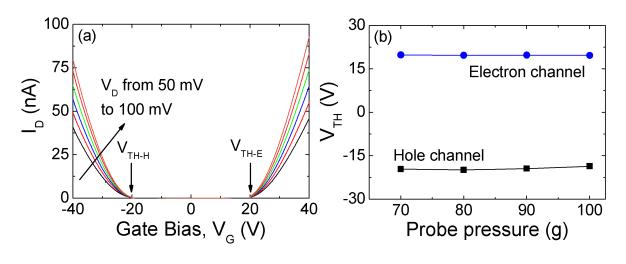

| 5.3 | (a) Current curves as a function of the gate bias when the needle pressure varies from 50 g to 100 g for different $V_D$ values. (b) Threshold voltage values obtained                                                                                                                                                                                                                                                                                                                                             |          |

| 5.4 | for the different probe pressures. $V_S = 0$ V, P = 90 g                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71       |

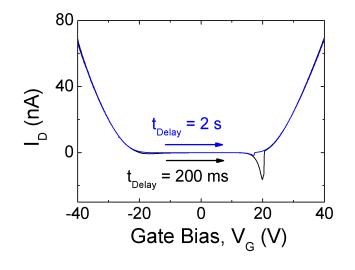

|     | two values: 100 ms, and 2 s. $V_D = 100 \text{ mV}, V_S = 0 \text{ V}, P = 90 \text{ g.} \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                        | 72       |

| 5.5 | Image of the graphene in one of the samples used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73       |

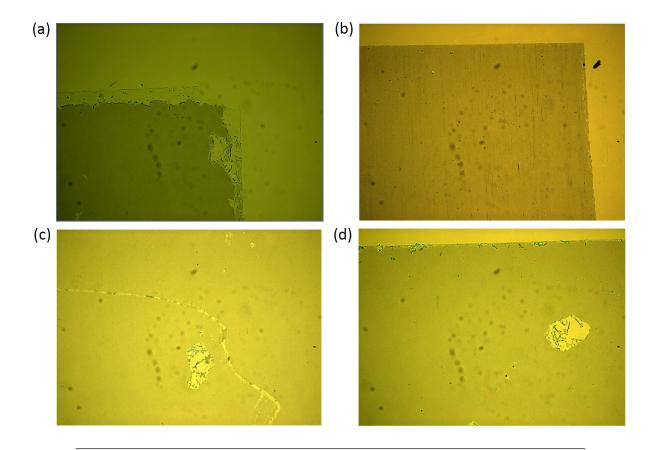

| 5.6 | (a)-(d) Microscope images of the graphene in one of the samples used taken lens<br>100X objective.                                                                                                                                                                                                                                                                                                                                                                                                                 | 74       |

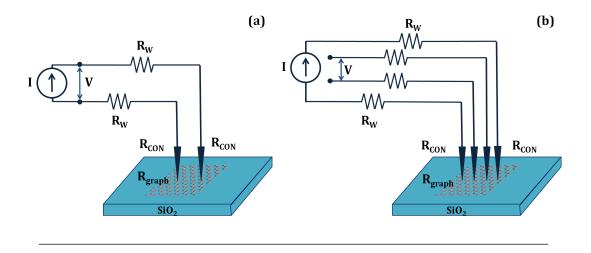

| 5.7 | Schematic of the (a) two point-contact and (b) four point-contact techniques used<br>to extract I-V characteristics for electrical characterization of graphene layers. (c)<br>Setup employed for capacitance measurements.                                                                                                                                                                                                                                                                                        | 74       |

| 5.8 | (a) Image of one of the graphene samples positioned on the metallic chuck of the                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|     | Janis station. (b) The microscope facilitates the location of the needles on the sample.                                                                                                                                                                                                                                                                                                                                                                                                                           | 75       |

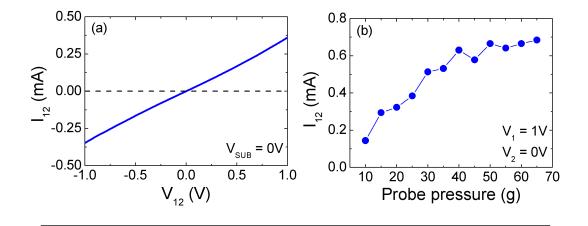

| 5.9  | (a) Current obtained when a two-needle configuration is employed in a square shaped graphene layer on insulator layer satisfying $d \ll L$ . (b) Current as a function of the needle pressure for $V_{12} = 1$ V. The current remains saturated above 50 g. Higher pressures only contribute to damage the underneath $SiO_2$ layer until physical breakdown. $V_{222} = 0$ V. $d = 1.50$ mm | 76       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

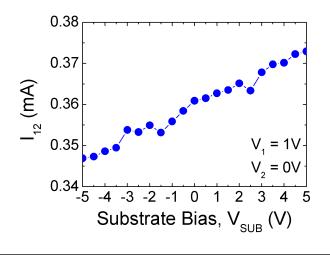

| 5.10 | layer until physical breakdown. $V_{SUB} = 0$ V, d = 1.59 mm Drain current at a given bias point as a function of the substrate bias from -5 V to 5 V. $t_{BOX} = 90$ nm, $N_{D-substrate} = 10^{18} cm^{-3}$                                                                                                                                                                                | 76<br>76 |

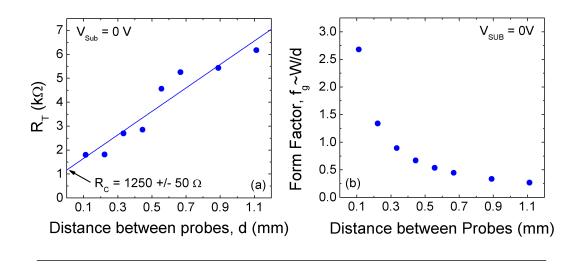

|      | Schematic of (a) two-terminal and (b) four-terminal resistance measurements (a) Total resistance between probes for two-point contact configuration as a function of the probe separation. Linear regression for $d = \theta$ allows the extraction of the contact resistance. (b) Form factor of the current flow for two-point con-                                                        | 77       |

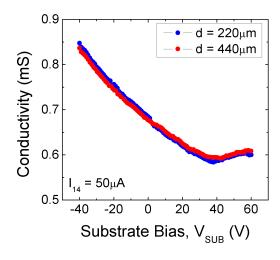

| 5.13 | tact configuration extracted combining four-probe and two-probe measurements.<br>$V_{SUB} = 0 \text{ V}, t_{BOX} = 90 \text{ nm}, N_{D-substrate} = 10^{18} \text{ cm}^{-3}.$                                                                                                                                                                                                                | 78       |

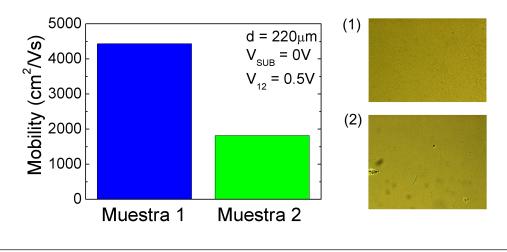

| 5.14 | 440 $\mu$ m. $t_{BOX} = 90$ nm, $N_{D-substrate} = 10^{18} cm^{-3}$ .<br>Carrier mobility extracted by the proposed four-point contact configuration for                                                                                                                                                                                                                                     | 79       |

| 5.15 | clean and contaminated samples of graphene and the actual microscope images<br>of them. $t_{BOX} = 90$ nm, $N_{D-substrate} = 10^{18} cm^{-3}$                                                                                                                                                                                                                                               | 79       |

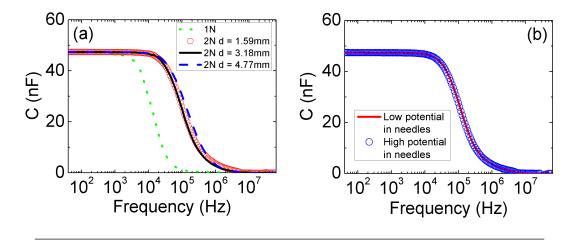

|      | one and two needles and considering several distances between them. (b) Ex-<br>changing the high and low potentials in the experimental setup. $t_{BOX} = 90$ nm,<br>$N_{D-substrate} = 10^{18} cm^{-3}$ .                                                                                                                                                                                   | 80       |

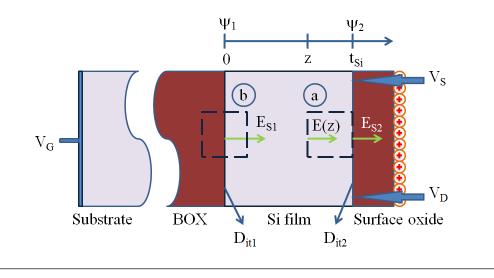

| 5.16 | technique: $V_S$ is the source voltage and $V_D$ is the drain voltage, both applied<br>by pressure adjustable probes; $V_G$ is the gate (substrate) voltage. $D_{it1}$ and $D_{it2}$<br>represent the density of interface states at BOX/Si film and Si film/top surface<br>interfaces respectively. Two Gaussian surfaces in both edges of the Si film (dashed                              | 01       |

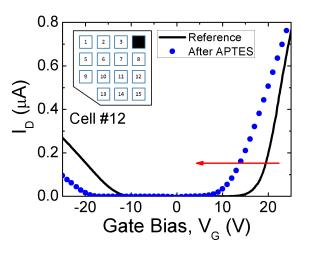

| 5.17 | line, (a) and (b)) are represented                                                                                                                                                                                                                                                                                                                                                           |          |

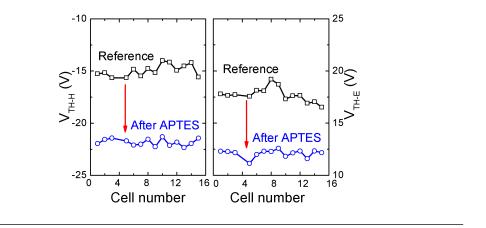

| 5.18 | nm.<br>Threshold voltages for hole (left) and electron (right) channels extracted from the $I_D(V_G)$ curves before (squares) and after (circles) the APTES layer is created on the native oxide of the cells. 15 cells were probed. $t_{Si} = 12$ nm, $t_{BOX} = 145$                                                                                                                       | 83       |

|      | nm                                                                                                                                                                                                                                                                                                                                                                                           | 84       |

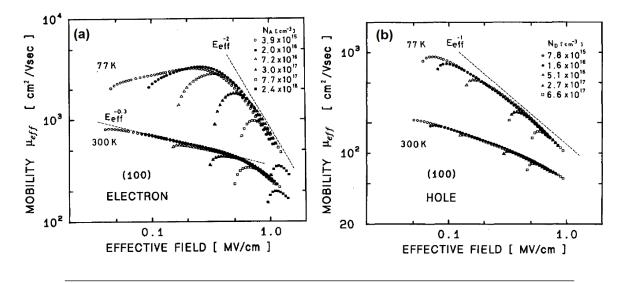

| A.1  | UMC curves from [TTIT94]. (a) Electron mobility in the inversion layer at 300 K and 77 K versus effective field $E_{eff}$ , as a function of substrate acceptor concentration $N_A$ . (b) Hole mobility in the inversion layer at 300 K and 77 K versus effective field $E_{eff}$ , as a parameter of substrate donor concentration $N_D$ .                                                  | 90       |

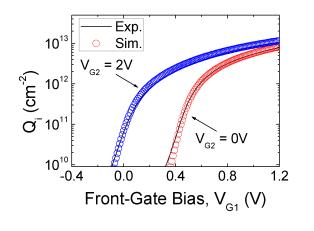

| A.2  | Comparison of the inversion charge concentration as a function of the front-gate<br>bias between the experimental results (open-symbols), calculated by the Split-<br>C(V) technique, and simulation results (solid-lines) obtained after the calibration<br>of the solver. Back-gate bias: $V_{G2} = 0$ V and $V_{G2} = 2$ V. $t_{Si} = 8$ nm, $t_{BOX} = 10$                               |          |

|      | nm, $L = W = 10 \ \mu$ m, EOT = 1.3 nm                                                                                                                                                                                                                                                                                                                                                       | 91       |

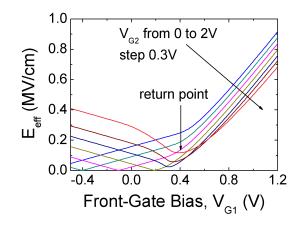

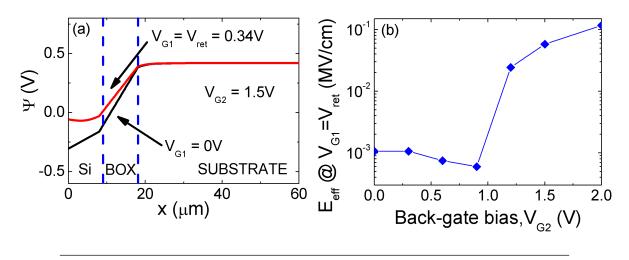

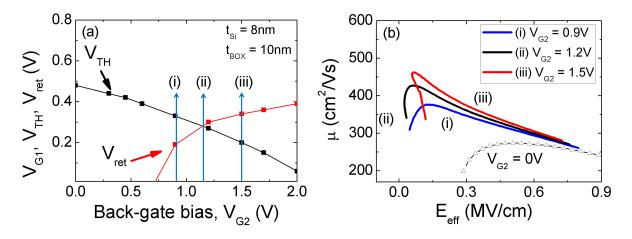

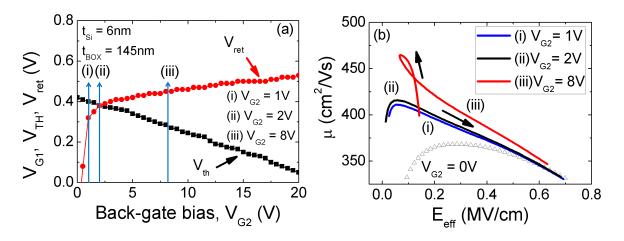

| A.3         | Effective field evaluated with Eq. (A.1) versus front-gate bias for different values<br>of $V_{G2}$ (0 V, 0.3 V, 0.6 V, 0.9 V, 1.2 V, 1.5 V, 2 V). For $V_{G2} > 0$ V, two<br>different front-gate biases lead to the same $E_{eff}$ value. $t_{Si} = 8$ nm, $t_{BOX} = 10$<br>nm, $L = W = 10 \ \mu\text{m}$ , EOT = 1.3 nm | 92       |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| A.4         | (a) Electrostatic potential cross section for two values of front-gate bias ( $V_{G1} = 0$<br>V and $V_{G1} = V_{ret} = 0.34$ V) when $V_{G2} = 1.5$ V. (b) Effective field evaluated at<br>the return point as a function of back-gate bias. $t_{Si} = 8$ nm, $t_{BOX} = 10$ nm,                                            | 02       |

| A.5         | $L = W = 10 \ \mu \text{m}$ , EOT = 1.3 nm                                                                                                                                                                                                                                                                                   | 92       |

| A.6         | nm, $L = W = 10 \ \mu\text{m}$ , EOT = 1.3 nm                                                                                                                                                                                                                                                                                | 93<br>94 |

| <b>B</b> .1 | Photography of the front of the CITIC-UGR building.                                                                                                                                                                                                                                                                          | 97       |

| B.2         | Front and back view of the Agilent B1500A Semiconductor Analyzer                                                                                                                                                                                                                                                             | 98       |

| B.3         | EASYExpert software.                                                                                                                                                                                                                                                                                                         | 98       |

| B.4         | Front and back view of the Keithley 4200-SCS Parameter Analyzer.                                                                                                                                                                                                                                                             | 99       |

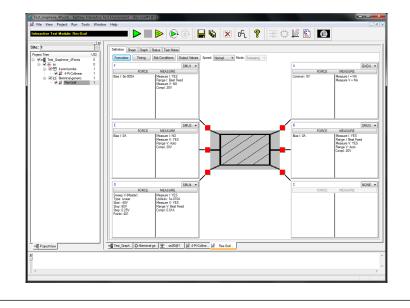

| B.5         | Keithley interactive test environment.                                                                                                                                                                                                                                                                                       | 99       |

| B.6         | SMU plug-in module from B1500A equipment.                                                                                                                                                                                                                                                                                    |          |

| B.7         | Conductors inside a triaxial cable.                                                                                                                                                                                                                                                                                          |          |

| B.8<br>B.9  | Front and back view of the Impedance Analyzer 4294A                                                                                                                                                                                                                                                                          |          |

| -           | Jandel point-contact system where Pseudo-MOSFET technique is carried out.                                                                                                                                                                                                                                                    |          |

|             | Janis micro-manipulated probe station.                                                                                                                                                                                                                                                                                       |          |

|             | BNC-triaxial adapter.                                                                                                                                                                                                                                                                                                        |          |

| B.13        | One of the Pseudo-MOSFET samples available in the nanoelectronics laboratory.<br>Semi-automatic probe system by Suss Microtec. This equipment provides a per-<br>fect environment for an accurate wafer current and capacitance low-noise mea-                                                                               | 103      |

| B.15        | surements.       Nikon Microscope ECLIPSE LV150N.                                                                                                                                                                                                                                                                            |          |