# High-Performance Scientific Computing on FPGA aboard the *Solar Orbiter* PHI Instrument

**Tesis Doctoral**

Programa Oficial de Posgrado Ciencias de la Computación y Tecnología Informática

#### Juan Pedro Cobos Carrascosa

Granada, Noviembre de 2015

INSTITUTO DE ASTROFÍSICA DE ANDALUCÍA CONSEJO SUPERIOR DE INVESTIGACIONES CIENTÍFICAS

DEPARTAMENTO DE ARQUITECTURA Y TECNOLOGÍA DE COMPUTADORES UNIVERSIDAD DE GRANADA

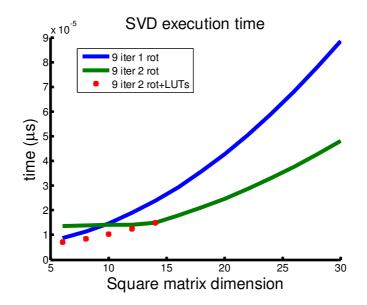

Editor: Universidad de Granada. Tesis Doctorales Autor: Juan Pedro Cobos Carrascosa ISBN: 978-84-9125-776-9 URI: http://hdl.handle.net/10481/43508

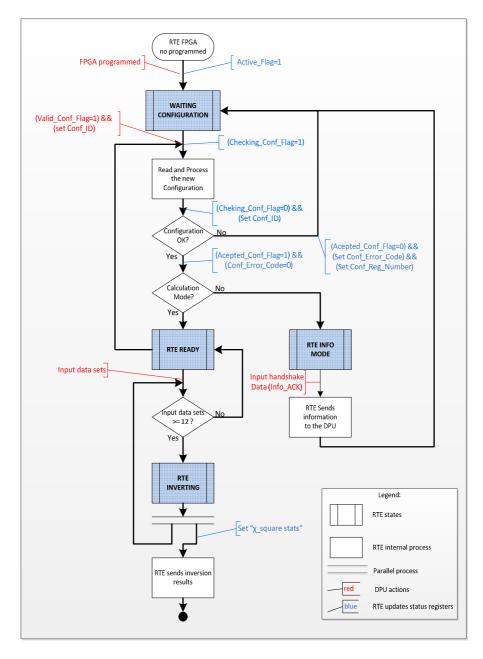

### Tesis Doctoral

## Programa Oficial de Posgrado Ciencias de la Computación y Tecnología Informática

## High-Performance Scientific Computing on FPGA aboard the *Solar Orbiter* PHI Instrument

Autor:

D. Juan Pedro Cobos Carrascosa

Directores:

Dr. D. Antonio C. López Jiménez

Dr. D. Christian A. Morillas Gutiérrez

Granada, Noviembre de 2015

Instituto de Astrofísica de Andalucía Consejo Superior de Investigaciones Científicas

Departamento de Arquitectura y Tecnología de Computadores Universidad de Granada

El doctorando, Juan Pedro Cobos Carrascosa, y los directores de la tesis, Antonio C. López Jiménez y Christian A. Morillas Gutiérrez, garantizamos, al firmar esta tesis doctoral, que el trabajo ha sido realizado por el doctorando bajo la dirección de los directores de la tesis y hasta donde nuestro conocimiento alcanza, en la realización del trabajo, se han respetado los derechos de otros autores a ser citados, cuando se han utilizado sus resultados o publicaciones.

Granada, 12 de noviembre de 2015

Director/es de la Tesis

Doctorando

Fdo.: Antonio C. López Jiménez Christian A. Morillas Gutiérrez Fdo.: Juan Pedro Cobos Carrascosa

A Pablo, Adrián y Esther

Quiero aprovechar esta oportunidad para agradecer de la forma más sincera, y por igual, a todas las personas que por su ayuda, o ánimos, han hecho posible este trabajo. Aun así, me gustaría hacer algunas menciones especiales de agradecimiento a quienes han sido fundamentales.

Al Dr. Jose Carlos del Toro, por poner sobre mis hombros toda la responsabilidad que conlleva este apasionante e increíble reto, por toda la confianza que siempre me ha dado para llevarlo a cabo y, por supuesto, por su inconmensurable ayuda. Todo ello ha sido la motivación que me ha hecho esforzarme al máximo en este trabajo y, sobre todo, disfrutar haciéndolo.

A Ramos y Bea, a Bea y Ramos, compañeros infatigables en esta aventura. Junto a los que empujar hacia delante codo con codo ha sido un placer.

Al Dr. Antonio López, por la dirección de esta tesis, por sus siempre certeros consejos y por el espléndido ambiente de trabajo que ha creado en el IAA.

Al Dr. Christian Morillas y al profesor Francisco Pelayo, por la motivación que me dieron siendo estudiante, por llevarme al mundo de la investigación en tecnología y, por supuesto, por sus revisiones y consejos.

Al IAA SO/PHI Team quienes contagian su ilusión y que con su ingente trabajo harán que un instrumento tan complejo, y de tal magnitud, como lo es SO/PHI sea un éxito. A María, Dani, Fernando, Pierre, Joaquín, Miguel, Berta y Luis.

A todos los compañeros del IAA con quienes es inspirador el trabajar, compartir despacho y convivir. A pesar de todas las barreras, trabajan desmesuradamente por hacer la mejor ciencia y tecnología posibles.

Al Dr. David Orozco por toda su ayuda y paciencia.

Para llevar a cabo esta tesis no ha sido suficiente toda esa ayuda en el plano profesional, porque sin todas las personas que me rodean nunca hubiese podido llegar hasta aquí.

A Esther, por estar siempre a mi lado y darme todo su apoyo. Por toda la alegría que me trasmite y sin quien no hubiera sido posible realizar todo este esfuerzo.

A Pablo y Adrián, cuyas risas, imaginación y energía hacen de cada día el mejor de los días.

A mi madre cuyo ejemplo de lucha y esfuerzo siempre ha sido el mejor de sus consejos.

Casi por último, y no por eso menos importante, a mis hermanos y familia, quienes siempre me han cubierto de cariño.

Y para finalizar, agradezco al Plan Nacional del Espacio y a la Junta de Andalucía por subvencionar los proyectos que han hecho posible este trabajo. Así como al Consejo Superior de Investigaciones Científicas por brindarme esta magnífica oportunidad.

SO/PHI (*Solar Orbiter* Polarimetric and Helioseismic Imager) is a filtergraph-based, solar magnetograph aimed at mapping the vector magnetic field and the line-of-sight (LOS) velocity of the solar photospheric plasma. It belongs to the scientific payload of the European Space Agency's *Solar Orbiter* mission which will orbit the Sun at 0.28 astronomical units.

The limited telemetry rate combined with the large amount of scientific information retrieved by the SO/PHI instrument demand a sophisticated on-board data reduction and scientific analysis through the study of the polarization state of a specific spectral line. The main aim is to perform the complicated algorithm needed to translate the polarization state of the light spectrum in terms of some specific solar parameters like the magnetic field vector and velocity. Technically speaking, the inference of the solar physical quantities through a spectropolarimetric study is based on the inversion of the Radiative Transfer Equation (RTE) and these tasks require the processing of a huge quantity of data in parallel.

The RTE inverter is the core of the on-board scientific data analysis and, probably, one of the most innovative parts of the instrument. Due to the unavailability of qualified for space processors, DSPs, or GPGPUs that fulfil the stringent computational requirements with the limited room and power consumption allocated to the instrument, a specifically designed hardware device has been implemented in SO/PHI. This device is in charge of inverting the RTE aboard *Solar Orbiter* under narrow time and power constraints.

The main aim of this thesis is to design, build, and test such a hardware device for SO/PHI. With that goal in mind, we propose two different high-performance computing architectures for carrying out the RTE inversion using FPGA devices embedded in the SO/PHI instrument.

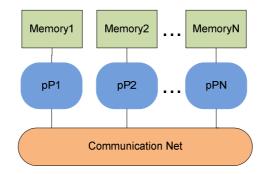

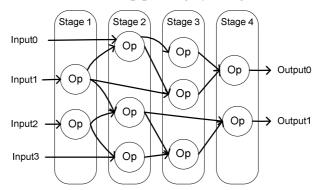

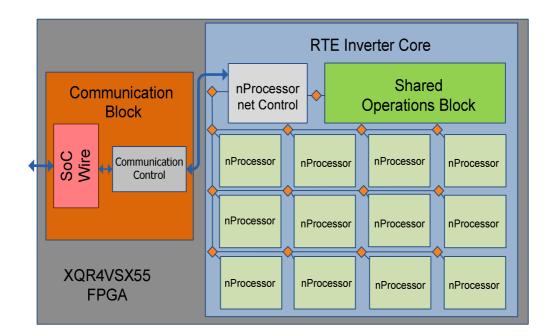

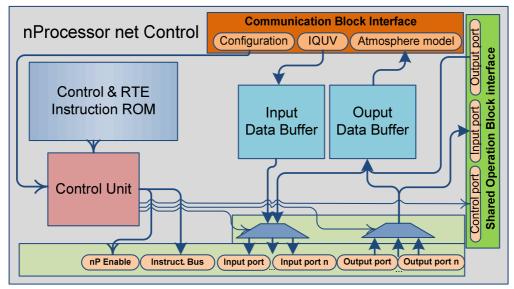

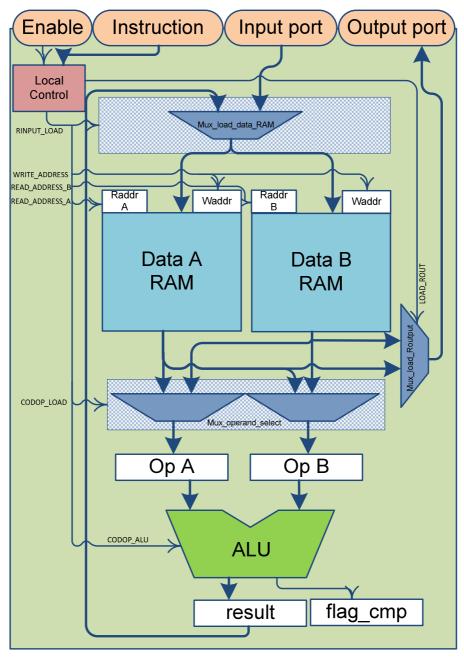

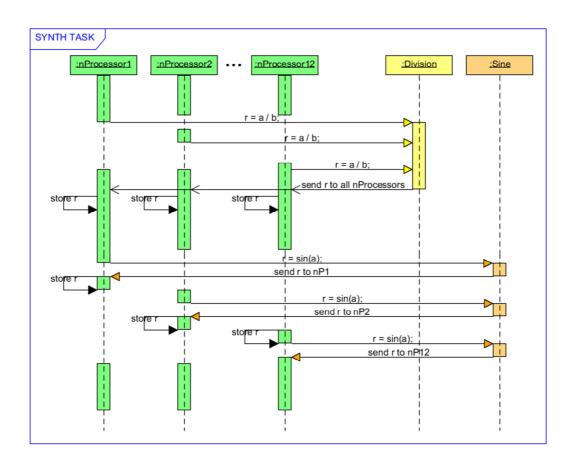

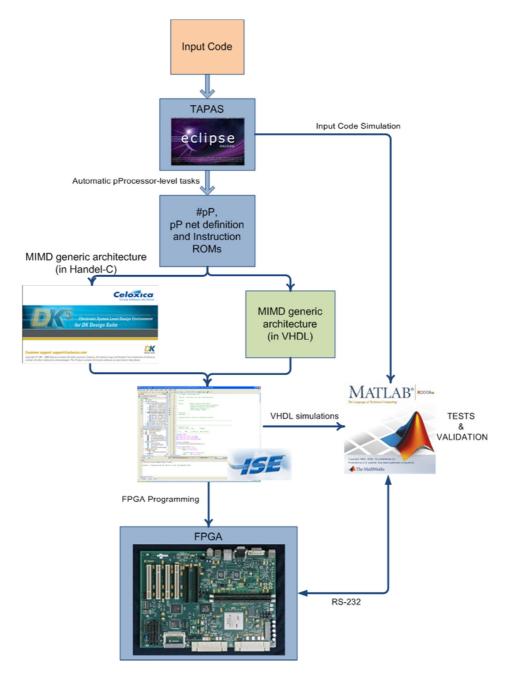

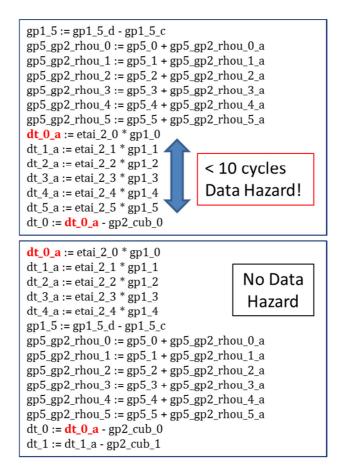

The first of these proposals is a distributed-memory MIMD multiprocessor architecture on a Virtex-5 FPGA that exploits the functional and data fine parallelism. It uses a pipelined execution based on a novel MIMD programming method. The processors within the architecture are simplified for saving resources but they are able of eliminating latency and exploiting the computing power that the FPGA provides. The synchronization and the communication network between processors have been simplified using this proposal.

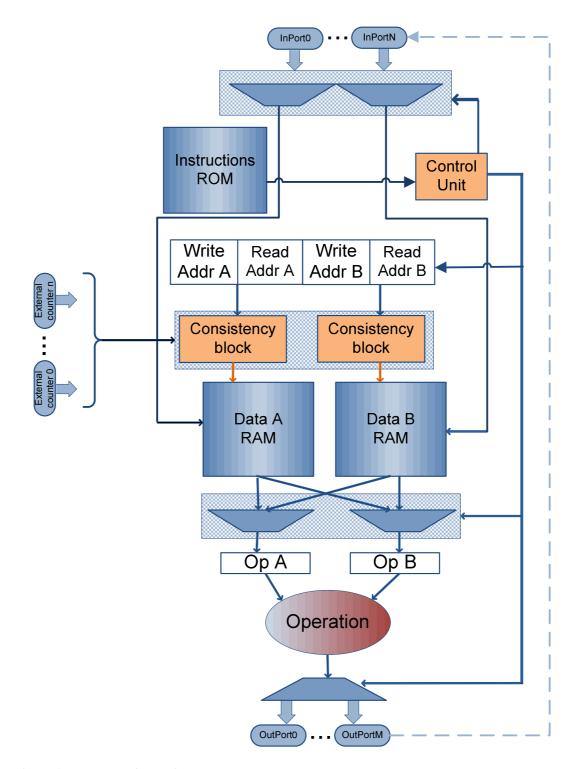

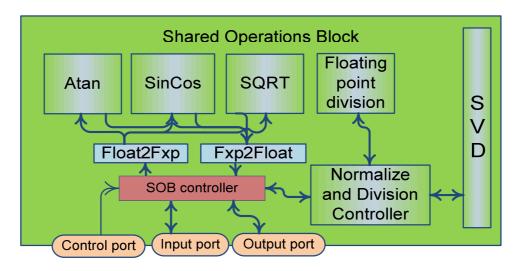

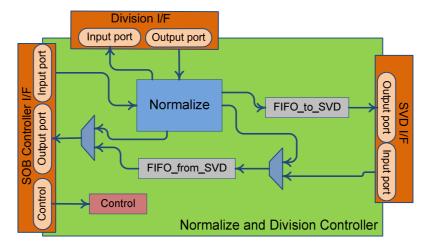

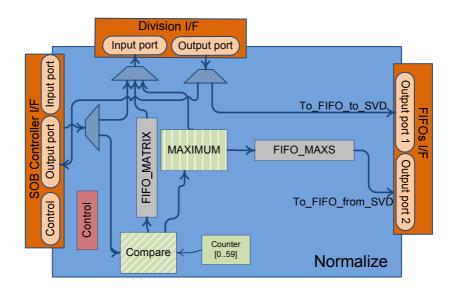

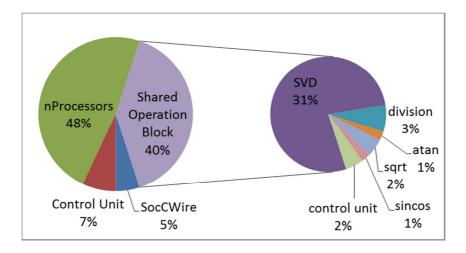

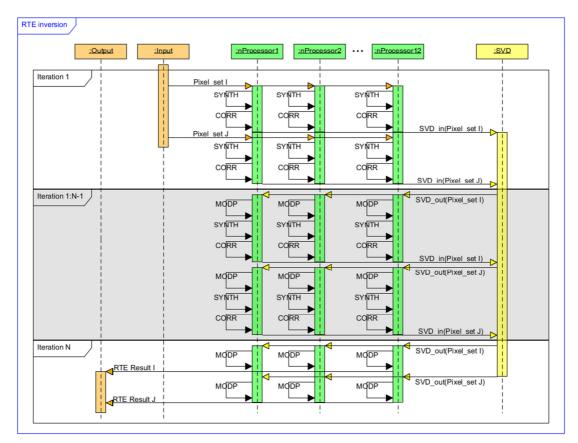

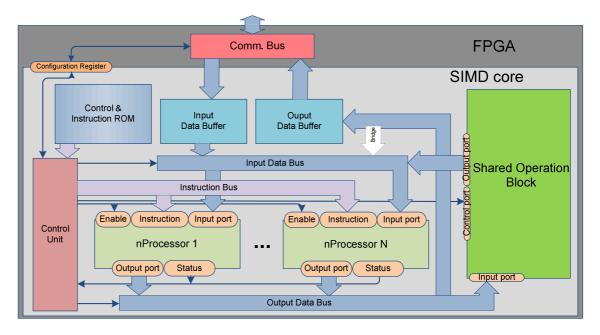

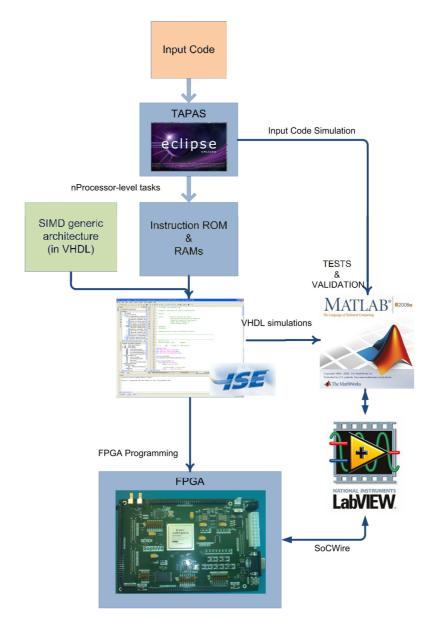

The second proposal consists of a SIMD multiprocessor architecture to reach high performance in floating point operations. This architecture on a Virtex-4 FPGA squeezes the FPGA resources in order to reach the time constraints. It is focused in exploiting the data parallelism using several processors working together and using different data streams. One of

the most important contributions of this architecture is the ability of saving resources allocating operation cores in a shared operation block, which is accessed by every processor. Some details for extending the architecture to other problems are pointed out. A study of how the radiation induced errors affect each block of the architecture is detailed, and two fault mitigation strategies are described.

We also present a novel software tool, which automates the entire design process and system settings from an input C-like pseudo-code. This tool uses advanced techniques of software pipelining and parallelizing scientific algorithms in multicore systems. A compiler within the tool makes it easier the use and programming of the proposed MIMD and SIMD architectures.

As a byproduct of our development, a specific, novel Singular Value Decomposition (SVD) architecture within the SIMD architecture is proposed as well. SVD is one of the steps in the RTE inversion but can be of interest to other developments as is a fairly common mathematical tool.

The achieved FPGA systems improve the time and power consumption of ground-based systems based on commercial CPUs.

The final system is tested using synthetic and real data. It satisfies the scientific precision requirements and the engineering computing time and power consumption requirements.

SO/PHI (*Solar Orbiter* Polarimetric and Helioseismic Imager) es un magnetógrafo, basado en un filtrógrafo, destinado a crear mapas del vector campo magnético y de la velocidad del plasma solar a lo largo de la línea de visión. Pertenece a la carga útil científica de la misión *Solar Orbiter* de la Agencia Espacial Europea, la cual orbitará el Sol a una distancia de 0,28 unidades astronómicas.

La limitación en la tasa de telemetría combinada con la gran cantidad de información científica obtenida por el instrumento SO/PHI requieren que se realice a bordo una sofisticada reducción de datos y un análisis científico a través del estudio del estado de polarización de una específica línea espectral. El principal objetivo es realizar el complicado algoritmo necesario para trasladar el estado de polarización del espectro de la luz a términos de algunos parámetros solares específicos como el campo magnético y velocidad. Técnicamente hablando, la inferencia de las magnitudes físicas solares a través de un estudio espectropolarimétrico está basada en la inversión de la ecuación de transporte radiativo (RTE) y estas tareas requieren del procesamiento de una gran cantidad de datos en paralelo.

El inversor RTE es el núcleo del análisis científico a bordo y, probablemente, una de las partes más innovadoras del instrumento. Debido a la inexistencia de procesadores, DSPs o GPGPUs cualificados para el espacio que cumplan con los exigentes requisitos de cómputo, de limitación de espacio y de consumo de potencia del instrumento, ha sido necesario el desarrollado un dispositivo hardware específico para SO/PHI. Este dispositivo es el encargado de invertir la ecuación RTE a bordo de Solar Orbiter bajo estrechas limitaciones de tiempo y potencia.

El objetivo principal de esta tesis es diseñar, construir y probar tal dispositivo hardware para SO/PHI. Con ese objetivo en mente, proponemos dos arquitecturas de cálculo científico de altas prestaciones para llevar a cabo la inversión RTE usando dispositivos FPGA embebidos en el instrumento SO/PHI.

La primera de estas propuestas es un arquitectura multiprocesador tipo MIMD de memoria distribuida en FPGA que explota el paralelismo fino a nivel de datos y funcional. Usa una ejecución segmentada basada en un innovador método de programación MIMD. Los procesadores de la arquitectura son simplificados para ahorrar recursos pero son capaces de eliminar latencias y de explotar la potencia de cálculo que la FPGA provee. Usando esta propuesta se simplifica la sincronización entre procesadores y la red de comunicaciones.

La segunda propuesta consiste de una arquitectura multiprocesador tipo SIMD para alcanzar alto rendimiento en las operaciones en coma flotante. Esta arquitectura en la FPGA Virtex-4 exprime los recursos de la FPGA para alcanzar las restricciones de tiempo. Está enfocada en explotar el paralelismo de datos usando varios procesadores que trabajan juntos y usan diferentes flujos de datos. Una de las contribuciones más importantes de esta arquitectura es la habilidad de ahorrar recursos alojando núcleos de operación en un bloque de operaciones compartidas, el cual es accedido por todos los procesadores. También se dan propuestas para extender la arquitectura a otros problemas y se hace un estudio detallado de como los errores inducidos por radiación afectan a cada bloque de la arquitectura. Además se describen dos estrategias para mitigar errores.

También presentamos una innovadora herramienta software, la cual automatiza completamente el proceso de diseño y la configuración del sistema para un seudocódigo de entrada tipo C. Esta herramienta usa técnicas avanzadas de segmentación de software y paralelización de algoritmos científicos en sistemas multiprocesador. El compilador que forma parte de la herramienta facilita el uso y programación de las arquitecturas propuestas SIMD y MIMD.

Como un subproducto de este desarrollo también se ha generado una arquitectura innovadora para el cálculo de la descomposición en valores singulares (SVD) de una matriz que se aloja en la arquitectura SIMD. El cálculo del SVD es uno de los pasos dentro de la inversión RTE pero puede ser de interés para otros desarrollos ya que es justamente una herramienta matemática muy común.

El sistema en FPGA obtenido mejora el tiempo y consumo de potencia de los sistemas terrestres basados en ordenadores comerciales.

Finalmente, se presentan los resultados obtenidos usando datos sintéticos y reales. Se ha comprobado que se satisfacen los requisitos de precisión científica, de tiempo de cálculo y de consumo de potencia.

## High-Performance Scientific Computing on FPGA Aboard the

### Solar Orbiter PHI Instrument

#### **Table of Contents**

| А                                           | Abstracti                                                                                                                                        |                                                                                                                                                                                                                                                                |                               |  |  |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|

| Resumeniii                                  |                                                                                                                                                  |                                                                                                                                                                                                                                                                |                               |  |  |  |

| 1                                           | Intr                                                                                                                                             | Introduction1                                                                                                                                                                                                                                                  |                               |  |  |  |

|                                             | $     \begin{array}{r}       1.1 \\       1.2 \\       1.3 \\       1.4 \\       1.5 \\       1.6 \\       1.7 \\       1.8 \\     \end{array} $ | The Solar Orbiter mission<br>The PHI instrument<br>SO/PHI Measurement principles<br>The SO/PHI data processing pipeline<br>The Data Processing Unit in SO/PHI<br>The PHI Team<br>Objectives of this thesis<br>Methodology and thesis structure                 | 5<br>8<br>9<br>12<br>16<br>17 |  |  |  |

| 2 The Radiative Transfer Equation inversion |                                                                                                                                                  |                                                                                                                                                                                                                                                                |                               |  |  |  |

|                                             | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                                                                                                    | The RTE inversion in SO/PHI.<br>The RTE inversion algorithm<br>Computational cost of the RTE inversion code<br>Reliability and robustness of C-MILOS<br>Precision of the calculations in C-MILOS<br>Improving the RTE inversion code<br>C-MILOS inversion time | 27<br>29<br>32<br>34<br>35    |  |  |  |

| 3                                           | High performance scientific computing on FPGA                                                                                                    |                                                                                                                                                                                                                                                                | 39                            |  |  |  |

|                                             | 3.1<br>3.2<br>3.3<br>3.4                                                                                                                         | Introduction<br>Custom architectures on FPGA<br>Parallel computing using multi-processor architectures<br>Multi-processors architecture in FPGAs                                                                                                               | 40<br>42                      |  |  |  |

| 4                                           | A MIMD architecture                                                                                                                              |                                                                                                                                                                                                                                                                | 47                            |  |  |  |

|                                             | 4.1<br>4.2<br>4.3<br>4.4                                                                                                                         | The multicore MIMD architecture<br>A novel MIMD programming model<br>The RTE algorithm in the MIMD architecture<br>MIMD architecture in FPGA                                                                                                                   | 50<br>53                      |  |  |  |

| 5                                           | AS                                                                                                                                               | SIMD architecture                                                                                                                                                                                                                                              | 57                            |  |  |  |

|                                             | 5.1<br>5.2<br>5.3<br>5.4                                                                                                                         | The SIMD architecture<br>The SIMD architecture on the FPGA<br>The RTE inversion algorithm within the SIMD architecture<br>A reconfigurable and scalable SIMD architecture                                                                                      | 67<br>69                      |  |  |  |

| 6                                           | The                                                                                                                                              | e TAPAS tool                                                                                                                                                                                                                                                   | 75                            |  |  |  |

|                                             | 6.1<br>6.2                                                                                                                                       | MIMD TAPAS<br>The SIMD TAPAS                                                                                                                                                                                                                                   |                               |  |  |  |

| 7                                                        | Th                                                         | The Singular Value Decomposition within the RTE inverter                                                                                                                        |     |  |  |  |

|----------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

|                                                          | 7.1<br>7.2<br>7.3<br>7.4<br>7.5                            | Introduction to the SVD<br>The Jacobi iterative method<br>The Brent's algorithm<br>The SVD architecture design<br>Results                                                       |     |  |  |  |

| 8                                                        |                                                            |                                                                                                                                                                                 |     |  |  |  |

|                                                          | 8.1<br>8.2                                                 | Fault mitigation, detection, and correction on the FPGA<br>Integration of the RTE inverter in the DPU                                                                           |     |  |  |  |

| 9                                                        | 9 Results                                                  |                                                                                                                                                                                 |     |  |  |  |

|                                                          | 9.1<br>9.2<br>9.3<br>9.4                                   | The RTE inverter within the SO/PHI development status<br>Time requirements and computing performance<br>Power consumption requirements<br>RTE inversion scientific requirements |     |  |  |  |

| 10                                                       | Co                                                         | onclusions and future prospects                                                                                                                                                 |     |  |  |  |

| 11                                                       | Aŗ                                                         | ppendix I. The Voigt function                                                                                                                                                   |     |  |  |  |

| 12 Appendix II. HLS description of a RTE inversion block |                                                            |                                                                                                                                                                                 |     |  |  |  |

| 13 Appendix III. MIMD architecture notes 1               |                                                            |                                                                                                                                                                                 |     |  |  |  |

| 14 Appendix IV. SIMD architecture notes                  |                                                            |                                                                                                                                                                                 |     |  |  |  |

| 15                                                       | 15 Appendix V. Communications based on RS-232 schematic 17 |                                                                                                                                                                                 |     |  |  |  |

| 16                                                       | Appendix VI. SVD notes                                     |                                                                                                                                                                                 |     |  |  |  |

| 17                                                       | Aţ                                                         | Appendix VII. Communication notes                                                                                                                                               |     |  |  |  |

| 18                                                       | Aţ                                                         | Appendix VIII. Documentation packets                                                                                                                                            |     |  |  |  |

| 19                                                       | Aŗ                                                         | Appendix IX. Virtex-4 FPGA development board                                                                                                                                    |     |  |  |  |

| 20                                                       | Aţ                                                         | ppendix X. Publications and other merits                                                                                                                                        |     |  |  |  |

| 21                                                       | Ac                                                         | cronyms                                                                                                                                                                         | 193 |  |  |  |

| 22                                                       | Re                                                         | ferences                                                                                                                                                                        |     |  |  |  |

## 1

## Introduction

From the early days of humankind, the Sun has unquestionably been the main celestial body, and the one that breathes life into the Earth. Soon, the Sun was ascended to a god category. Inti, in the Inca Empire, Ra, for Egyptians, and Helios, in the Greek culture, were deifications of the Sun.

The first astronomic attempt to explain how the universe works located the Earth as its center. Several centuries after that paradigm, Nicolaus Copernicus shifted the center of the known universe to the Sun. Back then, the Sun was not a god any more. The road had been opened for a scientific thought that was able of mathematically explaining the universe. Newton, after Galileo and Kepler, laid the foundations of modern science with its formal models and methodology. Four centuries later, the same thirst for knowledge has carried us to space exploration for searching the principles that manage the universe.

This PhD dissertation is an example of how the everlasting dichotomy between science and technology is old fashioned. It is a technological step forward with the background goal of helping science to increase our basic knowledge. The main goal of this dissertation is obtaining more efficient and powerful computing models to fulfil the stringent requirements of a solar physics problem. Hence, it can be considered advancement in the computer science field (thus improving computing technology) that can be used as a tool for astrophysics. As a by-product, many of the developments described in this dissertation can be used in other applications where high-performance scientific computing is needed.

#### 1.1 **The Solar Orbiter mission**

The Earth is within the extended atmosphere of the Sun, called Heliosphere. Advances in our understanding of both the Sun and the Heliosphere are therefore expected to improve not only our knowledge but our life on Earth as well. This is the goal of *Solar Orbiter*, an ESA mission in collaboration with NASA that was selected as the first medium (M)-class mission of ESA's Cosmic Vision 2015 – 2025 program.

An outline about the scientific objectives of Solar Orbiter is adopted from [Müller (2013)]:

"The results from current and past solar and heliospheric missions such as Helios [Porsche (1977); Schwenn (1990); Schwenn (1991)], Voyager [Stone (1977)], Ulysses [Wenzel (1992)], Yohkoh [Acton (1992)], SOHO [Domingo (1995)], TRACE [Handy (1999)], RHESSI [Lin (2002)], Hinode [Kosugi (2007)], STEREO [Kaiser (2008)] and SDO [Pesnell (2012)] have greatly improved our knowledge of the solar corona, the solar wind, and the three-dimensional Heliosphere. Each of these missions had a specific focus, being part of an overall strategy of coordinated solar and heliospheric research. However, none of these missions have been able to fully explore the interface region where the solar wind is born and heliospheric structures are formed with sufficient instrumentation to link solar wind structures back to their source regions at the Sun.

With a combination of in-situ and remote-sensing instruments and its inner-heliospheric mission design, Solar Orbiter will address the central question of heliophysics: How does the Sun create and control the Heliosphere? This primary, overarching scientific objective can be expanded into four interrelated top-level scientific questions that will be addressed by Solar Orbiter:

- What drives the solar wind and where does the coronal magnetic field originate from?

- How do solar transients drive heliospheric variability?

- How do solar eruptions produce energetic particle radiation that fills the Heliosphere?

• How does the solar dynamo work and drive connections between the Sun and the Heliosphere?

These questions represent fundamental challenges in solar and heliospheric physics today. By addressing them, we expect to make major breakthroughs in our understanding of how the inner solar system works and is driven by solar activity. To answer these questions, it is essential to make in-situ measurements of the solar wind plasma, fields, waves, and energetic particles close enough to the Sun that they are still relatively pristine and have not had their properties modified by subsequent transport and propagation processes. This is one of the

## fundamental drivers for the Solar Orbiter mission, which will approach the Sun to as close as 0.28 Astronomical Unit (AU)"

It is important to remark that *Solar Orbiter* will also have the possibility of observing the solar poles. An orbital inclination of  $25^{\circ}$  will be reached during the nominal mission, and a maximum inclination about the ecliptic of  $34^{\circ} - 36^{\circ}$  in the extended mission.

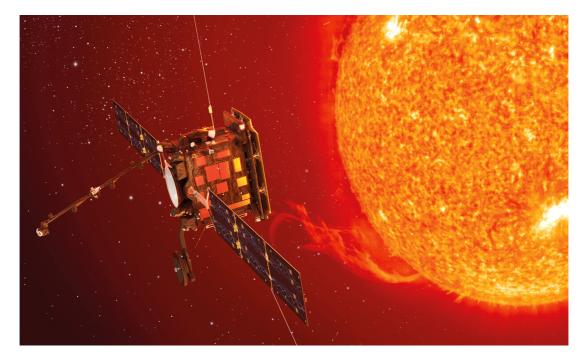

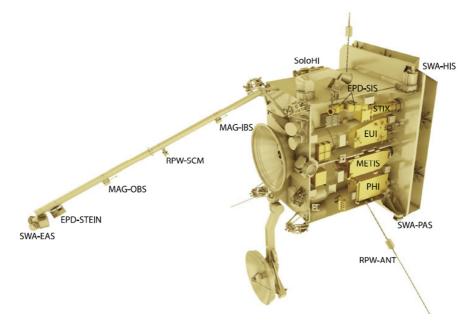

The scientific payload of the Solar Orbiter mission is formed by ten instruments. In Figure 1 the instrument accommodation onboard Solar Orbiter is shown. In short, there are in-situ instrument for measuring the solar wind, energetic particles and magnetometers. Also there are remote-sensing instruments that basically are imagers for providing visual images, and for doing spectroscopy with different aims as study solar wind or X-ray emissions. One of them is the Polarimetric and Helioseismic Imager instrument (PHI).

Also in [Müller (2013)] are introduced the instruments that compose the scientific payload of Solar Orbiter. We adopted this introduction below.

"Relating these in-situ measurements back to their source regions and structures on the Sun requires simultaneous, high-resolution imaging and spectroscopic observations of the Sun in and out of the ecliptic plane. The resulting combination of in-situ and remote-sensing instruments on the same spacecraft, together with the new, inner-heliospheric perspective, distinguishes Solar Orbiter from all previous and current missions, enabling science which can be achieved in no other way.

The scientific payload elements of Solar Orbiter will be provided by ESA member states, NASA and ESA and have been selected and funded through a competitive selection process. These are:

The in-situ instruments:

• The Energetic Particle Detector (EPD) experiment (J. Rodriguez-Pacheco, PI, Spain; R. F. Wimmer-Schweingruber, co-PI, Germany) will measure the properties of suprathermal ions and energetic particles in the energy range of a few keVn-1 to relativistic electrons and high-energy ions (100 MeVn-1 protons, 200 MeVn-1 heavy ions).

• The Magnetometer (MAG) experiment (T.S. Horbury, PI, UK) will provide detailed insitu measurements of the heliospheric magnetic field.

• The Radio and Plasma Waves (RPW) experiment (M. Maksimovic, PI, France) will measure magnetic and electric fields at high time resolution and determine the characteristics of electromagnetic and electrostatic waves in the solar wind from almost DC to 20 MHz.

• The Solar Wind Analyser (SWA) instrument suite (C.J. Owen, PI, UK) will fully characterize the major constituents of the solar wind plasma (protons, alpha particles, electrons, heavy ions) between 0.28 and 1.2 AU.

The remote-sensing instruments:

• The Extreme Ultraviolet Imager (EUI, P. Rochus, PI, Belgium) will provide image sequences of the solar atmospheric layers from the photosphere into the corona.

• The Multi Element Telescope for Imaging and Spectroscopy (METIS) Coronagraph (E. Antonucci, PI, Italy) will perform broad-band and polarized imaging of the visible K-corona, narrow-band imaging of the UV and EUV corona and spectroscopy of the most intense lines of the outer corona.

• The Polarimetric and Helioseismic Imager (PHI, S.K. Solanki, PI, Germany; J.C. del Toro Iniesta, co-PI, Spain) will provide high-resolution and full-disk measurements of the photospheric vector magnetic field and line-of-sight velocity as well as the continuum intensity in the visible wavelength range.

• The Solar Orbiter Heliospheric Imager (SoloHI, R.A. Howard, PI, USA) will image both the quasi-steady flow and transient disturbances in the solar wind over a wide field-of-view by observing visible sunlight scattered by solar wind electrons.

• A European-lead extreme ultraviolet imaging spectrograph Spectral Imaging of the Coronal Environment (SPICE) with contributions from ESA member states and ESA. This instrument will remotely characterize plasma properties of regions at and near the Sun.

• The Spectrometer/Telescope for Imaging X-rays (STIX) (S. Krucker, PI, Switzerland) provides imaging spectroscopy of solar thermal and non-thermal X-ray emission from  $\sim 4 - 150$  keV".

Detailed descriptions of the payload elements, as well as traceability matrices of the science goals are given in [Marsden (2011)]."

Figure 1 Payload accommodation onboard Solar Orbiter. (Adapted from [Müller (2013)])

#### 1.2 **The PHI instrument**

The Polarimetric and Helioseismic Imager (SO/PHI or simply PHI) instrument will provide high-resolution and full-disk measurements of the photospheric vector magnetic field and line-of-sight (LOS) velocity as well as the continuum intensity in the visible wavelength range. The measurement principle of SO/PHI is based on imaging spectropolarimetric observations of a photospheric absorption line in the solar visible-light spectrum. More details can be found in [Solanki (2015)].

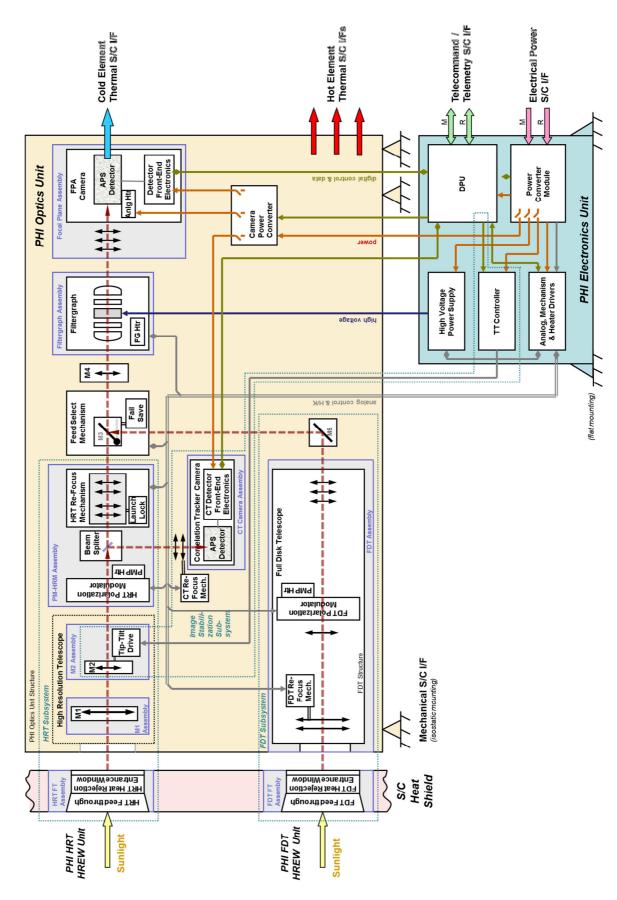

The instrument is made up of two main units, namely, an Optics Unit and an Electronics Unit (E-Unit). Figure 2 illustrates the conceptual design.

The Optics Unit contains several subsystems: two telescopes, a tunable filtergraph, two polarimetric packages, an image stabilization system, and the focal plane assembly. The, so-called High Resolution Telescope (HRT) is an off-axis Ritchey-Chrétien that will image a fraction of the solar disk at a resolution of 150 km over the solar surface at perihelion (the same resolution as the Extreme Ultraviolet Imager's high resolution channel). The refractor, Full Disk Telescope (FDT), will be able to image the full solar disk at all phases of the orbit. Each telescope has its own Polarization Modulation Package (PMP) located early in the optical path in order to minimize crosstalk effects among the four Stokes parameters. Polarimetry with a signal-to-noise ratio of 10<sup>3</sup> is baselined for SO/PHI. HRT or FDT will sequentially send light to a Fabry-Perot filtergraph system (100mÅ spectral resolution) and on one 2048×2048 pixels CMOS sensor. The Image Stabilization System (ISS) will compensate spacecraft jitter or other disturbances. This system is composed of a correlation tracker and a rapid tip-tilt mirror for the HRT [Hirzberger (2012)]]. Although the Heat Rejecting Entrance Window (HREW) is not visible in Figure 1, it contains the two openings for both telescopes that Figure 2 shows.

Figure 2 PHI Functional Diagram. (Adapted from [Meller (2013)])

The E-Unit is the main electronics system and is in charge of controlling the whole instrument. It is based on a modular system with individual boards (subsystems) interconnected with an external motherboard called EDS (Electrical Distribution System). It consists of five subsystems: the DPU (Digital Processing Unit for image accumulation, preprocessing, Stokes inversion of physical magnitudes, data compression, control of the instrument and of the interfaces with the spacecraft; the PCM (main and redundant Power Converter Module for providing the corresponding power supply to the subsystems); the AMHD (for housekeeping parameter acquisition, motors controller, and heater drivers) board; the TTC (Tip-Tilt Controller); and the HVPS (High Voltage Power supply for the filtergraph).

SO/PHI will observe intensively during the Science Operations Windows of each orbit. During other phases of the orbit it will continue to provide, as necessary, synoptic and context observations of the magnetic field at a considerably lower cadence. It will also provide helioseismic data at the full cadence but at a vastly reduced spatial resolution [Hirzberger (2012)]]. Specific operational modes have been defined to meet the scientific objectives during all mission phases within the allocated telemetry resources.

Severe threats have to be dealt in the SO/PHI instrument as a good power management or heat dissipation, all of them, with a mass limitation of 31 Kg for the entire instrument. The total power consumption limitation for the instrument is around 45 W during the science operation in the nominal orbit (0.28 AU). There is a great radial temperature in the nominal orbit that supposes a great challenge for the thermal engineers. This issue could affect the optical performance and the entire instrument.

A big technical challenge is the data transmission of the scientific data to ground since the available telemetry for SO/PHI is in average 20kbps, or 211 MB/day. To reduce the telemetry needed by SO/PHI, an initial reduction and the scientific analysis of the data will be carried out already onboard the spacecraft using a Milne-Eddington inversion (or RTE inversion) of the recorded data prior to their transmission to ground [Hirzberger (2012)]]. This analysis is highly computing demanding: in fact, when this type of observations is analyzed post facto on Earth, typical PCs spend almost two and a half hours [Borrero (2010)].

That is precisely one of the features that stand out among all the instrumentation in the *Solar Orbiter* mission, and maybe among all the space instruments of all times. Such an exhaustive scientific analysis has never been carried out aboard any space instrument.

Specifically, the challenge of carrying out this scientific analysis on flight is the origin and motivation of this thesis.

#### 1.3 SO/PHI Measurement principles

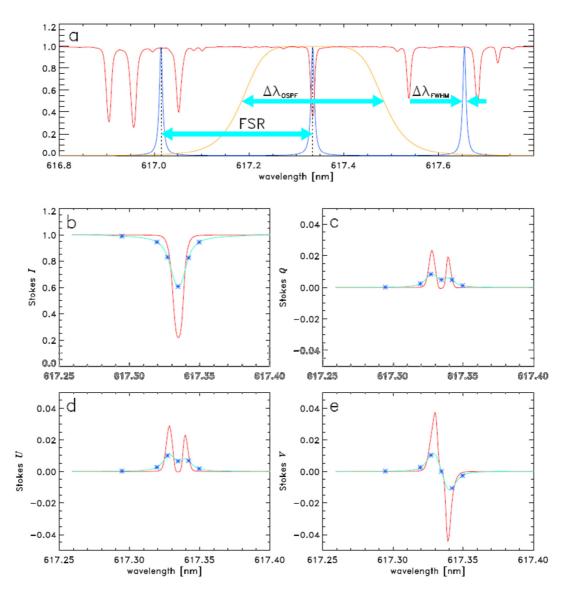

The primary goal of SO/PHI is to map the vector magnetic field of the Sun (magnetography) and the velocity of the solar plasma along the line of sight (tachography). Therefore, both polarimetric and spectroscopic measurements are needed. Magnetography is made through using liquid crystal variable retarders (LCVRs) as polarization modulators and a linear polarizer as the analyzer. With them, all four Stokes parameters of light, namely, *I*, *Q*, *U*, and *V* are measured. Stokes *I* gives the intensity of the light beam; Stokes *Q* and *U* give the linear polarization; and Stokes *V* speaks about the circular polarization. Spectroscopy is made by scanning a solar photospheric absorption line at a few wavelengths with a tunable, narrow band Filtergraph (FG), which is made up of a broader band pre-filter and a narrow band LiNbO<sub>3</sub>, solid Fabry-Perot etalon. With SO/PHI, thus, the spectral line profile at each point over the solar surface and in all four Stokes parameters is obtained: the so-called Stokes profiles of the spectral line are sampled at several wavelengths. The sought-for solar information is encoded in these Stokes profile samples.

The Fe I line at 617.3 nm was chosen as the SO/PHI science target after a careful comparison with a number of other widely used Zeeman-sensitive lines due to its ideal combination of properties allowing both vector magnetic field and helioseismic observations [Hirzberger (2012)]. The polarization properties of this spectral line depend on the magnetic field structure in the line-forming regions of the solar atmosphere through the Zeeman effect. In addition, the exact wavelength position of the spectral line depends on the relative velocity between the observing solar point and the spacecraft through the Doppler effect.

Figure 3 illustrates the measurement principle. The intensity solar spectrum around 617 nm is shown in panel *a* (red solid line) along with the pre-filter (orange solid line) and the etalon transmission profiles (blue solid line). The vertical dotted lines mark the central wavelength position of the various transmission peaks of the etalon. Their full width at half maximum (FWHM) is denoted by  $\Delta\lambda_{FWHM}$ , their separation is the so-called free spectral range (FSR), and the FWHM of the pre-filter is  $\Delta\lambda_{OSPF}$ . The FG spectral transmission is given by the product of the pre-filter and etalon transmission profiles, so that the side peaks of the FG are almost suppressed to zero. Panels *b* through *e* display the four Stokes profiles of the Fe I line as resulting from a simulation. The original profiles are plotted in red, the same profiles after convolution with the FG transmission profile are plotted in light blue; the asterisks mark the instrument wavelength samples.

As commented above, the information about the solar magnetic field and plasma velocity is encoded in the spectrum of these Stokes profiles. The SO/PHI data products, then, will be extracted from the primary observables by onboard processing. Without going into details, we can say that the process of getting the solar atmospheric parameters from the Stokes parameters is known as the inversion of the Radiative Transfer Equation (RTE) [del Toro (2003)]. This process will be detailed in Chapter 2.

Figure 3 Measurement principle of SO/PHI. (Image adapted from [Hirzberger (2015)]).

### 1.4 The SO/PHI data processing pipeline

The conceptual light path is depicted in Figure 2 with brown dotted lines. The light is recorded by the CMOS sensor after a polarization analysis by the polarization modulation package and a selection of wavelength within the spectral line by the filtergraph. Raw data, as they will be produced by the SO/PHI science detector within the focal plane assembly (FPA), are built up of narrow band filtergrams (images) obtained in the spectral region around the Fe I absorption line at 617.3 nm (the light level will be modulated by the PMPs).

Several operation principles can be tuned for acquisition of data. The science observing modes define the telescope to use (HRT or FDT), the number (and wavelengths) of the spectral scan positions (6 as a baseline) the number of polarization states at each spectral position (4 baselined for I, Q, U, and V), and the number of images to be accumulated at each polarization state and spectral position.

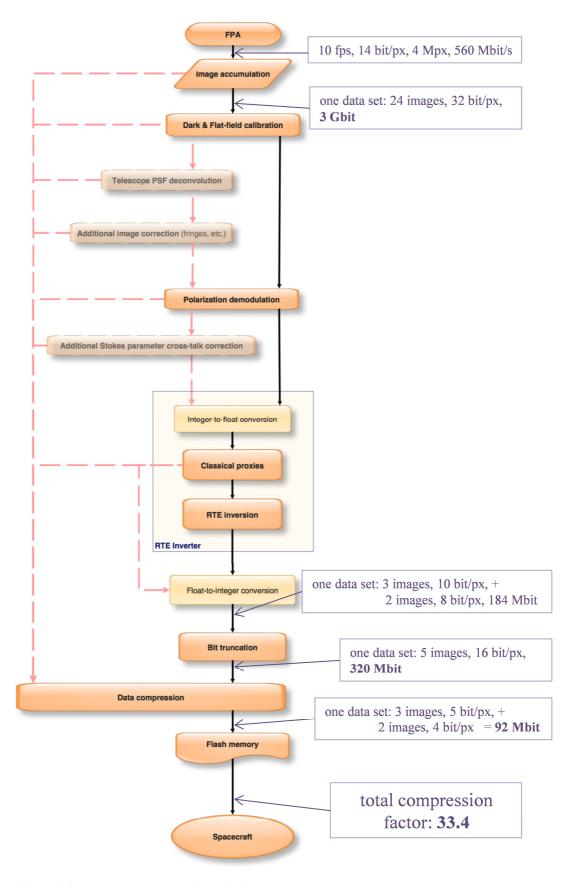

A conceptual overview of the data pipeline is shown in Figure 4 with a block diagram. Solid black lines denote the baseline data processing pipeline; dashed red lines represent additional/alternative processing modules, and denote the possibility to store and downlink raw and partially processed data. We refer the interested reader to [Hirzberger (2012)] for details.

In order to achieve a signal-to-noise ratio (SNR) of  $10^3$ , several images (separately for each polarization sate) have to be accumulated. An exposure time of the order of 1 s per polarization state is required to obtain the required SNR. This means that around 22 images have to be accumulated. The size of the frames is 2048x2048 pixels. However, the number of rows can be specified in the science operation mode (0–2047). At every spectral position and polarimetric state a number of frames will be accumulated in real time. Single frames have a digital depth of 14 bits and accumulated images have 32 bits digital depth. A frame rate of  $10 \text{ s}^{-1}$  corresponds to a read-out rate of 560 Mbits/s.

For each single science data set (one scan across the Fe I line at 617.3 nm), 24 accumulated images (6 spectral scan positions and 4 polarization states) are acquired, accounting for a raw data size of 3.2Gbit (for a frame size of  $2048 \times 2048$  pixels).

After data accumulation, several basic data calibration procedures have to be applied, so dark current and flat field calibrations are carried out. The polarization of the incoming light is modulated and analyzed by the PMPs. This means that that the fraction of light with a certain polarization state is transformed into a given intensity level, which is a linear combination of the four Stokes parameters. The process of recovering the Stokes parameters from those combinations is known as demodulation. That polarization demodulation does not affect to the size of a raw data set: 3.2 Gbit.

Through the study of the polarization state of the specific spectral line, we can infer the magnetic field vector and other quantities that define the physical state of the solar photosphere as the continuum intensity and the velocity of the solar plasma in the light-of-sight [del Toro (2003)]. Technically speaking, the inference of the solar physical quantities from the spectropolarimetric observations is based on the RTE inversion.

Figure 4 On-board data processing pipeline.

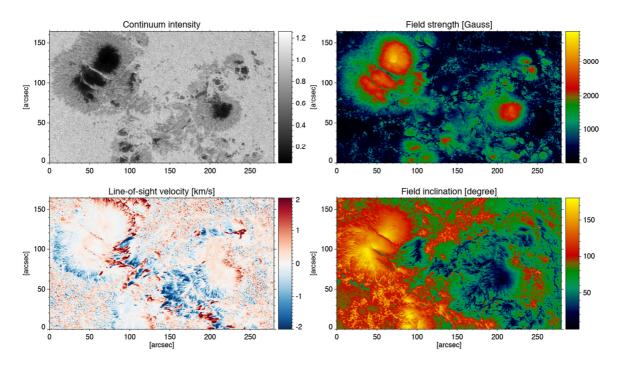

Thanks to the RTE inversion the raw data set can be reduced from 24 images to only 4 images: the line-of-sight (LOS) flow velocity and the strength, inclination, and azimuth of the magnetic field vector. The continuum intensity, which is not an output from the inversion procedure, is also a valuable fifth image. The inversion results enable the representation of the physical quantities with a shorter fixed point precision than the raw polarized images. Therefore, these quantities are candidates of a bit truncation.

The last step in the data processing pipeline is a lossless compression procedure. The RTE inversion results also help in increasing the effective data compression. As illustrated in Figure 4, data after the RTE inversion are truncated and compressed. Hence, the amount of data is reduced to only 92 Mbit per individual set. In short, we can say that the SO/PHI data processing pipeline, using **the on-board scientific analysis**, **reduces the data** to be transferred from the spacecraft to ground **in a factor higher than 33**.

During normal science operation, only fully-processed and compressed data are expected to be downlinked. During commissioning and check-out phases it is, however, planned to downlink raw and/or partly processed data, as is illustrated with dashed red lines in Figure 4.

In summary, the RTE inversion on board implies to do the scientific analysis of 24 images of 2048x2048 pixels, which makes it easy a final compression factor of around 33. In this thesis we study the RTE inversion algorithm and we will propose two computational architectures for that task not to be a bottle neck in the instrument regular pipeline.

#### 1.5 The Data Processing Unit in SO/PHI

The complexities of the acquisition tasks and of the data processing pipeline imply that steps like scientific data extraction and data evaluation have to be conducted within an instrument Data Processing Unit (DPU), which is otherwise responsible of the overall behavior of the whole instrument.

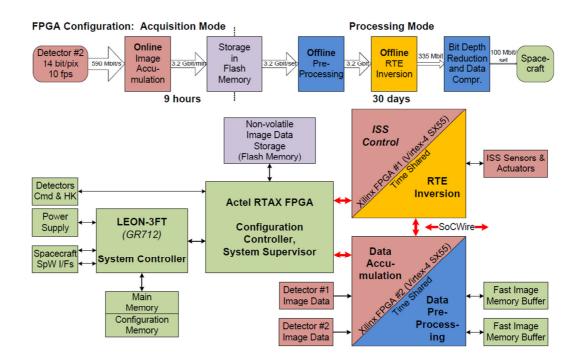

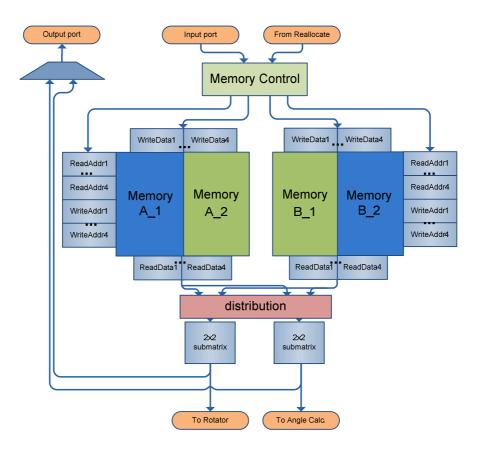

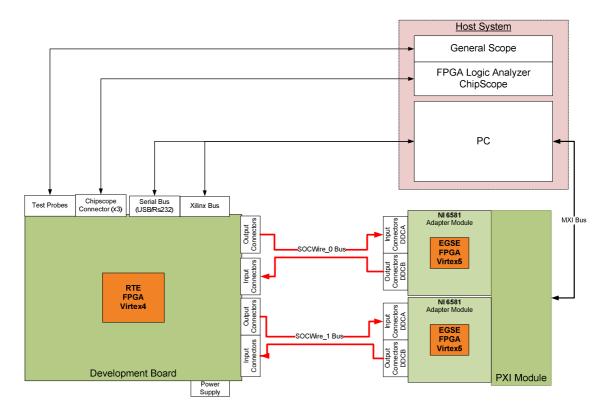

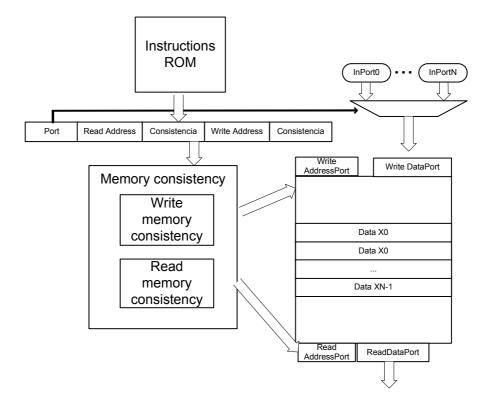

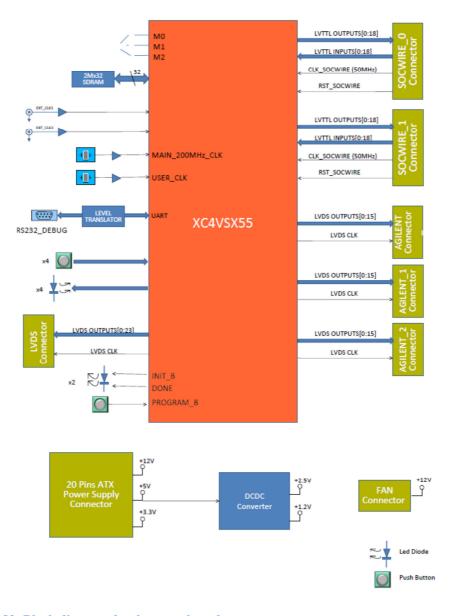

The basic structure proposed for the PHI DPU design is based on the results of the ESA study for a Dynamically Reconfigurable Processing Module (DRPM) [Bubenhagen (2010); Fossati (2011)]. This design utilizes a combination of a processor ASIC (GR712C from Aeroflex-Gaisler), containing a LEON-3FT-based main processor system, together with a fixed, radiation hardened and TMR by design, one-time programmable Microsemi RTAX FPGA as system supervisor plus a set of dedicated, real-time function cores implemented within in-flight reconfigurable Xilinx Virtex-4 FPGAs (XQR4VSX55) [Fiethe (2012)]. A DPU schematics is shown in Figure 5. Other alternatives of DPU architectures were rejected due to availability and performance because of power consumption reasons, as demonstrated in [Bubenhagen (2013)].

A combination of a small amount of volatile (e.g. 8 Gbit SDRAM) and large capacity of non-volatile (e.g. 4 Tbit NAND Flash) image memory provides significant storage capacity, which fulfills all needs of intermediate data storage at very low resources [Fiethe (2012)]. The design of the NAND-Flash-based system has complete error correction, taking into account the Flash handling. NAND-Flash-based mass storages for space have been intensively studied by Institute of Computer and Communication Engineering (IDA) in the Safe Guard Data Recorder (SGDR) study for ESA and have already been implemented for the Sentinel-2 SSMM [Cassel (2011)].

It is important to remark that the 4 Tbit non-volatile NAND flash memory allows storing data in order to schedule and postpone the data processing. In the nominal science observing mode, one full set of observables will be obtained within 60s. This time range includes frame exposure and data accumulation. The high cadence of data acquisition in most operation modes and/or the lack of DPU processing capacity for carrying out all necessary tasks in due time implies for the pipeline to have an option for storing raw or partially calibrated data in an image storage. The full data processing pipeline will thus be executed during periods where no observations are carried out. This idea of postponed processing is described in Figure 5, and detailed in [Fiethe (2012)].

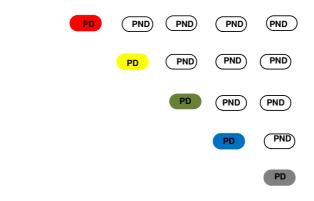

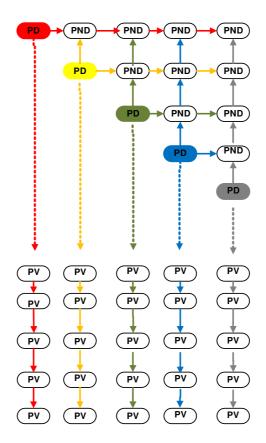

Thanks to the sufficient flash memory storage available, and to the Time-Space Partitioning (TSP) proposed by IDA [Fiethe (2012)], the entire advanced data processing pipeline is done only with the two radiation-tolerant in-flight reconfigurable Xilinx Virtex-4 FPGAs. For the PHI DPU, the seamless reconfigurability of these FPGAs enables multiple uses during different modes of operation:

- the first configuration uses the two FPGAs for image acquisition; it is remarked in Figure 5 using red blocks:

- image stabilization system (ISS) in FPGA #1

- data accumulation in FPGA #2

- a second, different configuration for the subsequent data processing is depicted in Figure 5 using yellow and blue remarks:

- RTE inversion in FPGA #1

- data pre-processing and compression in FPGA #2

Figure 5 PHI basic data flow (up) and DPU architecture block diagram with FPGA time sharing (down). Adapted from [Bubenhagen (2013)].

In short, to allow the DPU to work with only two Virtex-4 FPGAs, and make it feasible the Time-Space Partitioning within the SO/PHI instrument, the RTE inversion must be carried out using one of the two Virtex-4 FPGAs embedded in the PHI DPU. That is the same that is used to perform the Image Stabilization System (ISS) during the data acquisition phase. In the context of the SO/PHI instrument, the subsystem for carrying out the RTE inversion is also called RTE inverter and will also be referred to so along this work.

In early stages of the PHI DPU design, the use of the space-qualified Virtex-5 QRFX130T FPGA was considered. Unfortunately, this part is not yet qualified by ESA, mainly for packaging and soldering issues and, finally, the Virtex-4 XQR4VSX55 was the accepted device by ESA. Nevertheless, a specific qualification process about the assembly of the Virtex-4 XQR4VSX55 package (CF1140 package) had to be carried out by the SO/PHI team [Fiethe (2014)]. This mission-specific qualification was needed since no qualified process manufacturer for such a ceramic flip-chip column grid array package assembly is currently available in Europe.

The first DPU design, using Virtex-5, did not count with the enormous massive memory, and the first attempt was to process the raw data at the same time they were taken (online), in a minute. In the final DPU design using two Virtex-4 FPGA, thanks to the instrument internal memory, which allows storing up to one observation cycle (about 9 hours) [Hirzberger (2013-

B)], approximately 15 minutes are available to the system to perform the inversion of the RTE for each single observational data set (obtained in one minute).

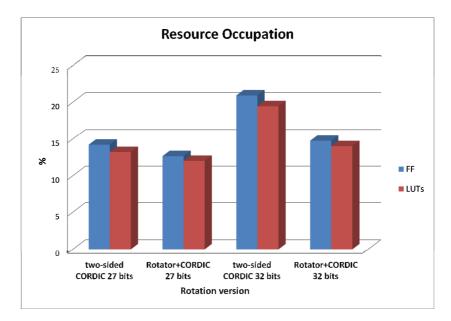

The Virtex-5 device was the baseline for the DPU design (and so for RTE inverter) during more than two years. We designed and developed a first prototype for that device. Finally, after the ESA decision, we had to redesign all the system for arranging the inversion to the Virtex-4 device. As Table 1 shows, both devices are very different, not only in number and size of available resources but also in the technology of these resources. Virtex-5 Configurable Logic Block slice contains four LUTs and four flip-flops (in Virtex 4 they have two LUTs and two flip-flops). In addition, each DSP48E slice of Virtex-5 contains 25 x 18 multipliers, meanwhile each DSP slice in Virtex-4 contains 18 x 18 ones. A study about the feasibility of using other space-qualified devices is given in [Cobos (2011)], where higher members on the qualified Virtex-4 family had to be discarded due to power consumption issues.

The Virtex-4 is based on 90 nm copper CMOS Process and it uses a 1.2 V Core Voltage. On the other hand, Virtex-5 is based on a 65 nm copper CMOS process technology, and it uses a 1.0 V core voltage. That means that Virtex-5 is a better, faster device and more efficient in power consumption. However the final system will use the Virtex-4, emphasizing even more the processing challenge in the space.

The device change in the DPU design is the reason why in this thesis two processing architectures are proposed, one for each DPU design, and both are original architectures.

|              | Devices                          |                                  |  |

|--------------|----------------------------------|----------------------------------|--|

| Resource     | Virtex 4 XQR4VSX55               | Virtex 5 XQR5VFX130              |  |

| Slices       | 24,576                           | 20,480                           |  |

| Block Ram    | 320 (18 Kb)                      | 596 (18 Kb)                      |  |

| Math Blocks  | 512<br>(400 MHz 18 bit x 18 bit) | 320<br>(360 MHz 25 bit x 18 bit) |  |

| CMOS Tech.   | 90 nm                            | 65 nm                            |  |

| Core Voltage | 1.2 V                            | 1 V                              |  |

Table 1 Elements that compose the Virtex-4 and Virtex-5 FPGAs

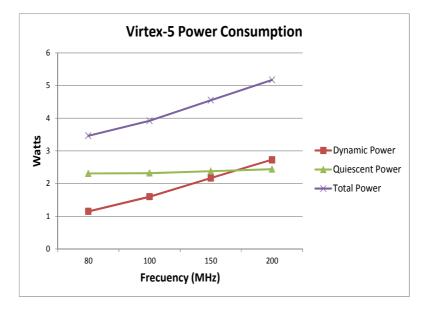

Regarding the engineering requirements, it is important to remark that the whole DPU has to operate with a maximum of 35 watts, and the assignation for the FPGA when the RTE inversion is running is only 7 watts for the Virtex-5 device and 5 watts for the Virtex-4 one.

#### 1.6 The PHI Team

To build such a complex, challenging, and novel instrument is an enormous task that would not be possible without a big consortium. However, its core elements either have space heritage or are based on technologies already developed by the SO/PHI team for the successful balloonborne *Sunrise* mission. The PHI consortium has a long-standing expertise in designing and building scientific instruments for space missions and their scientific exploitation. The PHI instrument is being developed with major contributions from institutes in Germany, Spain and France, and with smaller contributions from Sweden, and Norway.

The hardware and/or software contributing institutes are (in alphabetical order):

- Grupo de Astronomía y Ciencias del Espacio (GACE), Universidad de Valencia, Spain

- Institute of Computer and Communication Engineering (IDA), Braunschweig, Germany

- Institut d'Astrophysique Spatiale (IAS), Paris, France

- Instituto de Astrofísica de Andalucía (IAA), Granada, Spain

- Instituto de Astrofísica de Canarias (IAC), Tenerife, Spain

- Instituto Nacional de Técnica Aeroespacial (INTA), Madrid, Spain

- Instituto Universitario de Microgravedad "Ignacio Da Riva" (IDR), Universidad Politécnica de Madrid, Spain

- Institutt for Teoretisk Astrofysikk (ITA), Oslo, Norway

- Kiepenheuer-Institut für Sonnenphysik (KIS), Freiburg, Germany

- Max-Planck-Institut für Sonnensystemforschung (MPS), Göttingen, Germany

- Universidad de Barcelona (UB), Spain

The PHI consortium is represented by the Principal Investigator Prof. S. K. Solanki (MPS) and the Co- Principal Investigator Dr. Jose Carlos del Toro Iniesta (IAA).

The IAA has an important role in SO/PHI which includes the Co-Principal Investigator as well as the coordination of the Spanish consortium which is formed by the following institutions: INTA, GACE, IDR-UPM, UB and IAC. The level of participation of the Spanish consortium in the PHI instrument is slightly above 40%, including responsibilities at system level which are performed at IAA.

The IAA, as the coordinating institute, acts as a contact point with the PI project office at the MPS in Göttingen (Germany), which guarantees a high visibility of the contribution. Apart from an important contribution to the scientific side, the IAA has also a relevant contribution to the technical team. In addition to these high level tasks, the IAA is also responsible for two of the three SO/PHI instrument's Units: the Electronics Unit and the Harness as well as several important work packages at lower level as are the Electrical Distribution System (EDS), the Analog and Mechanisms Driver control board (AMHD) and the inversion of the Radiative Transfer Equation (RTE), all of them included in the E-Unit.

The EDS is an electronic board in which the distribution of the signals between the E-Unit subsystems is implemented. The AMHD is another board included in the E-Unit which is in charge of performing the PHI instrument motor and heaters control as well as the housekeeping acquisition. Finally, the RTE is the core of the on-board scientific analysis and, probably, one of the most innovative parts of the instrument. It consists on a device specifically designed to invert the Radiative Transfer Equation that will be on board *Solar Orbiter*. That denotes the importance of this thesis work within the SO/PHI instrument.

The responsibility of the IAA about the E-Unit as a whole implies the coordination of the several institutions that contribute to this unit; these are IDA (at the TU Braunschweig), which develops the Digital Processing unit (DPU); IAS (at the University of Paris-Sud), which contributes the High Voltage Power Supply (HVPS); Universitat de Barcelona (UB), which is responsible for the image stabilization system electronics (Tip Tilt Controller TTC); and GACE (at University of Valencia), which develops the Power Converter Module (PCM) of PHI.

As the E-Unit responsible, the IAA is in charge of supervising the development of all E-Unit subsystems from management and quality assurance points of view, controlling the schedule and leading the integration and verifications campaigns of the different E-Unit models.

#### **1.7 Objectives of this thesis**

In the last years, in the high-performance computing realm, the trend is to use multi-core architectures for accelerating scientific applications. However, in an extreme environment like the outer space, we cannot use the common devices like clusters of PCs or General Purpose Graphics Processing Unit devices (GPGPU) due to radiation problems and to power limitations.

The hypothesis of this thesis is to demonstrate that a space-qualified FPGA device can be used as a high-performance computing element and which will be able of carrying out the RTE inversion aboard the SO/PHI instrument. As we mentioned above, this will be the first time that such a computing demanding process is performed aboard a spacecraft. The final FPGA system can be considered the heart of the entire instrument data pipeline.

Therefore, the main aim of this thesis is to design and develop embedded architectures using the current high-performance computing techniques like multi-core architectures, code optimization, or specific-domain efficient processors, which would be able of reaching highperformance computing on an FPGA. In addition, the final design must satisfy the scientific requirement of computing precision and the engineering requirements of computing time and power consumption, all of that, without forgetting the final space environment for which the system is envisaged.

The proposed computing architectures, despite of focusing in the RTE inversion, shall be enough versatile for arranging to future changes in the scientific requirements, as spectral line, number of wavelengths, etc. That will lead to architectures with some capacity of configuration. Therefore, a secondary objective will be to provide the architectures with software tools that facilitate their configuration.

This thesis in computer science is aimed to further the research in high-performance computing and to propose innovative architectures for embedded computing. It is not an objective of this thesis to generate a detailed engineering document, or manual, with all the features and requirements of the proposed architectures focused in the space mission. For that, a great amount of technical notes and documentation has been generated within the framework of the SO/PHI international project, which will be referred to along this work. These documents are available upon request to the SO/PHI team. The requests will be examined on a case by case basis. However, we have tried to give a self-consistent document with all the necessary details, as well as, a summary of several technical notes in the appendices. Therefore, this thesis will mainly focus in explaining new computation strategies and how they are implemented using FPGA devices for carrying out scientific algorithms.

#### 1.8 Methodology and thesis structure

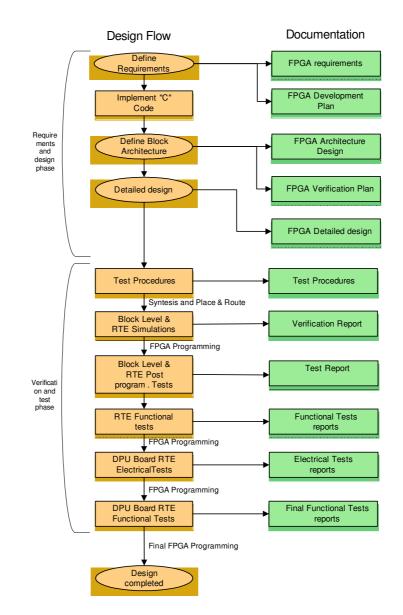

The development of this thesis is bounded to the development of the SO/PHI instrument. So the confirmation of the initial hypothesis is conditioned to the success of SO/PHI and of the RTE inverter subsystem. Since the space instrumentation context imposes a rigorous methodology based on the ESA standard for ASIC and FPGA Development [ESA (2008)] the RTE inverter development shall follow this standard.

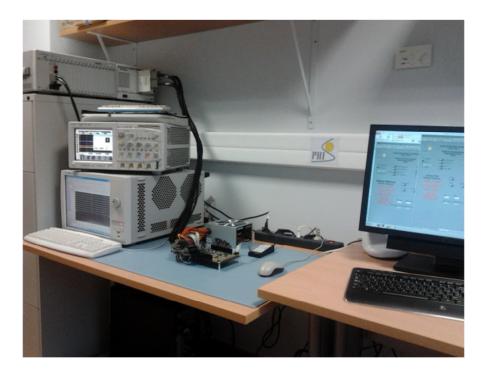

The methodology for designing and developing the RTE inverter is detailed in the RTE inverter FPGA Development Plan [Aparicio (2013)]. There, all the generated engineering documentation is detailed, and the entire followed design flow, for the RTE inverter within the space instrument context. The RTE inverter FPGA development shall follow the life cycle shown in the Figure 6, where once the specifications and requirements are established, a detailed design will be developed. This design will be simulated at a block level, and the

different blocks will also be tested on the FPGA. That is, the FPGA will be programmed with the different blocks and they will later be tested. Furthermore, this process will be repeated at top level. This is reflected in the figure as RTE simulations and RTE post programming test. Then, the RTE functional test will be done. All these tests will be carried out using the commercial FPGA version of our space-qualified Virtex-4. Finally, the electrical tests and functional test will be carried out over the flight FPGA, once integrated in the DPU board. All these steps will generate all the associated documentation appearing in Figure 6.

Figure 6 RTE inverter FPGA design flow

As Figure 6 explains, the first activity is to define the RTE requirements, including both scientific and technical. These requirements shall be documented within the RTE inverter FPGA

requirement specification [Aparicio (2014)]. This document shall include a minimum set of items according to the ESA standard [ESA (2008)], so it specifies the electrical, operational, functional, and science requirements of the RTE inverter with high grade of detail. Every requirement shall have its corresponding verification procedure and test reports. The main requirements for understanding the work in this thesis are outlined in Table 2.

| IDENTIFIER | Requirement Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RTE-R-0010 | <ul> <li>RTE shall produce maps of : <ul> <li>i the photospheric line-of-sight (LOS) flow velocity (v<sub>LOS</sub>), obtained from the polarized profiles of that line,</li> <li>ii the photospheric magnetic field strength (B<sub>LOS</sub>), obtained from the polarized profiles of the line,</li> <li>iii the photospheric magnetic field inclination (γ) with respect to the LOS, obtained from the polarized profiles of the line, and,</li> <li>iv the photospheric magnetic field azimuth (φ) in a plane perpendicular to the LOS, obtained from the polarized profiles of the above mentioned line.</li> </ul> </li> </ul> |  |  |

| RTE-R-0020 | The RTE inverter FPGA maximum power dissipation shall be 7 W for the Virtex-5 and 5 W for the Virtex-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RTE-R-0030 | The RTE inverter shall process a full set of images of each observation<br>in 1 minute using the Virtex-5 device and less than 15 minutes using<br>the Virtex-4 device                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

Table 2 Outline of the main RTE inverter requirement specifications

After this phase, a C code shall be implemented with the RTE operations. This way is easier and faster to make a first approach of RTE functionality. Then the block architecture shall be defined. This phase will be documented with the FPGA architecture design, and shall have a verification plan associated, explaining the procedures and test to verify the requirements. In [Cobos (2013)] is presented the RTE inverter FPGA validation and verification plan to follow in the RTE inverter development. It explains the needs for demonstrating whether the functional and non-functional requirements stated in the definition phase documentation are accomplished at all levels of modeling, starting from the behavioral level down to the RTL level.

It is important to remark that the Project Manager and the Assistant Manager supervise the validation and implementation tasks according to ESA standards for FPGA/ASIC developments, under the leadership and scientific assessment of the SO/PHI co-PI. Finally, an external company, SENER, with a long tradition in space missions, supervises and certificates all the development process and the documentation.

Thus, beginning from the state of the art in the field of high-performance computing embedded on FPGA, innovative architecture proposals will be generated that tackle the RTE inversion on FPGA. These architectures will be compared with the current ones. The final validation of the architecture proposals will be mainly based on the execution of the RTE inversion algorithm and on the requirements verification. If that validation is satisfactory the initial hypothesis will be corroborated. Anyway, the SO/PHI documentation will be constantly referred to as the powerful complement that it represents.

This document is structured in 9 main chapters. The next one deeply studies the RTE inversion algorithm from a point of view of computation, although some scientific concepts have to be introduced in order to clarify the most important issues. This study is necessary in order to know all the parallelization and optimization possibilities that the code intrinsically possesses. In addition, we will show the necessity of developing a core for the Singular Value Decomposition of a correlation matrix.

The third chapter presents the most relevant trends and works in the high-performance computing on the FPGA field. Based on it, two architectures, conceptually different, are proposed, but both aimed to the RTE inversion problem, and focused in obtaining high-performance computing. Each architecture is devised to one specific family of FPGAs considered in the DPU design. The fourth chapter details the design for the Virtex-5 FPGA, and the fifth one does the same for the Virtex-4 FPGA version. Since, the version for the Virtex-4 is the finally accepted by the ESA, the architecture is described with more detail.

In chapter number six, a software tool that allows the configuration and modification of the computing architectures is presented. This tool supplies a compiler that facilitates the programming tasks, and also the migration of the RTE inversion algorithm from a high-level programming language to the embedded architecture level. The tool counts with two different versions, one for each possible architecture and device.

The seventh chapter shows the design for the mathematical operation of Singular Value Decomposition of a correlation matrix.

In the eighth chapter some aspects related to the final RTE inverter systems like fault mitigation, algorithm scheduling, and configuration and use from an instrument point of view are explained.

Chapter nine shows how the RTE inversion algorithm is executed within the proposed architectures. Tests using artificial and real images are presented. A comparative with other RTE inversion approaches is done.

The tenth chapter concludes with comments and remarks about the most important innovations of the proposed solutions in this thesis.

## 2

## The Radiative Transfer Equation inversion

The limited telemetry rate combined with the large amount of scientific information retrieved from the SO/PHI instrument demand a sophisticated on-board data reduction and analysis. As pointed out in the introduction, the RTE inversion is the heart of that analysis. In this chapter, we describe the RTE inversion basics, the process, and its algorithmic implementation.

## 2.1 The RTE inversion in SO/PHI

Through a spectropolarimetric study of a particular spectral line formed in the photosphere we can infer the magnetic field and other quantities that define the physical state of the solar atmosphere [del Toro]. Spectropolarimetry is a spectroscopic analysis of light whose polarization state has been previously analyzed. As a result of this analysis, quasi-monochromatic images of the Stokes parameters (I, Q, U, V) are obtained at different wavelengths across the line and its nearby continuum -six wavelength in the SO/PHI case. The information about the solar magnetic field and plasma velocity is encoded in the spectrum of the Stokes parameters. Without going into details, we can say that the process of getting the solar atmospheric parameters from the Stokes parameters is known as the inversion of the Radiative Transfer Equation (RTE) [del Toro (2003)].

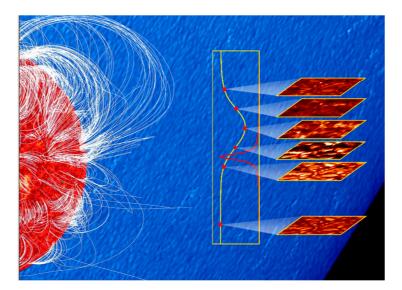

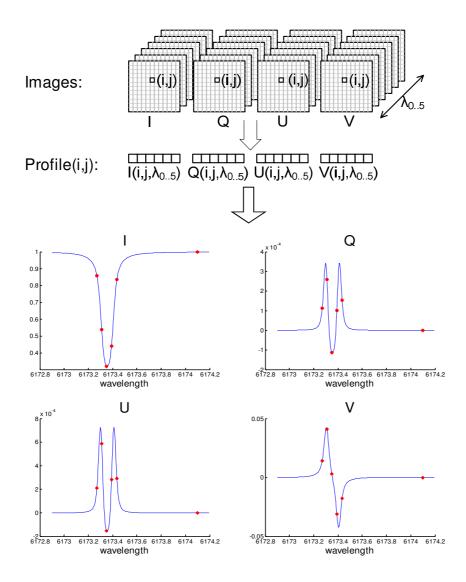

Figure 7 Illustration of the wavelength sampling

Specifically, we shall employ an inversion method based on the Milne-Eddington (ME) solution of the RTE. In it, the atmospheric parameters are assumed to be constant with depth. This approximation assumes a linear dependence of the source function on the optical depth and that several physical quantities like the magnetic field strength, the flow velocity, the microturbulence, etc. do not change with height. No macro- or microturbulent velocities will be assumed throughout this study. The ME approximation reduces significantly the computation time. However, the fit quality deteriorates for asymmetric Stokes profiles, where vertical gradients of the physical quantities are present in the solar photosphere.

In a Milne-Eddington atmosphere model, besides the so-called thermodynamic parameters (the line-to-continuum absorption coefficient ratio,  $\eta_0$ , the Doppler width of the line,  $\Delta\lambda_D$ , the damping parameter, a, and the two coefficients defining the source function,  $S_0$  and  $S_1$ ) that govern the shape of the Stokes spectrum, the line-of-sight (LOS) velocity ( $v_{LOS}$ ), and the strength (B), inclination ( $\gamma$ ), and azimuth ( $\phi$ ) of the vector magnetic field fully describe the atmosphere.

A single broadening, corresponding to the instrumental point-spread-function will be considered in the development. Since it is likely very wide (approximately  $10^{-1}$  Å), its effect on the profiles overrides other possible broadenings.

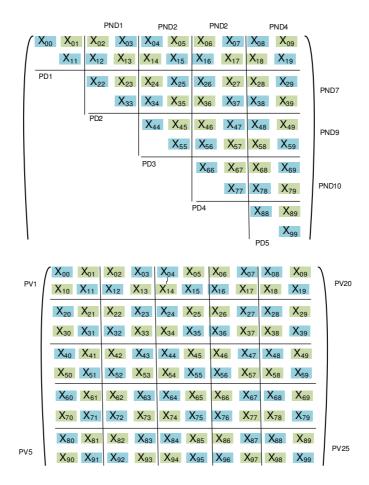

In Figure 8, a sketch is presented about how the Stokes profiles are obtained from the initial polarized images for each spatial pixel. For each point on the solar surface, codified in one spatial pixel, we have four Stokes "profiles" of six elements each (the Stokes parameters depend on wavelength). Thus, for each point (i, j) on the surface of the Sun, we have an Stokes profile with the shape of I={ $I(i, j, \lambda_{0..5}), Q(i, j, \lambda_{0..5}), U(i, j, \lambda_{0..5}), V(i, j, \lambda_{0..5})$ }. The lower panels

of Figure 8 show an example of a sampled Stokes profile Note that the sixth wavelength sample is not taken within the spectral line but on its nearby continuum. The image composed by  $I(i, j, \lambda_{0..5})$  is also called continuum intensity image, or simply I<sub>c</sub>.

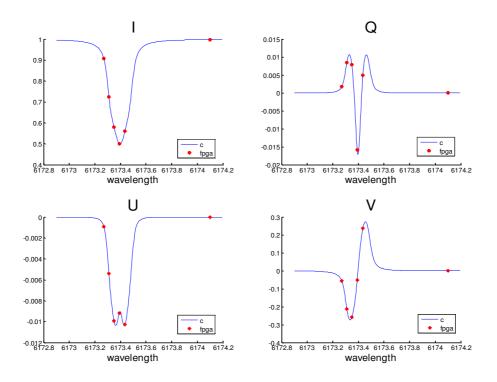

Figure 8 Diagram about how Stokes profiles are obtained from the initial images (UP). Example of a sampled Stokes profile (red dots) of the SO/PHI spectral line (blue line).

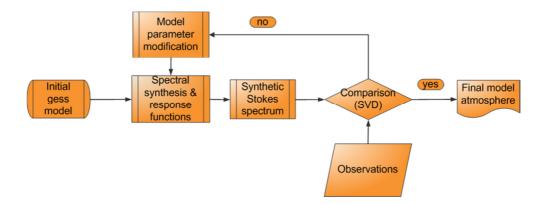

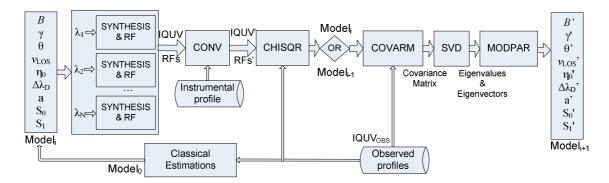

Such data set consists, then, of 24 images of 2048x2048 pixels, corresponding to the four Stokes parameters recorded at six wavelengths. From each one of these 2<sup>22</sup> sets of four Stokes profiles we will extract the relevant solar information, since each of them can be represented using a ME atmosphere model. For each Stoke profile the RTE inversion has to be carried out. Figure 9 shows a simplified RTE inversion block diagram, where the iterative character of the algorithm is apparent. Indeed, it is a non-linear least-squares procedure through which synthetic

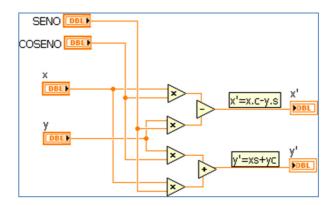

Stokes profiles are iteratively fit to the observed ones. The inversion procedure starts with an initial guess of the physical parameters. Then a synthesis of the corresponding Stokes spectrum by numerically solving the RTE is carried out. By iteratively changing the initial guess for the parameters in a closed feedback loop, the differences between synthetic and observed Stokes profiles are minimized and, thus, the desired parameters are obtained. Such a process is known as the inversion method of the Radiative Transfer Equation, or simply, RTE inversion and is illustrated in Figure 9.

Figure 9 RTE inversion process block diagram

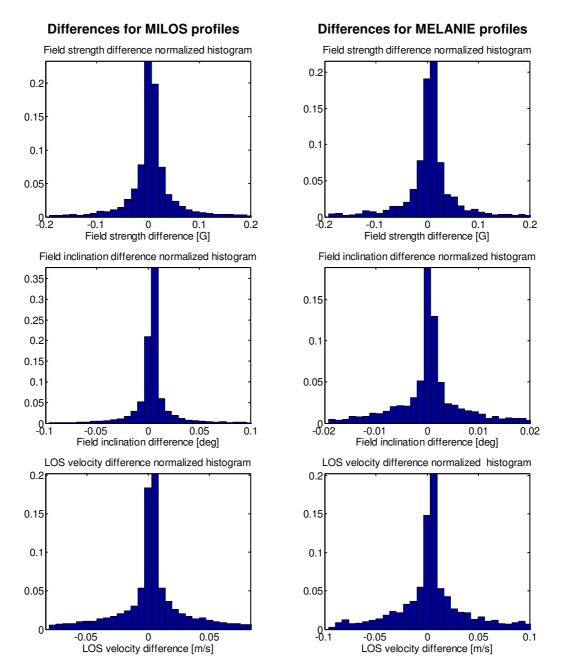

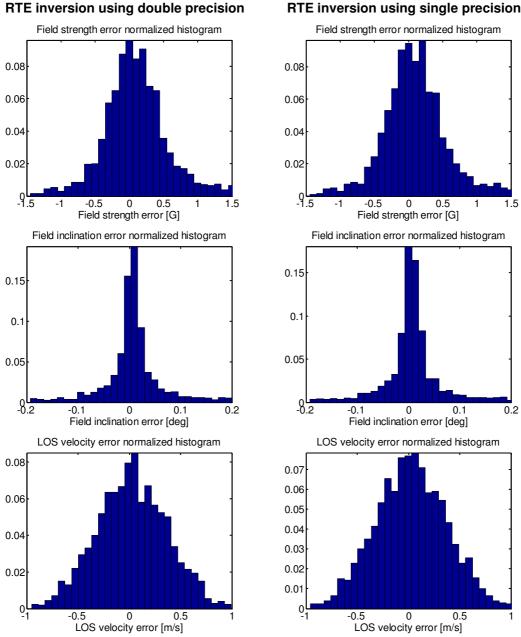

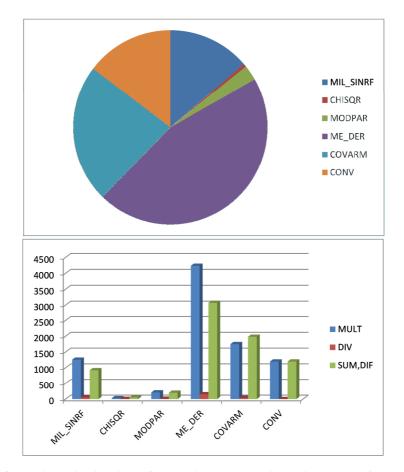

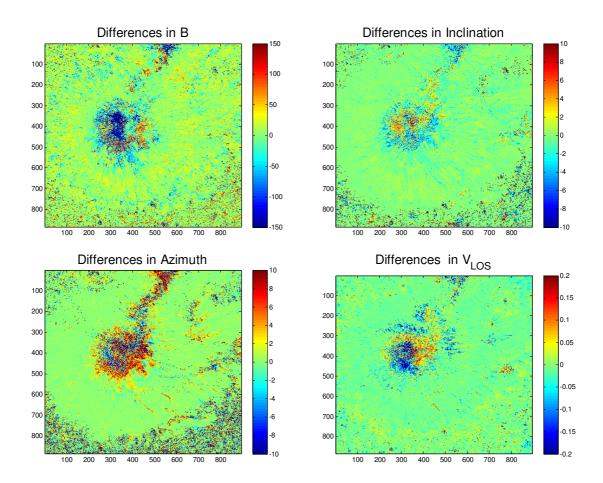

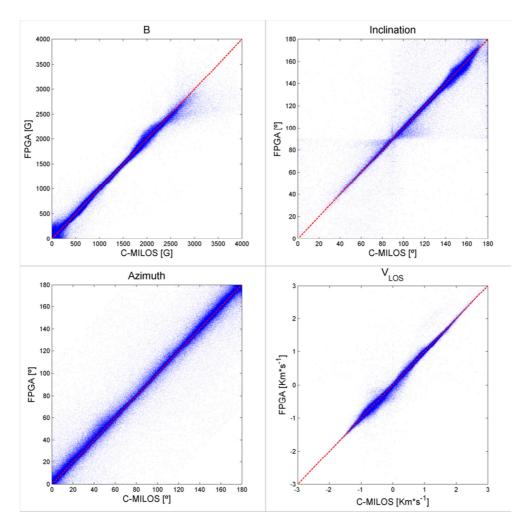

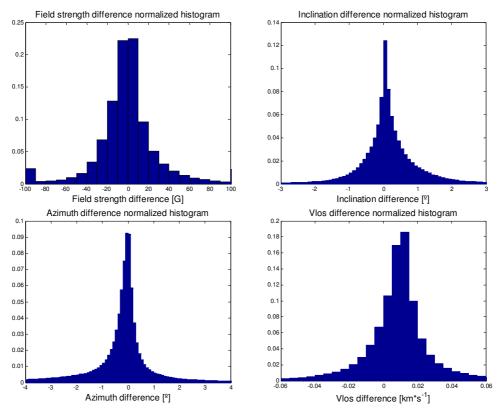

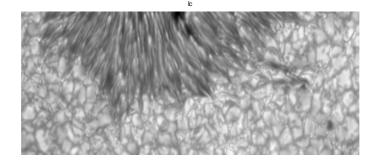

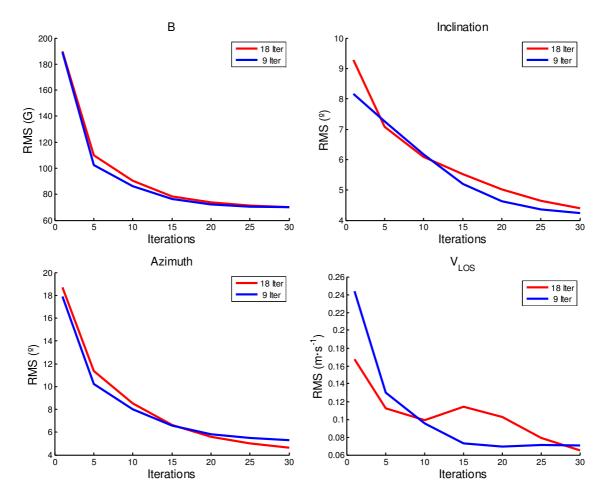

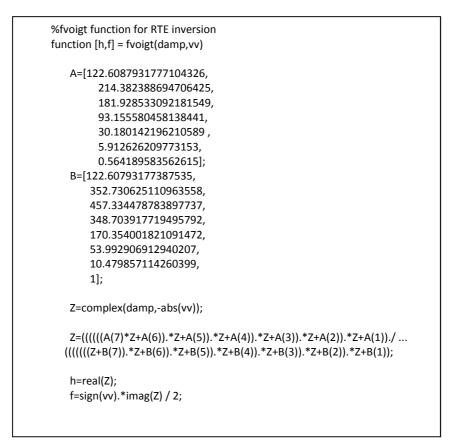

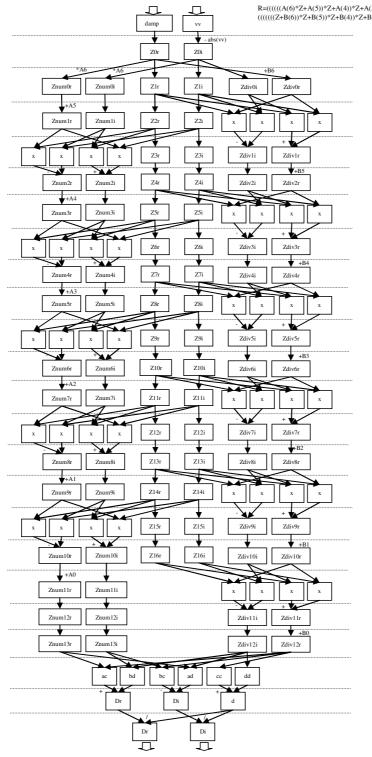

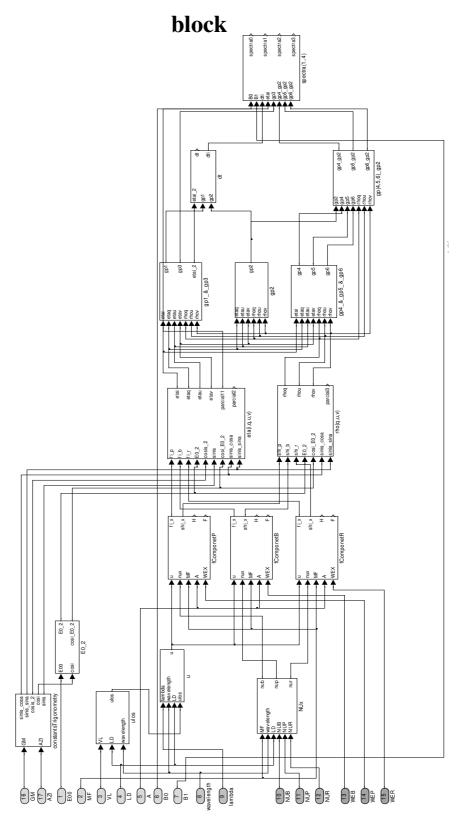

As a result of inverting the  $2^{22}$  Stokes profiles, instead of the original 24 images, only 4 will remain corresponding to  $v_{LOS}$ ,  $B_{LOS}$ ,  $\gamma$ , and  $\phi$  (as summarized in Table 2), hence reducing the amount of data by a factor almost 6. Subsequent truncation and conventional compression tasks will help to reach a final reduction factor higher than 30, as detailed section 1.3.