# UNIVERSIDAD DE GRANADA DEPARTAMENTO DE ELECTRÓNICA Y TECNOLOGÍA DE COMPUTADORES

### DESARROLLO DE NUEVAS ESTRATEGIAS DE SINCRONIZACIÓN PARA VLSI EN SISTEMAS DE PROCESAMIENTO RNS

### **TESIS DOCTORAL**

DANIEL GONZÁLEZ CASTRO

Editor: Editorial de la Universidad de Granada Autor: Daniel González Castro

D.L.: GR 755-2013 ISBN: 978-84-9028-438-4

### DESARROLLO DE NUEVAS ESTRATEGIAS DE SINCRONIZACIÓN PARA VLSI EN SISTEMAS DE PROCESAMIENTO RNS

### DANIEL GONZÁLEZ CASTRO

#### **TESIS DOCTORAL**

#### UNIVERSIDAD DE GRANADA

# DEPARTAMENTO DE ELECTRÓNICA Y TECNOLOGÍA DE COMPUTADORES

Granada, julio de 2012

D. Antonio García Ríos, Profesor Titular de Universidad, y D. Antonio Lloris Ruiz,

Catedrático de Universidad y Profesor Colaborador Extraordinario, ambos del

Departamento de Electónica y Tecnología de Computadores de la Universidad de

Granada

CERTIFICAN que el trabajo de investigación que se recoge en la presente Memoria,

titulada "Desarrollo de nuevas estrategias de sincronización para VLSI

en sistemas de procesamiento RNS" y presentada por D. Daniel

González Castro para optar al grado de Doctor por la Universidad de

Granada, ha sido realizado en su totalidad bajo su dirección en el

Departamento de Electrónica y Tecnología de Computadores de la

Universidad de Granada.

Granada a 16 de Julio de 2012

Edo. Antonio García Ríos

Fdo. Antonio Lloris Ruiz

Directores de la Tesis

#### **AGRADECIMIENTOS**

Deseo expresar mi agradecimiento en primer lugar a los profesores Dr. D. Antonio García Ríos y Dr. D. Antonio Lloris Ruiz por su dirección y asesoramiento, gracias a los cuales ha sido posible la realización de la investigación recogida en esta memoria. Asimismo quiero agradecer su amistad, su apoyo y la estrecha colaboración que hemos mantenido durante estos años.

A la profesora Dra. Dña. Encarnación Castillo Morales por su amistad, su ayuda, y los valiosos consejos que me han ayudado a finalizar esta investigación.

Al profesor Dr. D. Luis Parrilla Roure por sus consejos, su asesoramiento y sus orientaciones durante la investigación.

Al resto de los miembros del Departamento de Electrónica y Tecnología de Computadores de la Universidad de Granada por el ánimo y el apoyo recibido durante todos estos años.

Agradezco especialmente a mi esposa María del Mar, a mi hijo Juan y al resto de mi familia su constante apoyo, su paciencia y su generosa cesión de tiempo sin la cual este trabajo no hubiera sido posible.

Finalmente, destacar que este trabajo ha sido finciaciado en parte gracias a los proyectos del Plan Nacional TIC2002-02227 y TEC2007-68074-C02-01

# ÍNDICE

| Índi | ce                                                                      | i     |

|------|-------------------------------------------------------------------------|-------|

| Índi | ce de figuras                                                           | vii   |

| Índi | ce de tablas                                                            | xiii  |

| Abr  | eviaturas y siglas                                                      | xvii  |

| Pról | ogo                                                                     | xxiii |

| CAI  | PÍTULO 1: INTRODUCCIÓN                                                  | 1     |

|      | 1.1 Evolución y estado actual de las prestaciones en sistemas digitales | 2     |

|      | 1.2 Problemática en la sincronización de circuitos VLSI                 | 5     |

|      | 1.3 Estrategias de sincronización de sistemas VLSI                      | 8     |

|      | 1.4 Nueva estrategia de sincronización                                  | 10    |

|      | 1.5 Conclusión                                                          | 11    |

| CAI  | PÍTULO 2: FUNDAMENTOS DEL SISTEMA NUMÉRICO DE RESIDUOS                  | 13    |

|      | 2.1. Los Sistemas Numéricos de Residuos                                 | 14    |

|      | 2.1.1. Representación en RNS de enteros                                 | 17    |

|      | 2.1.2. El sistema numérico de residuos simétrico (SRNS)                 | 18    |

|      | 2.1.3. El sistema numérico de residuos cuadrático (QRNS)                | 18    |

|      | 2.2. Operaciones complicadas de realizar en el RNS                      | 19    |

|      | 2.2.1 Comparación de magnitud y división                                | 19    |

|      | 2.2.2 Detección de desbordamiento                                       | 20    |

|      | 2.2.3 Detección de errores                                              | 21    |

| 2.3. Técnicas de conversión para el RNS                                       | 22 |

|-------------------------------------------------------------------------------|----|

| 2.3.1. Conversión de binario a RNS                                            | 22 |

| 2.3.2. Conversión de RNS a binario                                            | 25 |

| 2.4. Módulos aritméticos para el RNS                                          | 27 |

| 2.4.1. Sumadores en aritmética de residuos                                    | 28 |

| 2.4.2. Multiplicadores en aritmética de residuos.                             | 31 |

| 2.4.2.1. Multiplicadores basados en tablas de consulta                        | 31 |

| 2.4.2.2. Multiplicadores de ley cuadrática                                    | 32 |

| 2.4.2.3. Multiplicadores basados en aritmética de índices                     | 33 |

| 2.4.2.4. Multiplicadores que no hacen uso de tablas de consulta               | 35 |

| 2.5 Conclusión                                                                | 38 |

| ÍTULO 3: SINCRONIZACIÓN EN CIRCUITOS DIGITALES VLSI         3.1. Introducción | 42 |

| 3.1.1. Sistemas síncronos                                                     |    |

| 3.1.2. Problemas que afectan a la señal de reloj                              |    |

| 3.2. Distribución de la señal de reloj                                        |    |

| 3.2.1. Dificultades en la distribución de la señal de reloj                   |    |

| 3.2.1.1. Retardo ( <i>delay</i> )                                             |    |

| 3.2.1.2. Pérdida de sincronía ( <i>skew</i> )                                 |    |

| 3.2.1.3. Dispersión en el flanco ( <i>clock jitter</i> )                      |    |

| 3.2.1.4. Electromigración                                                     |    |

| 3.2.2. Topologías de la red de distribución de la señal de reloj              |    |

| 3.2.2.1. Distribución no restringida                                          |    |

| 3.2.2.2. Distribuciones simétricas                                            |    |

| 3.2.2.3. Distribución en columna central ( <i>central spine</i> )             |    |

| 3.2.2.4. Mallas de distribución ( <i>grid</i> )                               |    |

| 3.2.2.5. Soluciones híbridas                                                  |    |

| 3.2.2.6. Otras técnicas de sincronización                                     |    |

| 3.2.2.6.1. Sincronización óptica                                              | 74 |

| 3.2.2.6.2. Sincronización mediante osciladores                                |    |

| rotatorios (rotary clocking)                                                  |    |

| 3.2.2.6.3. Supresión controlada del reloj ( <i>clock gating</i> )             |    |

| 3.2.2.6.4. Oscilación en baja amplitud ( <i>low swing</i> )                   |    |

| 3.3. Elementos de almacenamiento síncronos                                    |    |

| 3.3.1. Sincronización de CSEs controlados por nivel ( <i>latches</i> )        |    |

| 3.3.2. Sincronización de circuitos controlados por flanco                     | 92 |

<u>Índice</u> <u>iii</u>

| 3.4 Conclusión                                                                | 94  |

|-------------------------------------------------------------------------------|-----|

| CAPÍTULO 4: NUEVA ESTRATEGIA DE SINCRONIZACIÓN                                | 97  |

| 4.1. Introducción                                                             |     |

| 4.2. Metodología alternativa de sincronización de sistemas basados en RNS     |     |

| 4.2.1. Requisitospara la aplicación de la nueva estrategia de sincronización  |     |

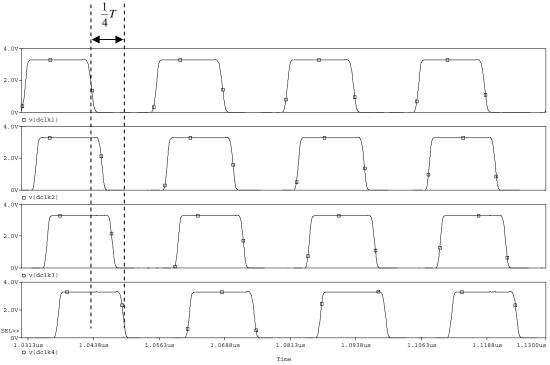

| 4.2.2. Características de las señales de reloj levemente desfasadas           |     |

| 4.2.3. Generación de las señales desfasadas:                                  |     |

| celda parametrizable dCLK_cel1                                                | 103 |

| 4.2.4. Análisis de la celda parametrizable dCLK_cell                          |     |

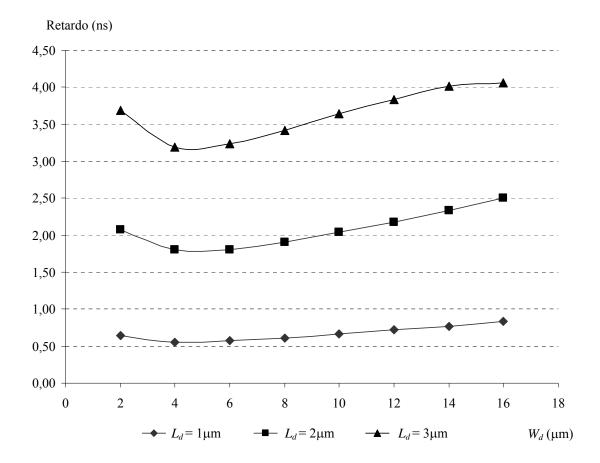

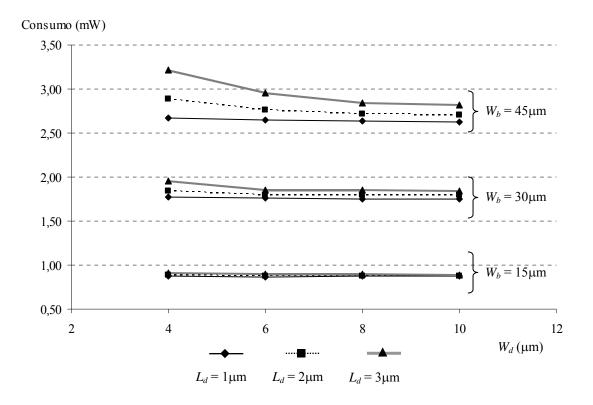

| 4.2.4.1. Efecto de $L_d$ y $W_d$                                              | 107 |

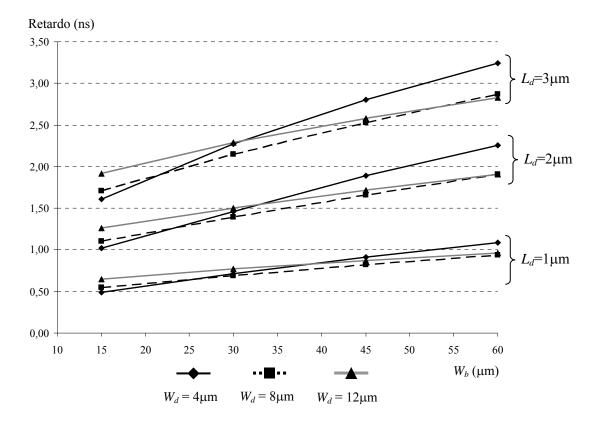

| 4.2.4.2. Efecto de $W_b$                                                      |     |

| 4.2.4.3. Análisis del consumo                                                 | 111 |

| 4.3. Diseño y aplicación de las estrategias de sincronización a tres sistemas | 112 |

| 4.3.1. Diseño de la red de distribución del reloj                             | 114 |

| 4.3.2. Filtro CIC para diezmado de Hogenauer                                  |     |

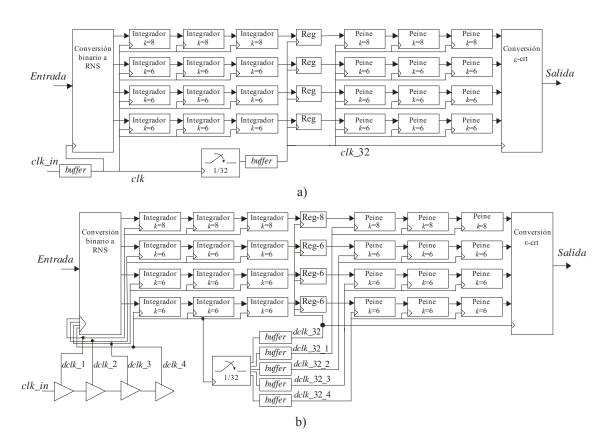

| 4.3.2.1. Descripción del sistema                                              | 123 |

| 4.3.2.2. Implementación para simulación                                       | 125 |

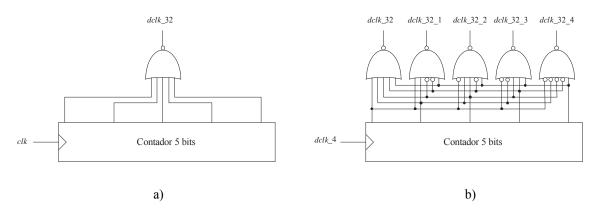

| 4.3.2.2.1. Sincronización del sistema                                         | 126 |

| 4.3.2.2.2. Conversión de binario a RNS                                        | 130 |

| 4.3.2.2.3. Integradores                                                       | 133 |

| 4.3.2.2.4. Peines                                                             | 134 |

| 4.3.2.2.5. Reductor de frecuencia                                             | 135 |

| 4.3.2.2.6. Conversión y escalado: móduo ε-CRT                                 | 135 |

| 4.3.2.3. Resultados de simulación                                             | 137 |

| 4.3.3. Controlador PID                                                        | 144 |

| 4.3.3.1. Descripción del sistema                                              | 145 |

| 4.3.3.2. Implementación para simulación                                       | 146 |

| 4.3.3.2.1. Sincronización del sistema                                         | 148 |

| 4.3.3.2.2. Conversión de binario a RNS                                        | 150 |

| 4.3.3.2.5. Canales del controlador PID                                        | 151 |

| 4.3.3.2.6. Conversión y escalado: móduo ε-CRT                                 | 151 |

| 4.3.3.3. Resultados de simulación                                             | 152 |

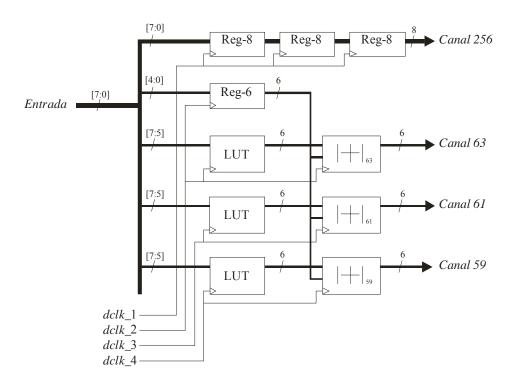

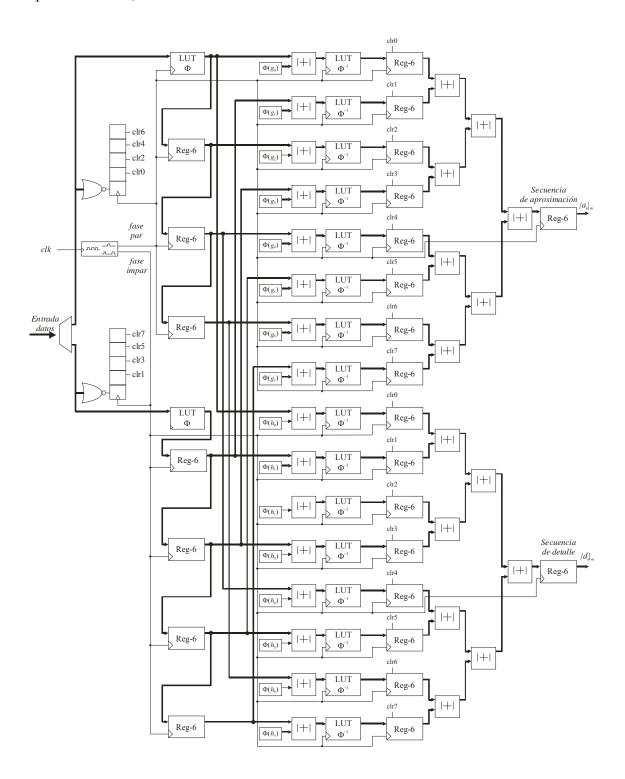

| 4.3.4. Transformada 1D-DWT por transformación al dominio de los índices.      | 158 |

| 4.3.4.1. Descripción del sistema                                              | 158 |

| 4.3.4.2. Implementación para simulación                                       | 161 |

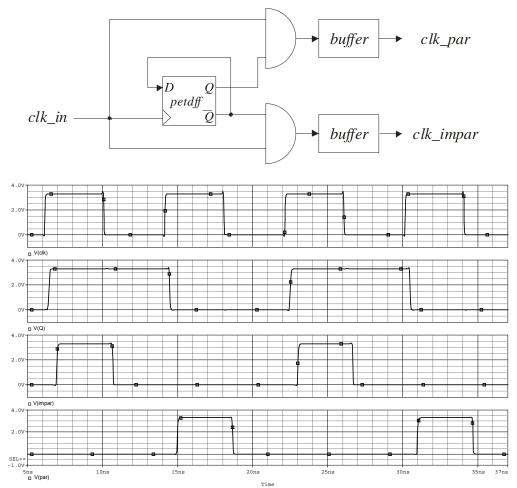

| 4.3.4.2.1. Sincronización del sistema                                         | 163 |

| 4.3.4.2.2. Conversión de binario a RNS                                  | 165   |

|-------------------------------------------------------------------------|-------|

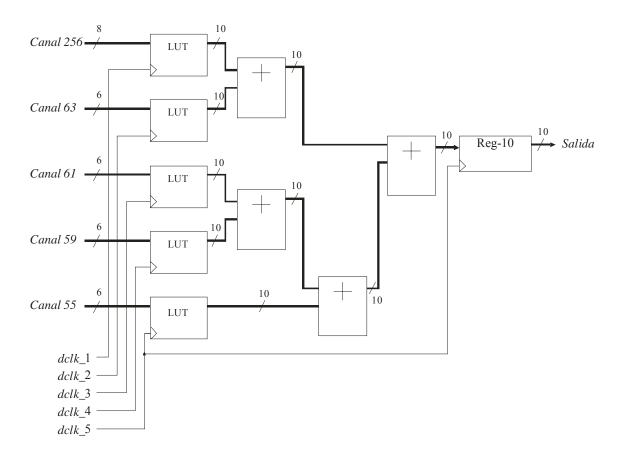

| 4.3.4.2.5. Canales del sistema 1D-DWT                                   | 166   |

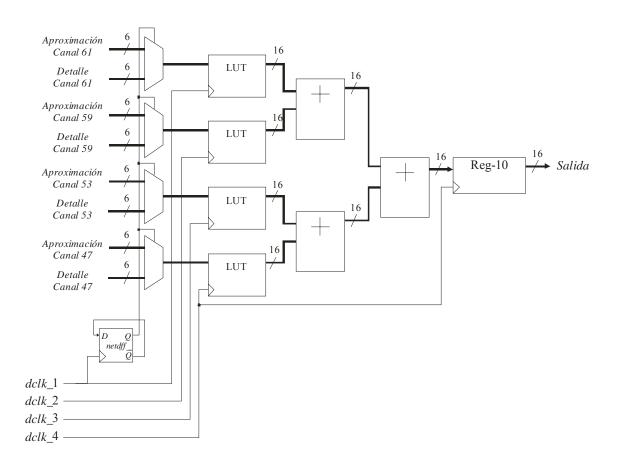

| 4.3.4.2.6. Conversión y escalado: móduo ε-CRT                           | 167   |

| 4.3.3.3. Resultados de simulación                                       | 168   |

| 4.3.5. Comparación de resultados                                        | 173   |

| 4.4 Conclusión                                                          | 178   |

| CAPÍTULO 5: APLICACIÓN EN DISPOSITIVOS LÓGICOS PROGRAMABLES             | S 181 |

| 5.1 Introducción                                                        | 182   |

| 5.1.1. Dispositivos lógicos programables. FPGAs                         | 183   |

| 5.1.1.1. Sincronización en FPGAs                                        | 185   |

| 5.1.2. Protección de módulos IP                                         | 191   |

| 5.2. Aplicación de la nueva estrategia de sincronización a dispositivos |       |

| lógicos programables                                                    | 192   |

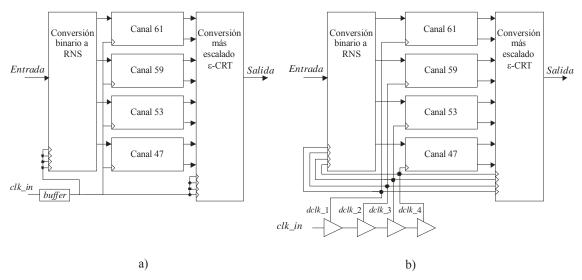

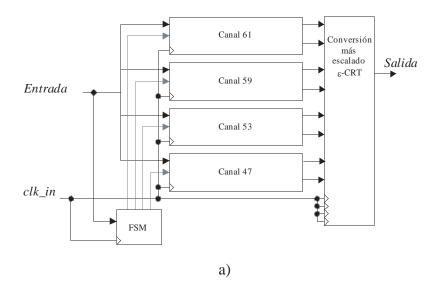

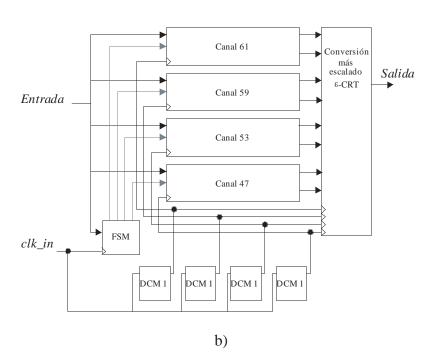

| 5.2.1. Descripción del sistema                                          | 193   |

| 5.2.1.1. Sincronización del sistema                                     | 194   |

| 5.2.1.2. Canales RNS de procesamiento y conversión más escalado         | 195   |

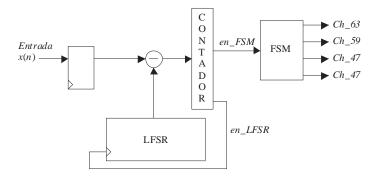

| 5.2.1.3. Lógica de extracción de la firma                               | 196   |

| 5.2.2. Implementación del sistema                                       | 198   |

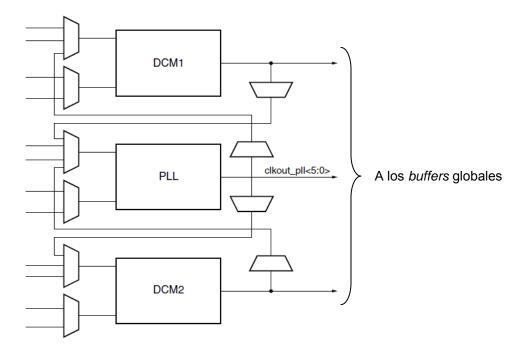

| 5.2.2.1. Generación de las señales de reloj                             | 200   |

| 5.3. Resultados experimentales                                          | 203   |

| 5.3.1. Efecto de la nueva estrategia de sincronización sobre el consumo | 206   |

| 5.3.2. Efecto de la nueva estrategia de sincronización sobre el proceso |       |

| de extracción de la firma                                               | 211   |

| 5.4 Conclusión                                                          | 214   |

| CAPÍTULO 6: CONCLUSIONES                                                | 217   |

| 6.1 Introducción                                                        | 218   |

| 6.2 Principales aportaciones                                            | 220   |

| 6.3 Líneas de investigación futuras                                     | 224   |

| 6.4 Conclusión                                                          | 225   |

| APÉNDICE A: GENERACIÓN DE LA SEÑAL DE RELOJ                             | 227   |

| A.1. Generación de la señal de reloj                                    | 228   |

| APÉNDICE B: ANÁLISIS DE LOS DISPOSITIVOS Y                              |       |

| MÓDULOS USADOS EN LAS SIMULACIONES                                      | 237   |

<u>Índice</u> v

| B.1. Transistores                          | 238 |

|--------------------------------------------|-----|

| B.2. Elementos de memoria                  | 240 |

| B.2.1. Biestables                          | 240 |

| B.2.2. Registros                           | 241 |

| B.2.3. Memorias ROM                        | 241 |

| B.3 Sumadores                              | 246 |

| A.3.1 Sumador binario de <i>n</i> bits     | 246 |

| A.3.2 Sumador módulo m                     | 247 |

| B.4 Otros módulos                          | 248 |

| B.4.1. Multiplexores                       | 249 |

| B.4.2. Puertas lógicas                     | 249 |

| B.4.3. Contador de 32 bits                 | 250 |

| B.5 Generador de la señal de reloj externa | 250 |

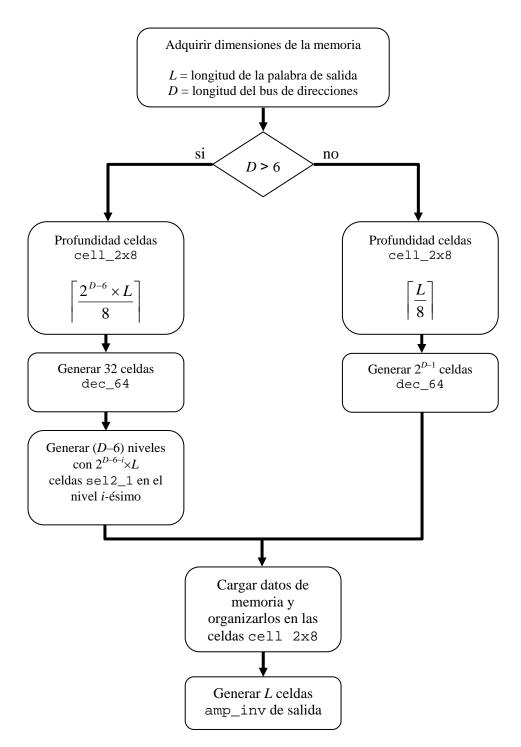

| APÉNDICE C: PROGRAMA GENERADOR DE MEMORIAS | 253 |

| C.1. Organigrama                           | 254 |

| C.2. Programa generador de librerías       | 255 |

| Bibliografía                               | 259 |

## ÍNDICE DE FIGURAS

| CAPÍTULO 1: INTRODUCCIÓN                                              | 1  |

|-----------------------------------------------------------------------|----|

| Figura 1.1. Evolución del número de dispositivos                      |    |

| integrados en un solo microprocesador                                 | 2  |

| Figura 1.2. Evolución del tamaño característico de los transistores   | 3  |

| Figura 1.3. Evolución de la frecuencia de funcionamiento diferentes   | ∠  |

| CAPÍTULO 2: SISTEMA NUMÉRICO DE RESIDUOS                              | 13 |

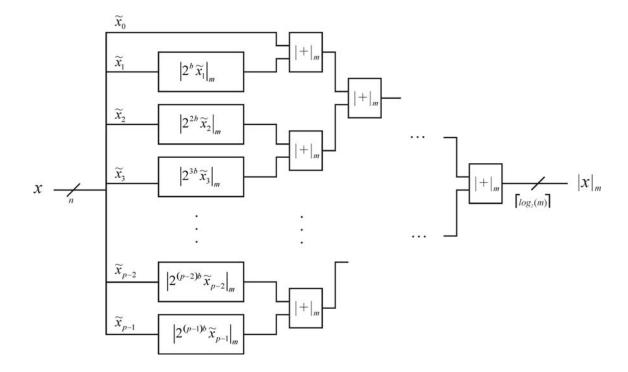

| Figura 2.1. Conversión por bloques de binario a RNS.                  |    |

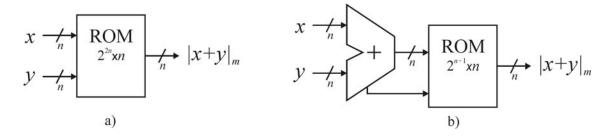

| Figura 2.2. Sumadores basados en memorias ROM                         | 30 |

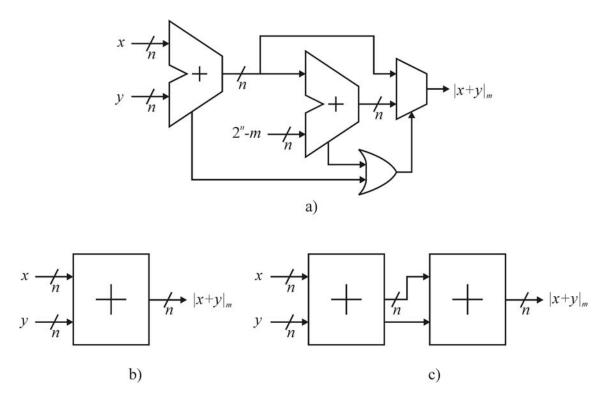

| Figura 2.3. Sumadores modulares basados en sumadores binarios         |    |

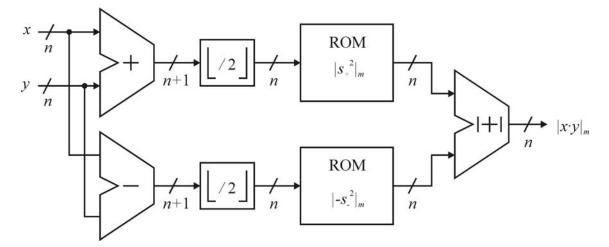

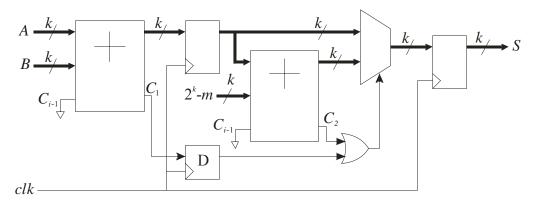

| Figura 2.4. Multiplicador módulo <i>m</i> basado en la ley cuadrática | 33 |

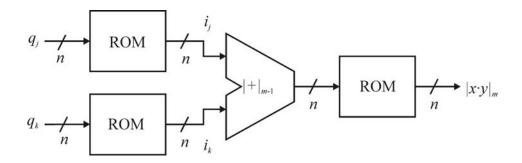

| Figura 2.5. Multiplicador basado en aritmética de índices.            | 34 |

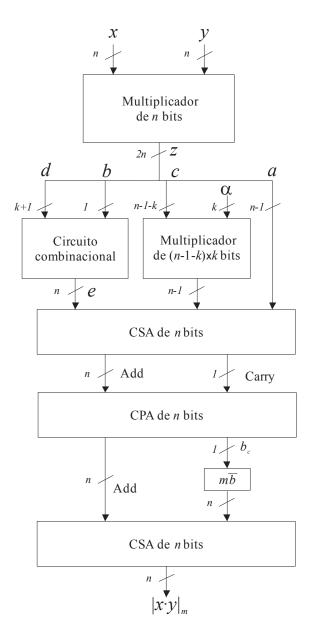

| Figura 2.6. Multiplicador módulo <i>m</i> que no hace uso de tablas   | 37 |

| CAPÍTULO 3: SINCRONIZACIÓN EN CIRCUITOS DIGITALES VLSI                | 41 |

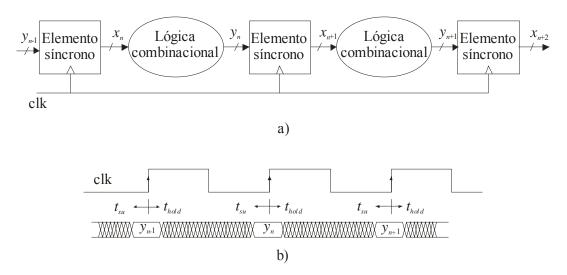

| Figura 3.1. Esquema de funcionamiento de un sistema síncrono          | 42 |

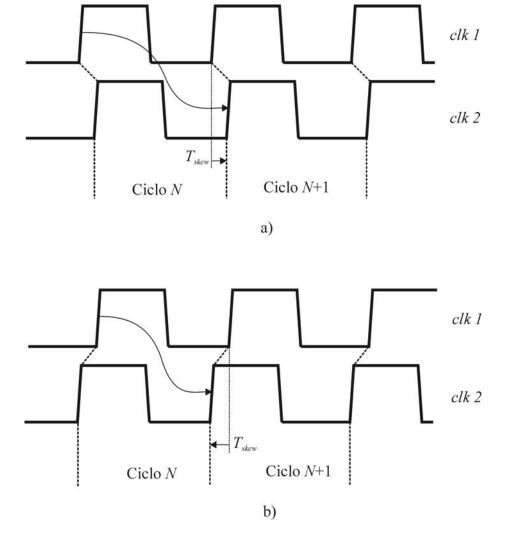

| Figura 3.2. Skew negativo (a) y positivo (b).                         | 52 |

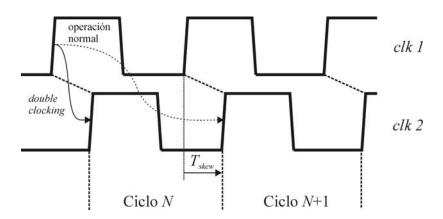

| Figura 3.3. Problema de carreras o double clocking                    |    |

| debido a un valor del skew negativo elevado                           | 53 |

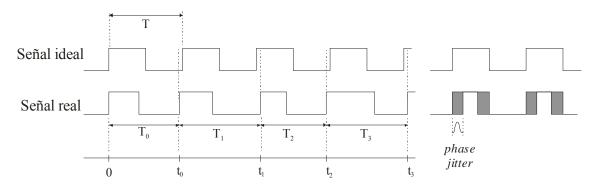

| Figura 3.4. Definición de <i>jitter</i> .                             | 56 |

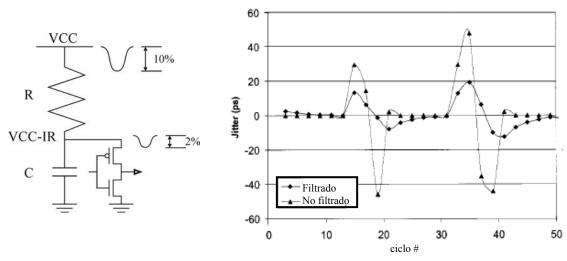

| Figura 3.5. Filtro RC para corrección del <i>jitter</i> [KUR01].      | 59 |

| Figura 3.6. Red de distribución no restringida.                       | 62 |

| Figura 3.7 Distribución no simétrica [RES98].                         | 63 |

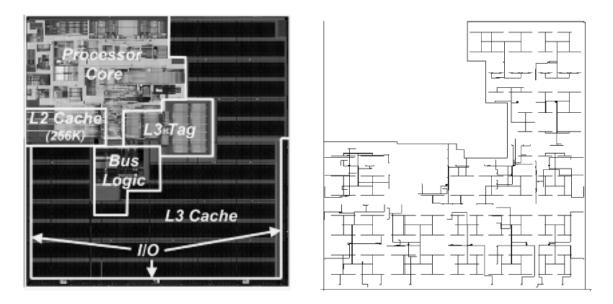

| Figura 3.8. Procesador Itanium® 2 y red de distribución               |    |

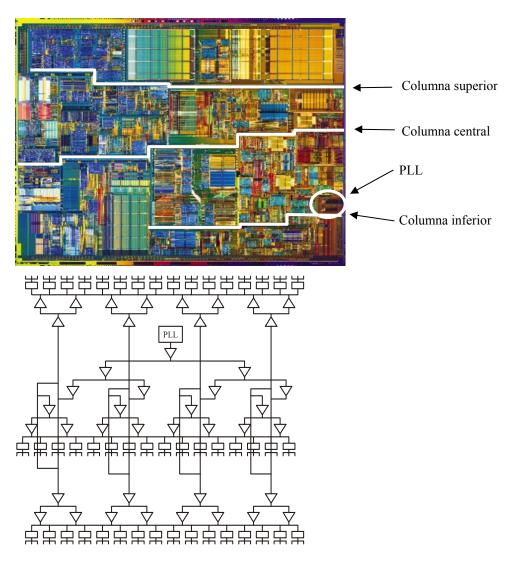

| del reloj de la caché de 3 <sup>er</sup> nivel [CHA05]                | 64 |

| Figura 3.9. R | led de distribución en <i>H-tree</i> .                                   | 65 |

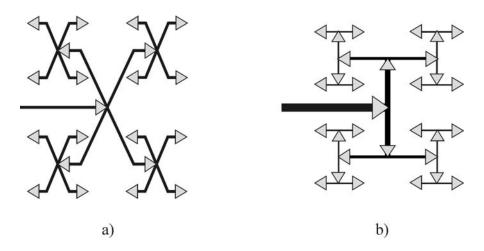

|---------------|--------------------------------------------------------------------------|----|

| Figura 3.10.  | Distribuciones en X-tree y H-tree con acoplamiento de impedancia         | 65 |

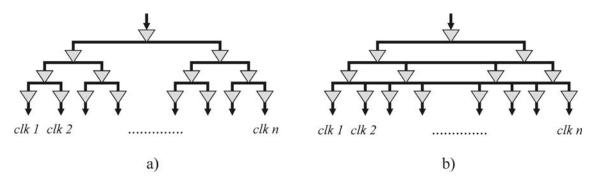

| Figura 3.11.  | Redes de distribución en árbol binario (a)                               |    |

|               | y árbol binario con conexiones intermedias (b)                           | 66 |

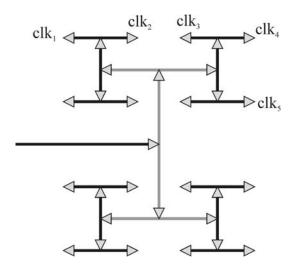

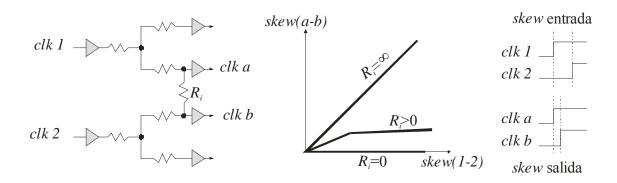

| Figura 3.12.  | Reducción del skew mediante interconexiones                              | 67 |

| Figura 3.13.  | Distribución de reloj del PowerPC 64b [HOF00]                            | 68 |

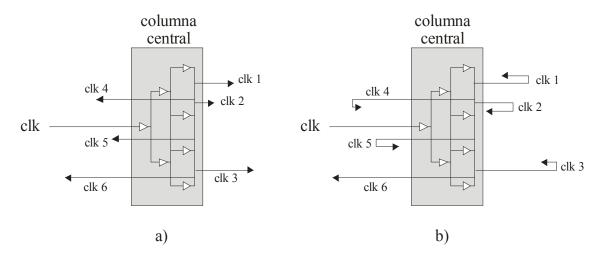

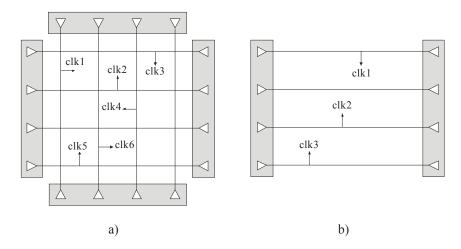

| Figura 3.14.  | Distribución en columna central (a)                                      |    |

|               | y con interconexiones equilibradas (b)                                   | 69 |

| Figura 3.15.  | Dsitribución mediante columnas centrales                                 |    |

|               | en modelos de procesador Alpha® [GRO98]                                  | 69 |

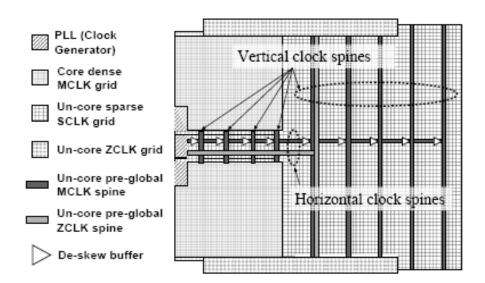

| Figura 3.16.  | Columnas de distribución de reloj en Pentium® 4 [KUR01]                  | 70 |

| Figura 3.17.  | Rejilla bidimensional (a) y unidimensional (b)                           | 72 |

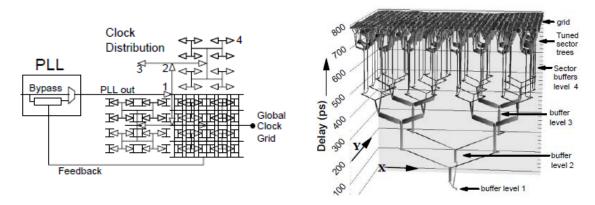

| Figura 3.18.  | Distribución del reloj y retardos a través                               |    |

|               | del chip en el procesador Power4 [RES02]                                 | 73 |

| Figura 3.19.  | Regiones de reloj y distribución en el procesador Xeon® [TAM06]          | 74 |

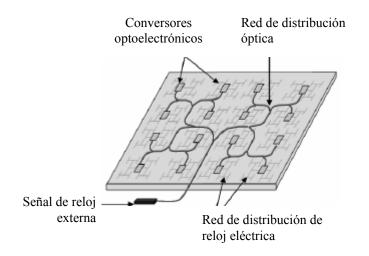

| Figura 3.20.  | Red de distribución global óptica [TOS07]                                | 75 |

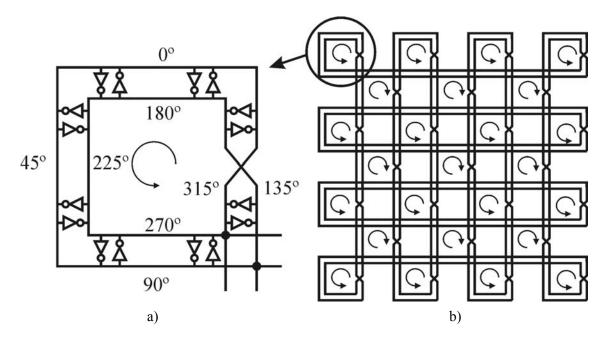

| Figura 3.21.  | RTWO (a) y matriz de 25 RTWOs (b).                                       | 77 |

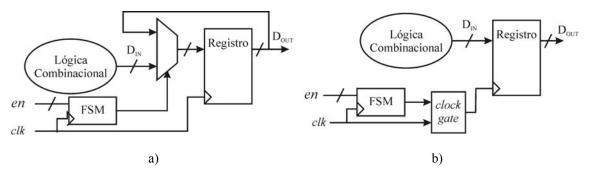

| Figura 3.22.  | Registro con habilitación de carga síncrona (a).                         |    |

|               | Aplicación de clock gating (b)                                           | 79 |

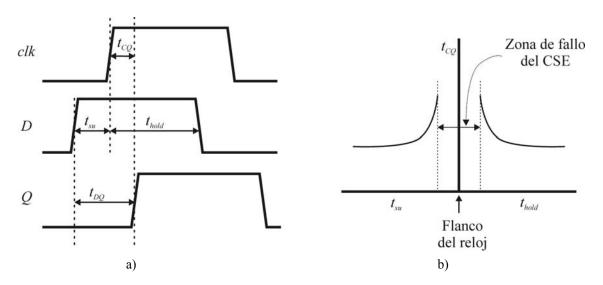

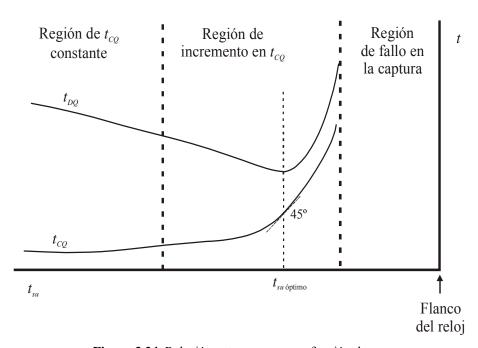

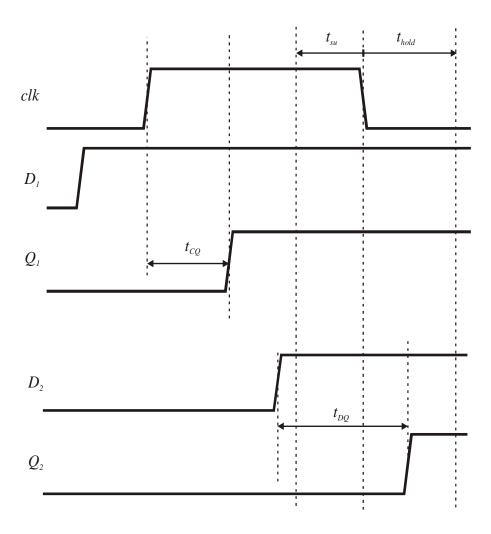

| Figura 3.23.  | Retardos principales en CSEs (a).                                        |    |

|               | Dependencia de $t_{CQ}$ con $t_{DC}$ y $t_{CD}$ (b)                      | 82 |

| Figura 3.24.  | Relación entre $t_{CQ}$ y $t_{DQ}$ en función de $t_{su}$ .              | 83 |

| Figura 3.25.  | Definiciones de t <sub>su</sub> y t <sub>hold</sub>                      | 85 |

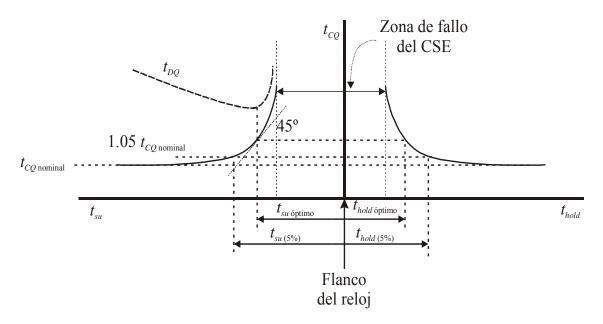

| Figura 3.26.  | Diferentes estrategias de sincronización mediante latches:               |    |

|               | a) lógica C <sup>2</sup> CMOS con NPTC; b) NORA CMOS dinámica;           |    |

|               | c) TSPC CMOS dinámica                                                    | 89 |

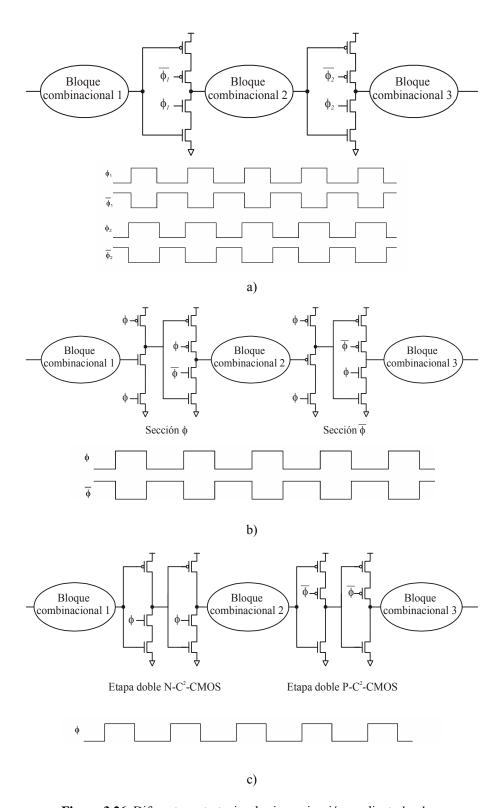

| Figura 3.27.  | Latch tipo master-slave [WAR06]                                          | 90 |

| Figura 3.28.  | Diagrama de captura de datos en latch:                                   |    |

|               | dato anticipado (D <sub>1</sub> ) y dato retardado (D <sub>2</sub> )     | 91 |

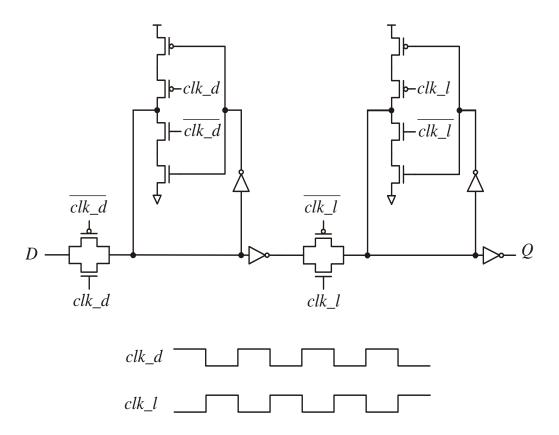

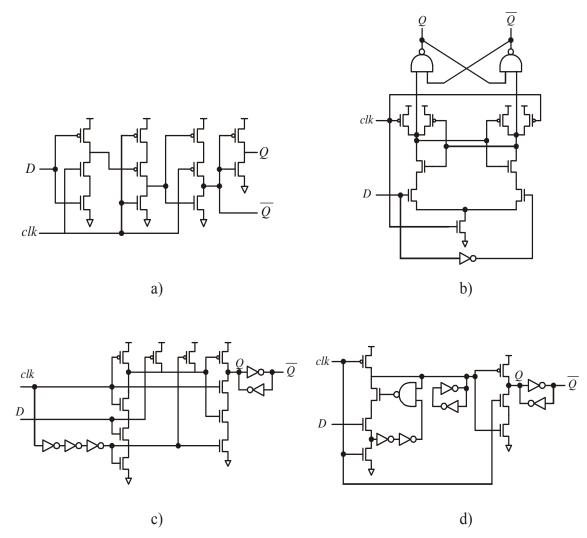

| Figura 3.29.  | Cuatro ejemplos de <i>flip-flop</i> típicos sincronizados mediante TSPC: |    |

|               | a) flip-flop basado en biestable tipo D; b) SAFF; c) HLFF; d) SDFF.      | 93 |

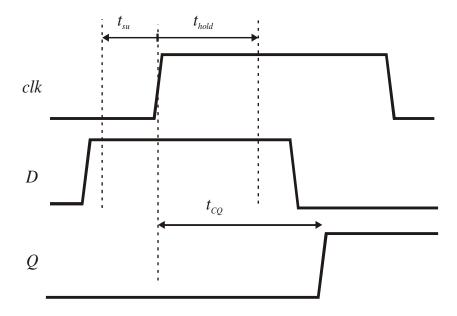

| Figura 3.30.  | Cronograma de flip-flop                                                  | 94 |

| CAPÍTULO 4: NUEVA ESTRATEGIA DE SINCRONIZACIÓN                                       |

|--------------------------------------------------------------------------------------|

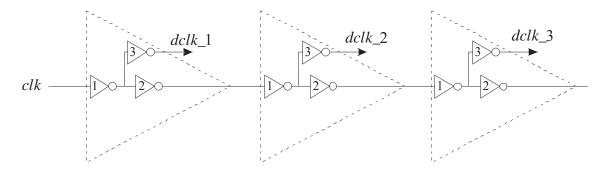

| Figura 4.1. Esquema de línea de generación de las señales de reloj desfasadas:       |

| (1) inversor de entrada, con una gran capacidad de entrada;                          |

| (2) inversor de salida, de dimensiones mínimas;                                      |

| (3) inversor restaurador, genera la señal de reloj efectiva 103                      |

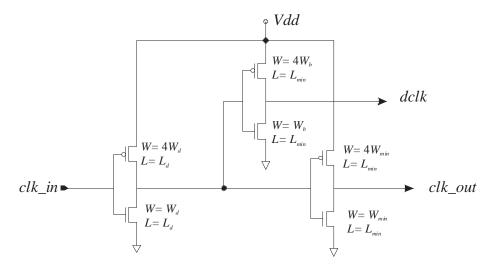

| Figura 4.2. Detalle de la celda parametrizable dCLK_cell                             |

| Figura 4.3. Representación de la señal de reloj de                                   |

| entrada original junto con las señales levemente desfasadas 106                      |

| Figura 4.4. Retardo por celda en función de $L_d$ y $W_d$                            |

| Figura 4.5. Retardo en función de $L_d$ , $W_d$ y $W_b$                              |

| Figura 4.6. Consumo de la celda parametrizable en función de $L_d$ , $W_d$ y $W_b$   |

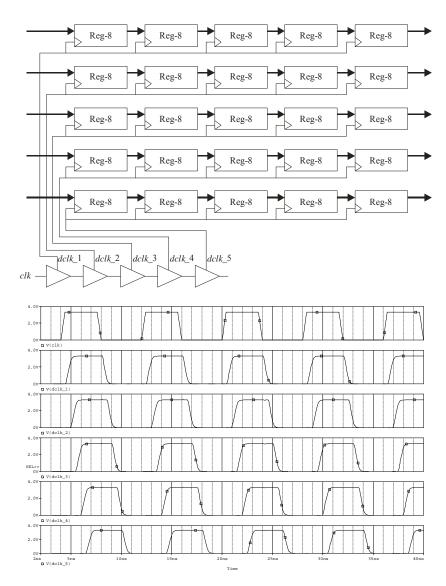

| Figura 4.7. Sitema de prueba para apreciar el efecto del perfil de la                |

| señal de reloj sobre el consumo                                                      |

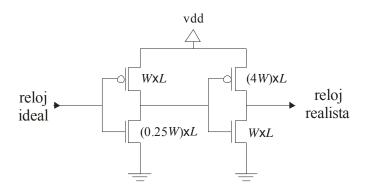

| Figura 4.8. <i>Buffer</i> regenerador de señal de reloj                              |

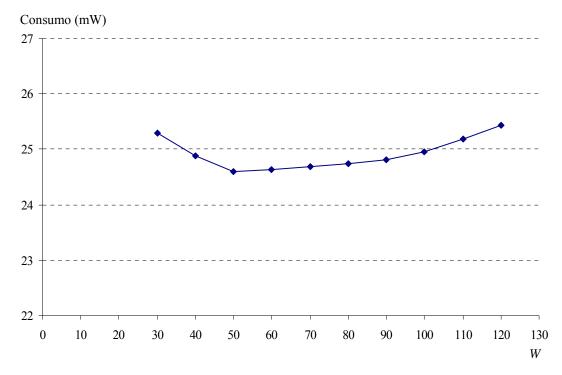

| Figura 4.9. Consumo global de un sistema en función                                  |

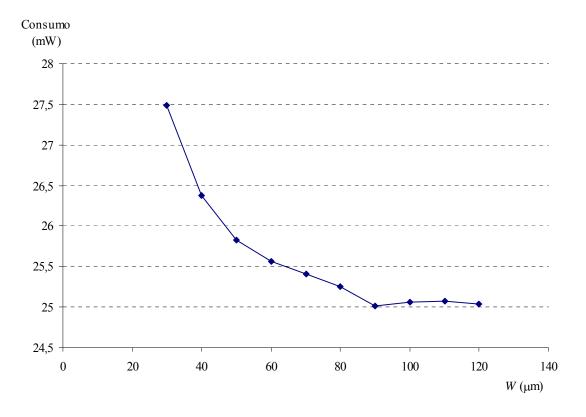

| de la anchura del canal del buffer117                                                |

| Figura 4.10. Consumo de un sistema, sin incluir la red de distribución de la señal   |

| de reloj, en función del tamaño del buffer que lo sincroniza119                      |

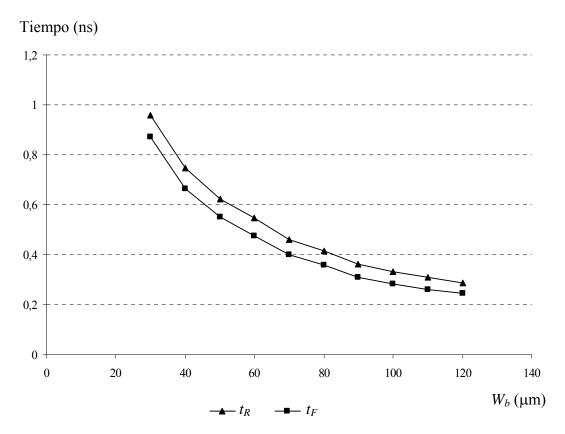

| Figura 4.11. Tiempos de subida y bajada en función del tamaño del buffer             |

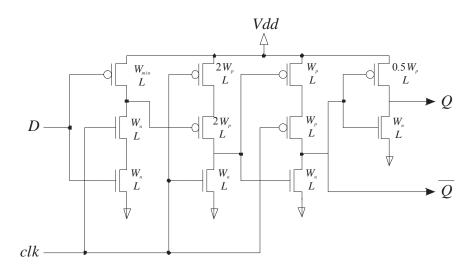

| Figura 4.12. Biestable sincronizado por flanco de bajada                             |

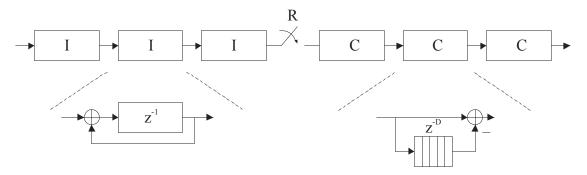

| Figura 4.13. Filtro CIC de tres etapas.                                              |

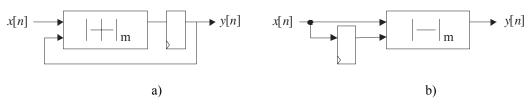

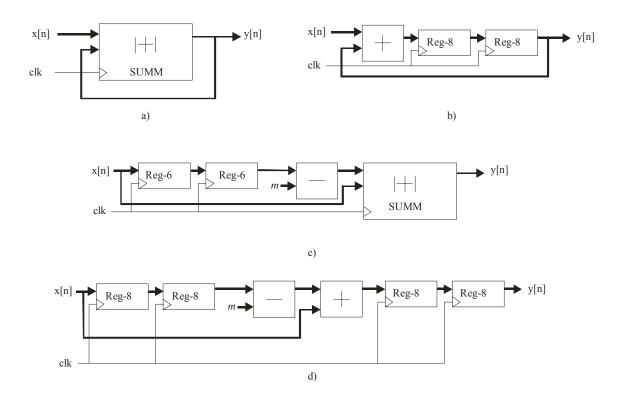

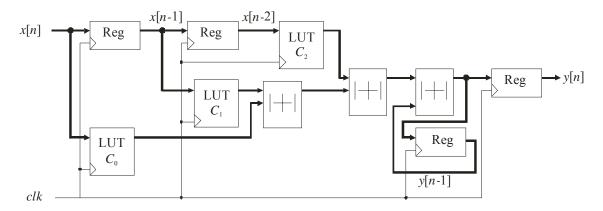

| Figura 4.14. Esquema de un integrador (a) y un peine (D=1) (b) para el procesamiento |

| de señales discretas basados en sumadores modulares                                  |

| Figura 4.15. Esquema del filtro CIC sincronizado mediante un                         |

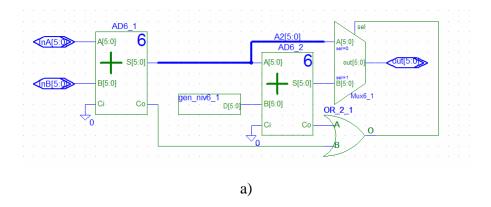

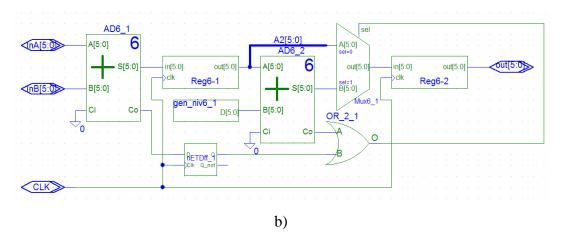

| único reloj (a) y celdas dCLK_cell (b)                                               |

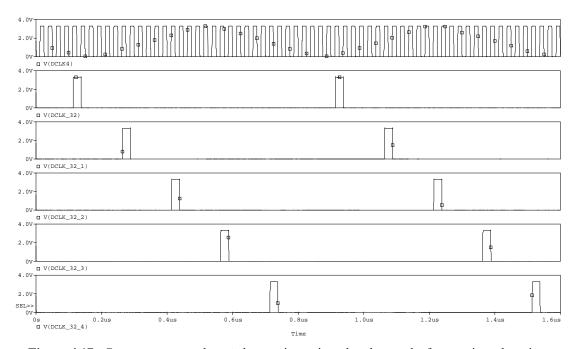

| Figura 4.16. Reductores de frecuencia para las dos estrategias de sincronización 126 |

| Figura 4.17. Cronograma con la señal que sincroniza el reductor de                   |

| frecuencia y las cinco señales generadas por éste                                    |

| Figura 4.18. Señales de reloj desfasadas generadas mediante                          |

| las celdas dCLK_cell                                                                 |

| Figura 4.19. Módulo de conversión de binario a RNS                                   |

| Figura 4.20. Sumador modular con cauce segmentado y salida registrada                |

| Figura 4.21. Implementación de integradores de 6 y 8 bits (a y b,                    |

| respectivamente) y peines para los canales de 6 y 8 bits (c y d) 134                 |

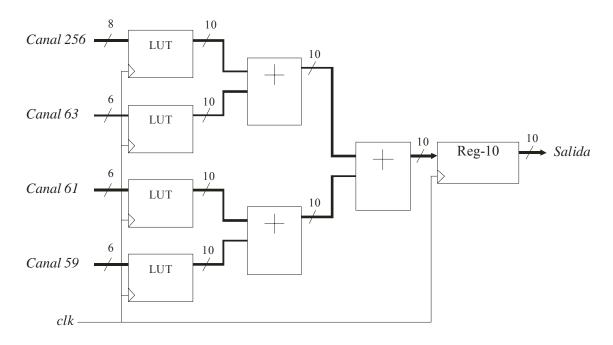

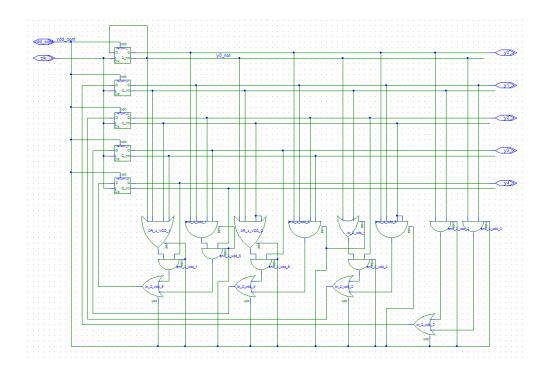

| Figura 4.22. Módulo de conversión más escalado ε-CRT para el filtro CIC13        |

|----------------------------------------------------------------------------------|

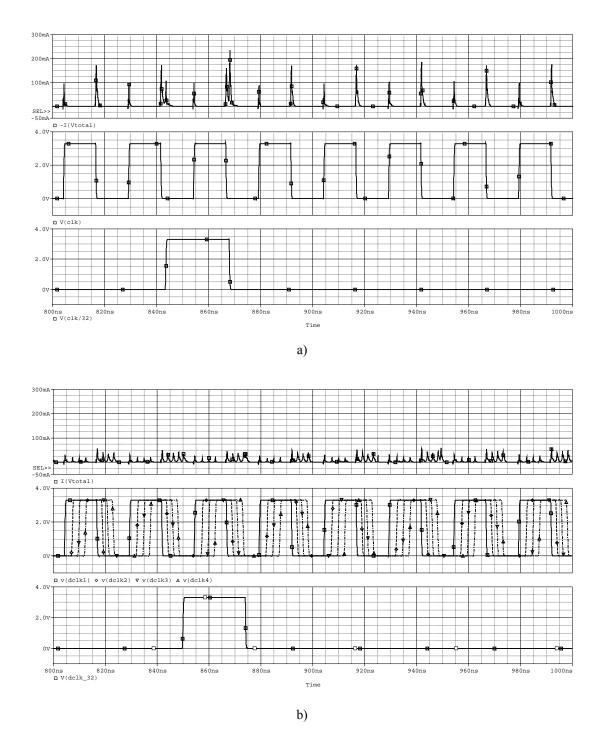

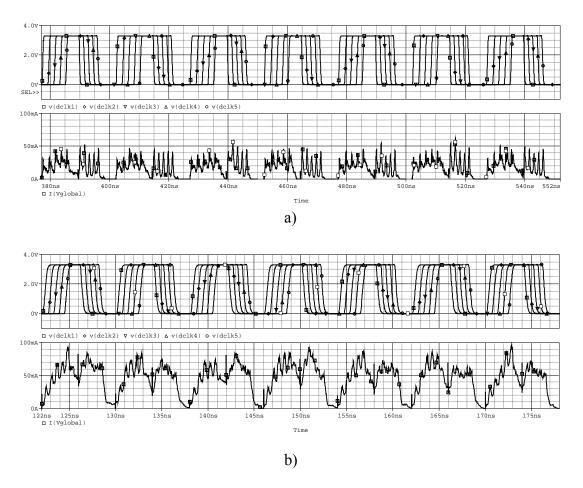

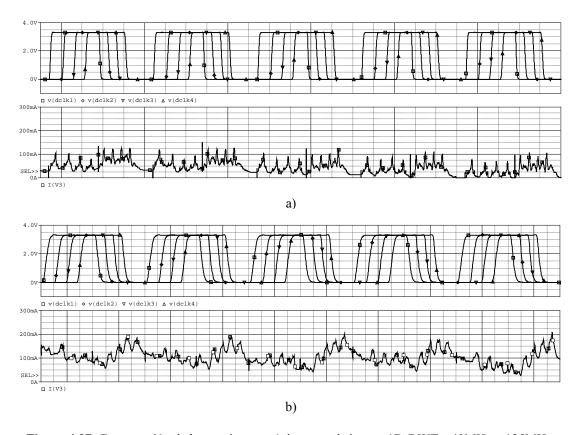

| Figura 4.23. Señales de reloj y corriente instantánea con reloj único (a)        |

| y reloj distribuido (b)13                                                        |

| Figura 4.24. Incremento del consumo en sistemas sincronizados por                |

| celdas dCLK_cell                                                                 |

| Figura 4.25. Implementación discreta de un controlador PID                       |

| Figura 4.26. Implementación para simulación de un controlador                    |

| PID basado en RNS de cinco canales mediante las                                  |

| dos metodologías de sincronización                                               |

| Figura 4.27. Módulo de conversión de binario a RNS del controlador PID150        |

| Figura 4.28. Sumador modular combinacional                                       |

| Figura 4.29. Canal PID implementado mediante tablas de consulta                  |

| Figura 4.30. Módulo de conversión más escalado ε-CRT para el controlador PID15   |

| Figura 4.31. Comparación de los valores máximos de las demandas de corriente 15. |

| Figura 4.32. Comparación de corrientes con reloj distribuído a 40MHz (a)         |

| y 125MHz (b)                                                                     |

| Figura 4.33. Arquitectura para la realización de la transformada                 |

| 1D-DWT por transformación al dominio de los índices                              |

| Figura 4.34. Implementación de un filtro basado en RNS parala transformada       |

| 1D-DWT wavelets mediante las dos estrategias de sincronización 16                |

| Figura 4.35. Divisor de la señal de reloj en sus fases y                         |

| señales de reloj más relevantes                                                  |

| Figura 4.36. Módulo de conversión y escalado ε-CRT en el sistema                 |

| 1D-DWT wavelets                                                                  |

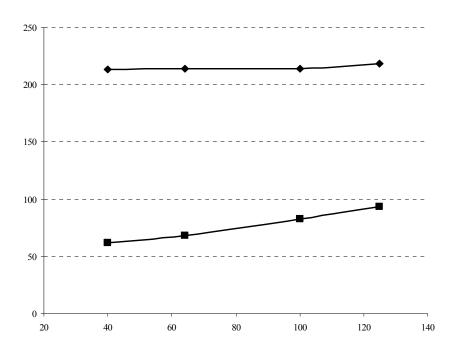

| Figura 4.37. Comparación de las corrientes máximas en el sistema 1D-DWT          |

| a 40MHz y 125MHz                                                                 |

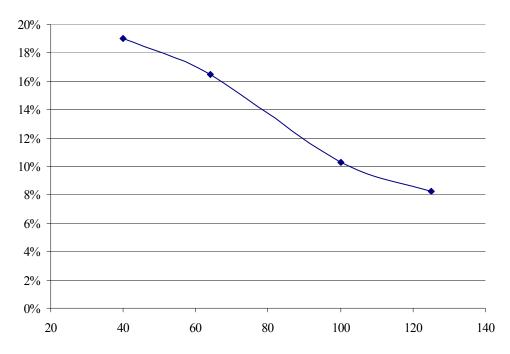

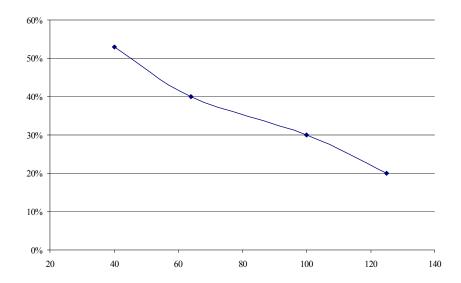

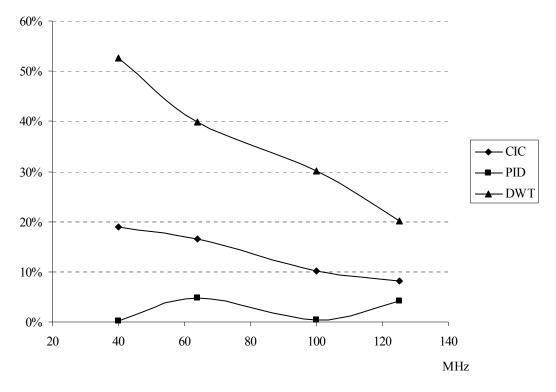

| Figura 4.38. Variación porcentual del incremento de consumo                      |

| al aplicar varias señales desfasadas17                                           |

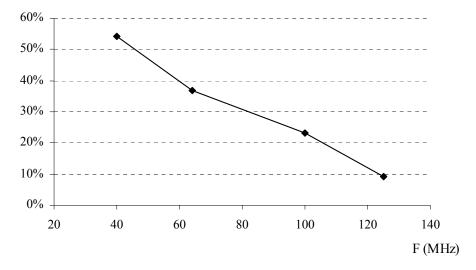

| Figura 4.39. Variación porcentual del consumo dinámico en el sistema 1D-DWT17    |

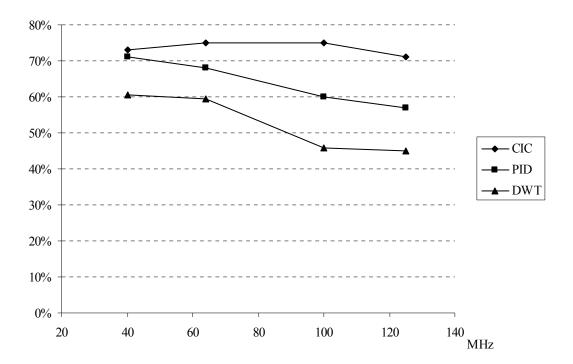

| Figura 4.40. Reducción de los picos de corriente en los sistemas estudiados17    |

| Figura 4.41. Incremento del consumo debido a la inclusión                        |

| de la cadena de celdas dCLK cell                                                 |

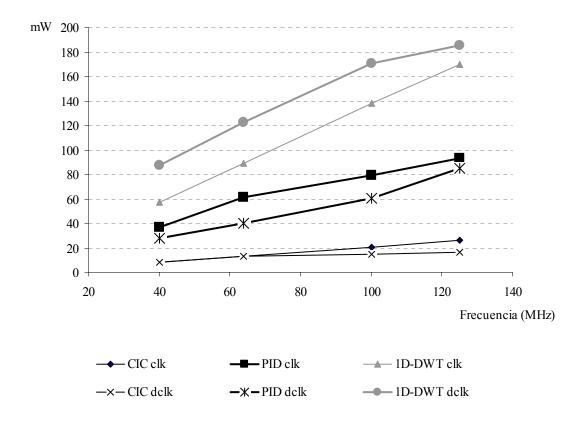

| Figura 4.42. Consumo dinámico de los sistemas bajo las dos                    |    |

|-------------------------------------------------------------------------------|----|

| metodologías de sincronización1                                               | 78 |

| CAPÍTULO 5: APLICACIÓN EN DISPOSITIVOS                                        |    |

| LÓGICOS PROGRAMABLES1                                                         | 81 |

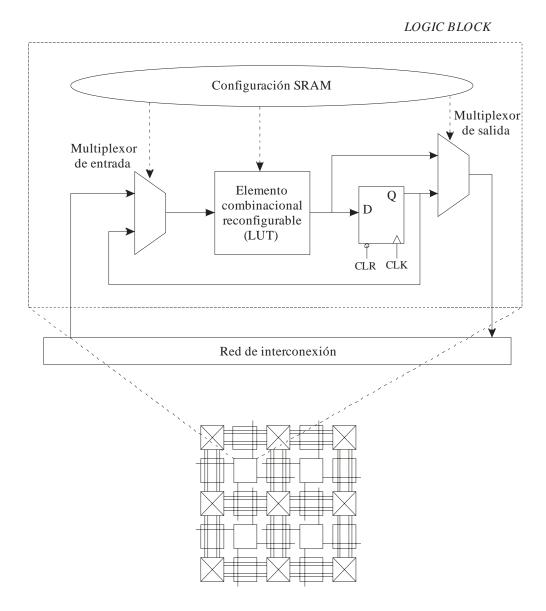

| Figura 5.1. Arquitectura general de una FPGA y detalle de un Bloque Lógico 1  | 84 |

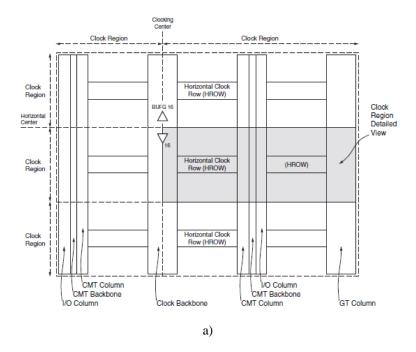

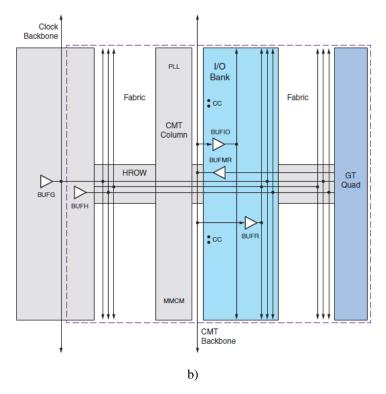

| Figura 5.2. Arquitectura de la distribución global de la señal de reloj (a)   |    |

| y detalle de la red de distribución de una región de reloj (b)                |    |

| en la serie 7 de Xilinx [XIL12a]                                              | 86 |

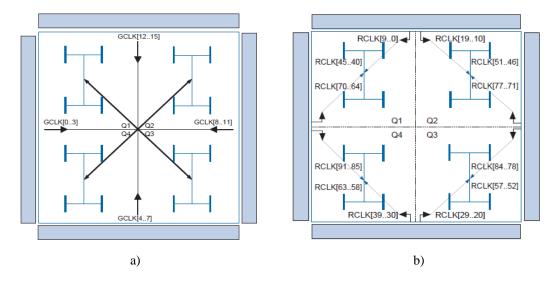

| Figura 5.3. Distribuciones de reloj global (a) y                              |    |

| regional (b) en la FPGA Stratix V [XIL12] 1                                   | 87 |

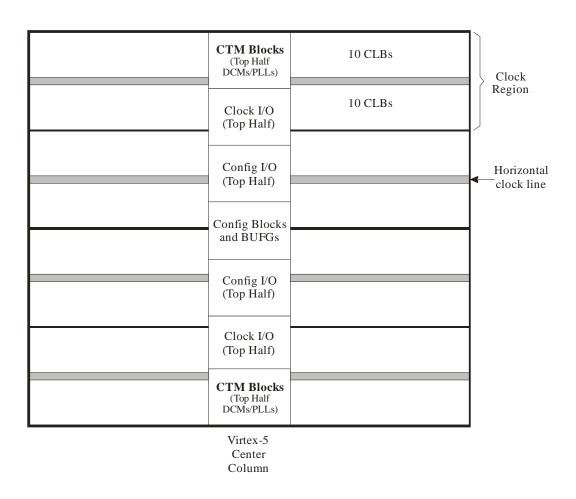

| Figura 5.4. Estructura de alto nivel de la Virtex-5 XC5VLX30 [XIL12b] 1       | 88 |

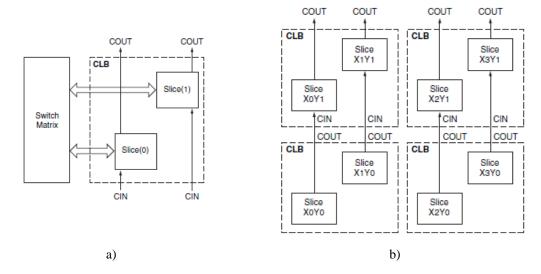

| Figura 5.5. Estructura de un CLB (a) e interconexiones entre CLBs y           |    |

| slices (b) [XIL12b]1                                                          | 89 |

| Figura 5.6. Esquema general de un CTM en la FPGA Virtex-5 [XIL12b] 1          | 90 |

| Figura 5.7. Sistema 1D-DWT sincronizado mediante una señal de reloj única (a) |    |

| y mediante DCMs (b)1                                                          | 94 |

| Figura 5.8. Lógica de extracción de la firma mediante un LFSR                 | 97 |

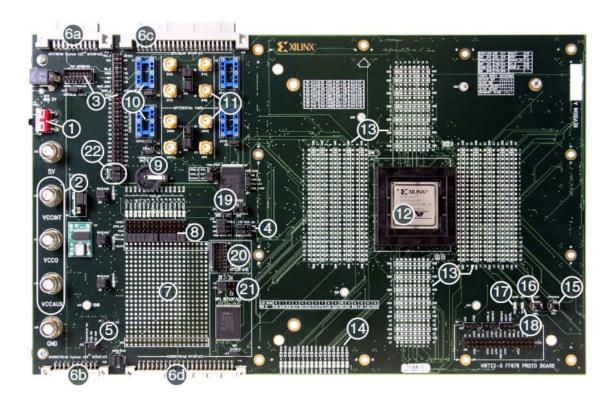

| Figura 5.9. Placa de prototipado Virtex-5 LX [XIL11]                          | 98 |

| CAPÍTULO 6: CONCLUSIONES2                                                     | 17 |

| APÉNDICE A: GENERACIÓN DE LA SEÑAL DE RELOJ2                                  | 27 |

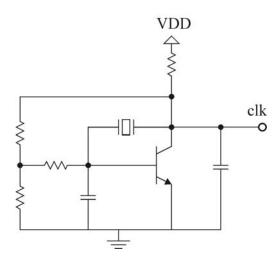

| Figura A.1. Circuito oscilador de cristal                                     | 28 |

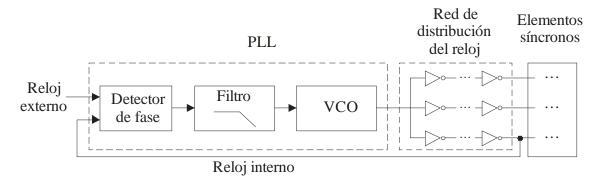

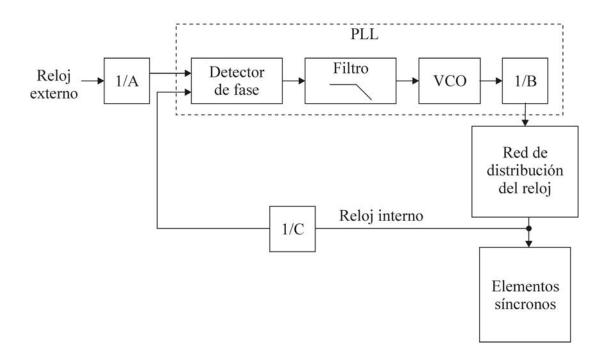

| Figura A.2. Esquema general de un PLL                                         | 29 |

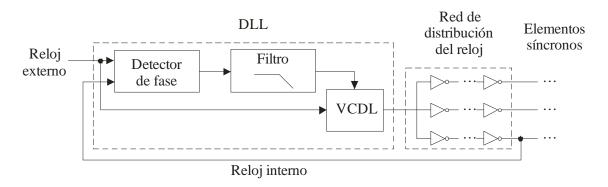

| Figura A.3. Esquema general de un DLL.                                        | 30 |

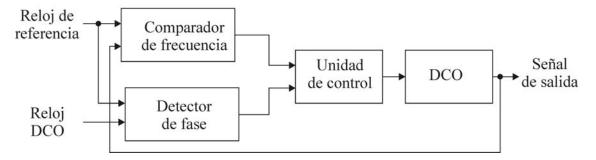

| Figura A.4. Diagrama de bloques de un sistema ADPLL                           |    |

| current–starved ring oscillator2                                              | 32 |

| Figura A.5. PLL como multiplicador de frecuencia                              | 33 |

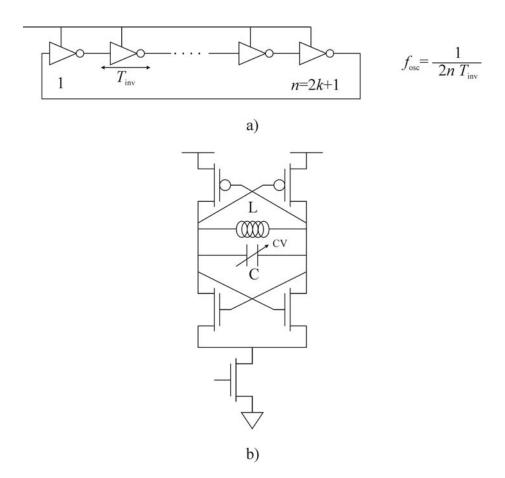

| Figura A.6. Oscilador basado en anillo (a) y en oscilador LC (b)              | 34 |

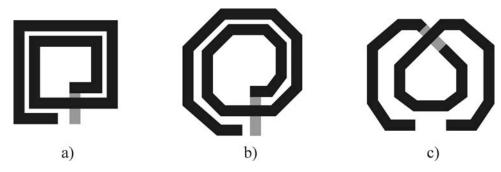

| Figura A.7 Inductores espirales de dos vueltas:                               |    |

| a) cuadrado, b) octogonal y c) octogonal simétrico2                           | 35 |

| APÉNDICE B: ANÁLISIS DE LOS DISPOSITIVOS Y                                   |     |

|------------------------------------------------------------------------------|-----|

| MÓDULOS USADOS EN LAS SIMULACIONES                                           | 237 |

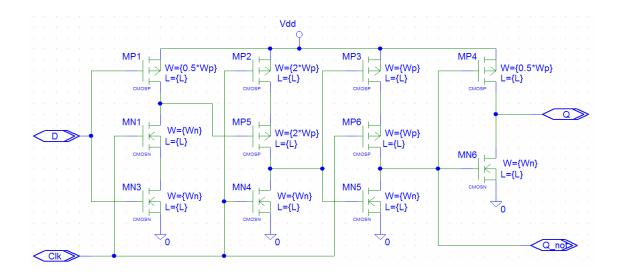

| Figura B.1. Esquemático de un biestable tipo D activado por flanco de bajada | 240 |

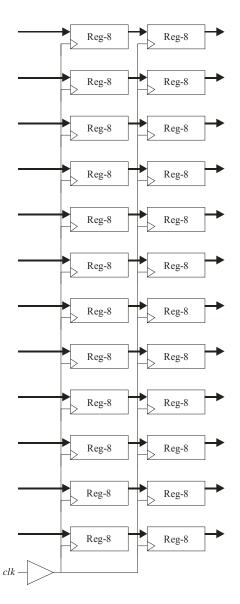

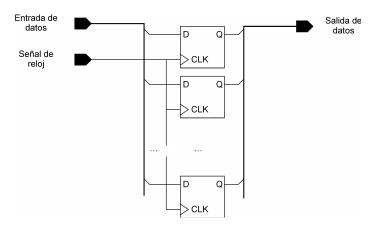

| Figura B.2. Implementación de un registro de <i>n</i> bits.                  | 241 |

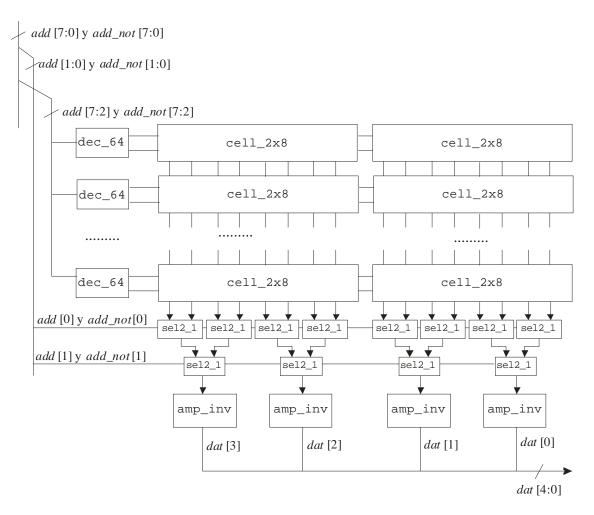

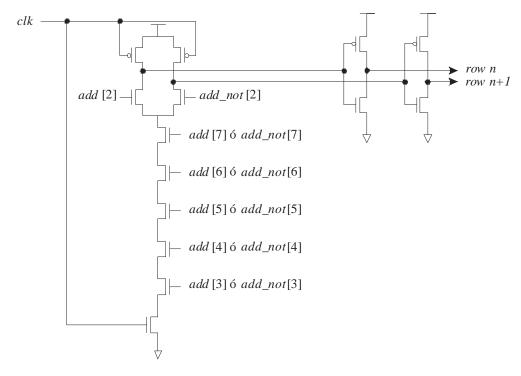

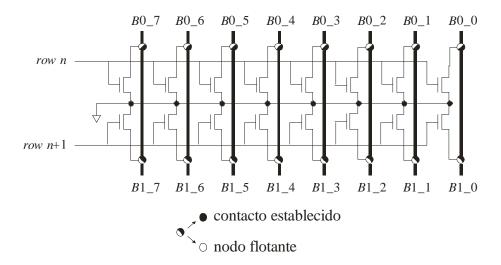

| Figura B.3. Visión de global de un módulo de memoria de 256×4                | 242 |

| Figura B.4. Celda de selección de filas dec_64                               | 243 |

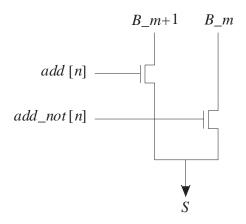

| Figura B.5. Celda de almacenamiento de datos cell_2x8                        | 244 |

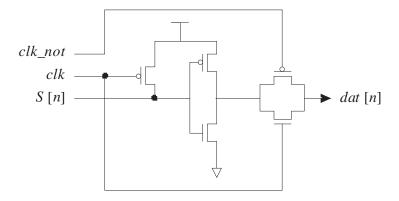

| Figura B.6. Esquemático de la celda sel2_1                                   | 244 |

| Figura B.7. Esquemático de la celda amp_inv                                  | 245 |

| Figura B.8. Sumador completo de un bit.                                      | 246 |

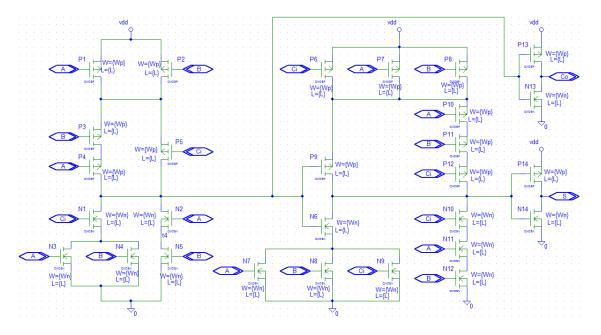

| Figura B.9. Sumadores modulares simple (a) y con pipelinig (b)               | 247 |

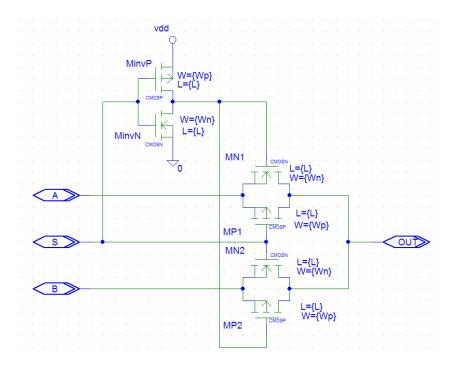

| Figura B.10. Celda básica del multiplexor                                    | 248 |

| Figura B.11. Contador de 32 bits.                                            | 249 |

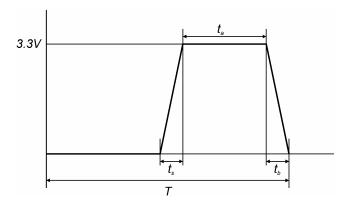

| Figura B.12. Señal de reloj de entrada.                                      | 250 |

|                                                                              |     |

| APÉNDICE C: PROGRAMA GENERADOR DE MEMORIAS                                   | 253 |

| Figura C.1. Ejemplo de archivo de descripción de la memoria                  | 254 |

| Figura C.2. Organigrama para la generación de la librería                    | 256 |

# ÍNDICE DE TABLAS

| CAPÍTULO 1: INTRODUCCIÓN                                                                     |

|----------------------------------------------------------------------------------------------|

| CAPÍTULO 2: SISTEMA NUMÉRICO DE RESIDUOS                                                     |

| CAPÍTULO 3: SINCRONIZACIÓN EN CIRCUITOS DIGITALES VLSI 41                                    |

| CAPÍTULO 4: NUEVA ESTRATEGIA DE SINCRONIZACIÓN                                               |

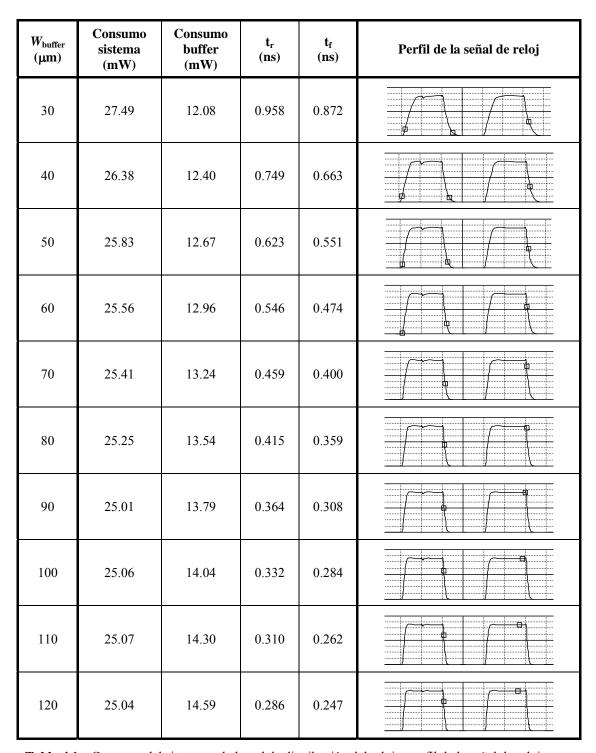

| Tabla 4.1. Consumo del sistema y de la red de distribución del reloj y perfil de la          |

| señal de reloj en función del tamaño de buffer                                               |

| regenerador de la señal de reloj118                                                          |

| Tabla 4.2. Área total de puerta de los transistores sincronizados                            |

| por la señal de reloj de un biestable estándar                                               |

| Tabla 4.3. Dimensionado de salida de los <i>buffers</i> y celdas dclk_cell en filtro CIC 128 |

| Tabla 4.4. Retardo entre señales de reloj adyacentes y                                       |

| valor de los parámetros $L_d$ y $W_d$                                                        |

| Tabla 4.5. Comparación de corrientes máximas con reloj único                                 |

| y distribuido en el filtro CIC.                                                              |

| Tabla 4.6. Comparación de la máxima derivada de la corriente en el filtro CIC 140            |

| Tabla 4.7. Comparación de consumos con ambas estrategias de sincronización 14                |

| Tabla 4.8. Consumo del filtro CIC sin actividad a la entrada de datos                        |

| Tabla 4.9. Comparación del consumo dinámico en el flitro CIC                                 |

| Tabla 4.10. Dimensionado del <i>buffer</i> y de las celdas dCLK_cell                         |

| Tabla 4.11. Dimensionado de las celdas dCLK_cell para alcanzar                               |

| los retardos requeridos                                                                      |

| Tabla 4.12. Corrientes máximas con reloj único y distribuido                                 |

| en el controlador PID                                                                        |

| Tabla 4.13. Comparación de la máxima derivada de la corriente                      |     |

|------------------------------------------------------------------------------------|-----|

| en el controlador PID.                                                             | 155 |

| Tabla 4.14. Comparación de consumos en el controlador PID                          | 156 |

| Tabla 4.15. Consumo del controlador PID sin actividad en la entrada de datos       | 157 |

| Tabla 4.16. Comparación del consumo dinámico en el controlador PID                 | 158 |

| Tabla 4.17. Dimensionado del <i>buffer</i> y de las celdas dCLK_cell               | 163 |

| Tabla 4.18. Dimensionado de las celdas dCLK_cell para alcanzar los retardos        |     |

| requeridos                                                                         | 164 |

| Tabla 4.19. Dimensiones de los buffers que generan las señales internas            |     |

| de los filtros 1D-DWT                                                              | 165 |

| Tabla 4.20. Corrientes máximas con reloj único y                                   |     |

| distribuido en el sistema 1D-DWT.                                                  | 168 |

| Tabla 4.21. Comparación de la máxima derivada de la                                |     |

| corriente en el sistema 1D-DWT.                                                    | 169 |

| Tabla 4.22. Comparación de consumos en el sistema 1D-DWT                           | 170 |

| Tabla 4.23. Consumo del filtro 1D-DWT sin actividad en la entrada de datos         | 171 |

| Tabla 4.24. Comparación del consumo dinámico en el sistema 1D-DWT                  | 172 |

| Tabla 4.25. Descenso porcentual de la derivada de la corriente al aplicar la nueva |     |

| estrategia de sincronización                                                       | 174 |

| CAPÍTULO 5: APLICACIÓN EN DISPOSITIVOS LÓGICOS                                     |     |

| PROGRAMABLES                                                                       | 181 |

| Tabla 5.1. Recursos empleados y frecuencia máxima de funcionamiento                | 200 |

| Tabla 5.2. Desfase generado por cada DCM en función de la frecuencia               | 202 |

| Tabla 5.3. Consumo del sistema con SEF manual.                                     | 203 |

| Tabla 5.4. Consumo del sistema con SEF generada mediante LFSR.                     | 204 |

| Tabla 5.5. Consumo estático del sistema.                                           | 205 |

| Tabla 5.6. Influencia sobre el consumo de la inclusión de los DCMs y de la         |     |

| aplicación de la nueva estrategia de sincronización.                               | 206 |

| Tabla 5.7. Consumo dinámico del sistema con SEF manual                             | 208 |

| Tabla 5.8. Consumo dinámico del sistema con SEF generada mediante LFSR             | 209 |

| Tabla 5.9. Reducción porcentual del consumo debida a los DCMs.                     | 210 |

| Tabla 5.10. Variaciones en el consumo entre los modos de                           |     |

| funcionamiento normal y de extracción de la firma                                  | 211 |

<u>Índice de tablas</u> xv

| Tabla 5.11. Variaciones en el consumo dinámico entre los modos              |     |

|-----------------------------------------------------------------------------|-----|

| de funcionamiento normal y de extracción de la firma                        | 212 |

|                                                                             |     |

| CAPÍTULO 6: CONCLUSIONES                                                    | 213 |

|                                                                             |     |

| APÉNDICE A: GENERACIÓN DE LA SEÑAL DE RELOJ                                 | 227 |

|                                                                             |     |

| APÉNDICE B: ANÁLISIS DE LOS DISPOSITIVOS Y                                  |     |

| MÓDULOS USADOS EN LAS SIMULACIONES                                          | 237 |

| Tabla B.1. Dimensiones de los transistores NMOS y PMOS                      | 239 |

| Tabla B.2. Especificaciones para las dos señales de reloj ideales aplicadas | 250 |

|                                                                             |     |

| APÉNDICE C: PROGRAMA GENERADOR DE MEMORIAS                                  | 253 |

## ABREVIATURAS Y SIGLAS

A continuación se recogen las abreviaturas y siglas que aparecen a lo largo de esta tesis para facilitar su lectura.

- **A/D** Analógico/digital.

- **ADPLL** All Digital Phase-Locked Loop, ciclo de fijación de fase completamente digital.

- **ASIC** Application Speficic Integrated Circuit, Circuito integrado para aplicaciones específicas.

- CIC Cascade Integrator Comb, integradores y peines en cascada.

- **CLB** *Configurable Logic Block*, bloque lógico configurable.

- CMC Canadian Microelectronic Corporation, Corporación Canadiense para la Microelectrónica.

- **CMOS** *Complementary Metal-Oxide-Semiconductor*, proceso metal-óxidosemiconductor complementario.

- **CPA** *Carry Propagate Adder*, sumador con propagación de acarreo.

**CPLD** Complex Programmable Logic Device, dispositivo lógico programable complejo.

**CRT** *Chinese Remanider Theorem*, teorema del resto chino.

**CSA** *Carry Save Adder*, sumador con ahorro de propagación de acarreo.

**CSE** *Clocked storage element*, elemento almacenador síncrono.

C<sup>2</sup>MOS Clocked CMOS Logic, lógica de sincronización con dispositivos CMOS.

**DCM** *Digital Clock Manager*, administrador digital de la señal de reloj.

**DCO** Digital Controlled Oscillator, oscilador controlado digitalmente.

**DLL** Delay-Locked Loop, ciclo de fijación de fase por retardo.

**DOE** Diffractive Optical Element, elemento óptico difractor.

**DSP** Digital Signal Processing, procesamiento digital de señales (también Digital Signal Processor, procesador digital de señales).

**DWT** Discrete Wavelets Transform, Transformada Discreta de Wavelets.

**EPLD** EPROM *technology-based Programable Logic Device*, Dispositivos Lógicos Programables basados en tecnología EPROM.

**EPROM** Erasable Programable Read Only Memory, Memoria de Solo Lectura Borrable y Programable.

**EEPROM** Electrically Erasable Programable Read Only Memory, Memoria de Solo Lectura Borrable y Programable Eléctricamente.

Abreviaturas y siglas xix

**FF** Flip-flop, biestable.

**FFT** Fast Fourier Transform, transformada rápida de Fourier.

**FIR** *Finite Impulsive Response*, respuesta a impluso finita.

**FPGA** *Field Programable Gate Array*, matriz de puertas programables.

**FPL** Field Programable Logic, Lógica programable.

**FSM** Finite-State Machine, máquina de estados finitos.

**GALS** Globally Asynchronous Locally Synchronous, globalmente asíncrono localmente síncrono.

**GQRNS** *Galois Enhanced QRNS*, QRNS mejorado mediante aritmética sobre cuerpos de Galois.

**HDL** *Hardware Description Language*, lenguaje de descripción de *hardware*.

**IP** Intellectual Property, propiedad intelectual.

**LFSR** *Linear Feedback Shift Register*, registro de desplazamiento con retroalimentación lineal.

**LSI** Large Scale of Integration, integración a gran escala.

**LUT** *Look-up table*, tabla de consulta.

**MOS** *Metal-Oxide-Semiconductor*, metal-óxido-semiconductor.

**MOSFET** *Metal-Oxide-Semiconductor Field Effect Transistor*, Transistor de Efecto Campo Metal Óxido Semiconductor.

**MRC** *Mixed Radix Conversion*, conversión por bases mixtas.

MSI Medium Scale of Integration, integración a media escala.

**MSL** *Master-slave latch*, elemento de almacenamiento síncrono controlado por nivel tipo maestro-esclavo.

**MCD** Máximo Común Divisor.

N-C<sup>2</sup>MOS *N-devices Clocked CMOS Logic*, lógica de sincronización CMOS con dispositivos de canal N.

**nETDFF** Negative Edge-Triggerd D Flip-Flop, biestable controlado por flanco de bajada.

**NMOS** *N-channel Complementary Metal-Oxide-Semiconductor*, proceso metal-óxido-semiconductor de canal N.

**NORA** *No Races*, sin carreras.

**NPTC** Non-Overlapping Pseudo Two Phase Clock, reloj de pseudo-dos fases no solapadas.

**PLL** *Phase-Locked Loop*, ciclo de fijación de fase.

**POD** *Point of Divergence*, punto de divergencia.

**QRNS** Quadratic Residue Number System, sistema numérico de residuos cuadrático.

**P-C<sup>2</sup>MOS** *P-devices Clocked CMOS Logic*, lógica de sincronización CMOS con dispositivos de canal P.

**PID** Proporcional, integral, diferencial.

Abreviaturas y siglas xxi

**PLD** *Programmable Logic Device*, dispositivo lógico programable.

**PMOS** *P-channel Complementary Metal-Oxide-Semiconductor*, proceso metal-óxido-semiconductor de canal P.

**RC** Resistive-Capacitive, resistivo-capacitivo.

**RDR** Red de Distribución del Reloj.

**RNS** Residue Number System, sistema numérico de residuos.

**ROA** *Rotary Oscillatos Array*, matriz de osciladores rotatorios.

**ROM** *Read Only Memory*, memoria de sólo lectura.

**RTWO** *Rotary traveling-wave oscillator*, oscilador rotatorio de ondas viajeras.

**SPDM** Single poly double metal, una capa de polisilicio y dos capas de metal.

**SPLD** Simple Programmable Logic Device, Dispositivo lógico programable simple.

**SRAM** Static Random Acces Memory, Memoria de Acceso Aleatorio Estática.

**SSI** *Small Scale of Integration*, integración a pequeña escala.

**SoC** System on chip, sistemas integrados en el mismo circuito integrado.

**SOI** *Silicon On Insulator*, silicio sobre aislante.

**SRNS** *Symmetric Residue Number System*, sistema numérico de residuos simétrico.

**TSPC** *True Single Phase Clock*, reloj de fase única.

VCO Voltage Controlled Oscillator, oscilador controlado por tensión.

**VHDL** Very High Speed Integrated Circuit Hardware Description Language, lenguaje de descripción de harware para circuitos integrados de alta velocidad.

**VLSI** *Very Large Scale of Integration*, muy alta escala de integración.

### **PRÓLOGO**

La sincronización es uno de los aspectos más importantes a considerar en el diseño de sistemas electrónicos VLSI (*Very Large Scale of Integration*), ya que las prestaciones y el rendimiento de un sistema dependen considerablemente de la exactitud y la calidad de la señal de reloj. Los últimos avances en la fabricación de circuitos integrados han tenido como consecuencia directa un notable incremento de los niveles de integración y de las velocidades de funcionamiento de los sistemas. Estos dos factores dificultan de forma extraordinaria la sincronización de los circuitos integrados. En los sistemas síncronos la señal de reloj controla el flujo de información a lo largo de todo el circuito, por lo tanto, la calidad de la misma repercute de forma crítica en el rendimiento del sistema.

La técnica de sincronización más frecuente en los sistemas digitales actuales es la denominada TSPC (*True Single Phase Clock*) [KAR88, AFG90], que consiste en transmitir una única señal de reloj a lo largo de todo el sistema de modo que todos los elementos síncronos sean activados simultáneamente por el flanco de dicha señal. Esto significa que una señal eléctrica debe ser transmitida de manera simultánea y con calidad aceptable por todo el circuito hasta cada módulo operativo. La señal de reloj es básicamente una señal de control y, como tal, es la que más distancia debe recorrer a lo largo del circuito y la que más rápidamente debe conmutar; de ahí que su generación y distribución sean un aspecto prioritario en el diseño de sistemas digitales.

Los problemas más comunes en la generación y distribución de la señal de reloj son el ruido, los retardos y la atenuación. Dichos problemas afectan a la calidad de la señal y al instante en que ésta conmuta, por lo que pueden causar una pérdida de sincronía en el sistema, o restricciones en la máxima frecuencia de reloj alcanzable debido a la necesidad de establecer márgenes de funcionamiento seguros. Por otro lado, el funcionamiento perfectamente síncrono de sistemas con un elevado número de dispositivos puede provocar problemas de distribución de corriente. La conmutación simultánea de gran cantidad de dispositivos requiere elevados niveles de corriente, de manera que es necesario el aumento del tamaño de las líneas de alimentación y el diseño de fuentes de alimentación capaces de suministrar rápidamente elevados niveles de corriente al sistema manteniendo contantes los niveles de referencia de tensión. El aumento del tamaño de las líneas de distribución de corriente provoca un incremento de las capacidades asociadas y, por lo tanto, del retardo producido y del consumo, mientras que el diseño de fuentes de alimentación más complejas complican y encarecen el diseño del sistema.

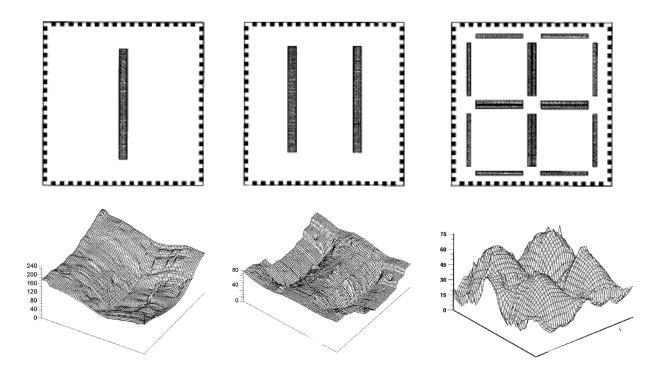

El principal objetivo de esta investigación es el estudio de una estrategia de sincronización para sistemas basados en el sistema numérico de residuos (RNS: *Residue Number System*) que distribuya varias señales de reloj ligeramente desfasadas a lo largo del periodo de la señal de reloj de referencia. Cada una de estas señales controlará cada uno de los canales de procesamiento de datos en los que se descomponen de forma natural los sistemas basados en el RNS. De esta manera se distribuye el funcionamiento del sistema, de modo que los valores máximos de corriente y el ritmo de crecimiento de dichas demandadas disminuyan significativamente, lo que permitirá el escalado de las líneas de alimentación del circuito integrado y la simplificación de las fuentes de alimentación. Al mismo tiempo, se eliminará la necesidad de transmitir una única señal de reloj perfectamente síncrona a lo largo de todo el sistema, con lo que se simplificará significativamente la labor de diseño de la red de distribución del reloj. Para llevar a cabo esta investigación se han realizado simulaciones eléctricas sobre sistemas realistas y también se han implementado sobre dispositivos lógicos programables.

La memoria este trabajo está estructurada en seis capítulos y tres apéndices, tal como se describe a continuación:

Prólogo xxv

#### CAPÍTULO 1. INTRODUCCIÓN

En el primer capítulo se introduce el problema de la sincronización de sistemas VLSI y se exponen las principales motivaciones para el desarrollo de este trabajo. Más concretamente se realiza una revisión histórica de la evolución del tamaño de los circuitos integrados, de la reducción del tamaño de los dispositivos y del aumento de la frecuencia de los sistemas digitales. Además, se plantean una serie de problemas derivados del aumento de la frecuencia y de las dimensiones de los sistemas digitales actuales. Para finalizar se plantea una estrategia de sincronización para sistemas basados en el RNS que aprovecha la modularidad de dichos sistemas.

### CAPÍTULO 2. FUNDAMENTOS DEL SISTEMA NÚMERICO DE RESIDUOS

En el segundo capítulo se realiza una revisión del RNS. En este capítulo se introducen los Sistemas Numéricos de Residuos y las operaciones más comunes en la aritmética de residuos. Además, se presentan algunas otras características del RNS, tales como la posibilidad de detección y corrección de errores, nociones sobre conversión, etc. También se describe la principal ventaja del RNS consistente en que es un sistema de representación numérica en el que cada número es representado por un conjunto de módulos de tal manera que las operaciones de suma, diferencia y producto de varios números se realizan de modo independiente en cada canal de procesamiento.

#### CAPÍTULO 3. SINCRONIZACIÓN EN CIRCUITOS DIGITALES VLSI

En el tercer capítulo se hace una revisión de diferentes métodos para la sincronización de circuitos digitales VLSI. Se analiza la propagación de la señal de reloj, así como su efecto en los elementos síncronos que componen un sistema. Se estudian los problemas que aparecen como consecuencia del aumento en tamaño, complejidad y velocidad de los circuitos integrados, así como los cada vez más exigentes requerimientos de fiabilidad. Adicionalmente, se presentan diferentes alternativas de sincronización que pretenden soslayar dichos problemas, al tiempo que pueden aumentar las prestaciones del sistema.

#### CAPÍTULO 4. NUEVA ESTRATEGIA DE SINCRONIZACIÓN

En este capítulo define, analiza y caracteriza una estrategia de sincronización basada en la aplicación de varias señales de reloj levemente desfasadas que controlan los diferentes canales que componen los sistemas basados en el RNS. Se compara esta estrategia de sincronización con la metodología de sincronización basada en una señal de reloj única, que es la más frecuente en la sincronización de sistemas digitales. Ambas estrategias se aplican a una serie de sistemas de prueba y se analiza el efecto de la aplicación de las señales desfasadas, sobre las demandas de corriente y el consumo de los sistemas.

#### CAPÍTULO 5. APLICACIÓN EN SISTEMAS PROGRAMAMBLES

En el capítulo quinto se implementa un sistema basado en el RNS sobre un dispositivo lógico programable FPGA (*Field Programable Gate Array*) protegido mediante una firma digital. Se estudia el efecto de la aplicación de la nueva estrategia de sincronización sobre el consumo de un sistema real en contraste con el sistema sincronizado mediante una única señal de reloj. Además se va a estudiar el efecto de la aplicación de varias señales desfasadas en las diferencias entre los modos de funcionamiento normal y de extracción de la firma con las dos metodologías de protección analizadas.

#### CAPÍTULO 6. CONCLUSIONES

Por último, el capítulo sexto contiene las conclusiones obtenidas y una valoración crítica de los resultados. Se recogen las aportaciones de esta memoria y se sugieren nuevas líneas de trabajo.

A final de la memoria se añaden tres apéndices con los siguientes contenidos:

#### APÉNDICE A. GENERACIÓN DE LA SEÑAL DE RELOJ

En el primer apéndice se analiza la generación de las señales de reloj así como los diferentes métodos para acondicionar la señal de reloj de referencia dentro del chip. Se estudian diversas configuraciones para conseguir la sincronización entre la señal de reloj externa y la interna, y la multiplicación de frecuencia dentro del chip.

Prólogo xxvii

# APÉNDICE B. ANÁLISIS DE LOS DISPOSITIVOS Y MÓDULOS USADOS EN LAS SIMULACIONES

En el segundo apéndice se detallan los dispositivos y circuitos empleados en las simulaciones eléctricas y se justifican algunas decisiones de diseño en cuanto al dimensionado de dispositivos. Además se describe en detalle la arquitectura y funcionamiento de las memorias ROM que se han usado asiduamente en los sistemas simulados.

# APÉDICE C. PROGRAMA GENERADOR DE LIBRERÍAS DE MEMORIAS ROM

En el último apéndice se describe un programa desarrollado para este trabajo para la implementación de las memorias ROM, usadas en el diseño de los sistemas simulados, a partir de la descripción de la memoria y de los datos contenidos en las mismas.

Como finalización de este prólogo se van a dar algunas indicaciones para facilitar la lectura de esta memoria:

- la memoria está estructurada en capítulos y éstos se organizan en diferentes secciones y éstas en apartados y subapartados, que se numeran con varios dígitos. El primer dígito hace referencia al capítulo y los posteriores a la sección y diferentes apartados en el orden de inclusión en que van apareciendo. Ejemplo 4.5.2.3;

- las figuras y tablas se numeran con dos números, el primero hace referencia al

capítulo y el segundo al orden de aparición dentro del capítulo. Además la

memoria incluye índices de tablas y figuras para facilitar la búsqueda concreta

de alguno de estos elementos. Ejemplo: Tabla 4.6, Figura 5.2;

- las expresiones matemáticas y ecuaciones se referencian de modo similar a las tablas y las figuras con dos números entre paréntesis, que representan el capítulo y al orden de aparición dentro del mismo. Ejemplo (2.1);

Por último las referencias bibliográficas se designan entre corchetes con tres letras, correspondientes al apellido del primer autor y dos números relativos al año de publicación. En el caso de coincidencia en la denominación de las referencias se incluirá una letra al final. Las referencias se hallan ordenadas alfabéticamente al final de la memoria. Ejemplos [GAR99], [CAS07], [GON02a].

# **CAPÍTULO 1**

# INTRODUCCIÓN

En este primer capítulo se exponen las principales motivaciones que justifican la realización de esta tesis. Se realiza un estudio preliminar sobre la evolución de las características y prestaciones de los sistemas digitales y se comentan las dificultades que surgen durante el diseño de sistemas cada vez más extensos que funcionan a frecuencias cada vez mayores. Después se hace una breve introducción a la evolución de diferentes metodologías de sincronización y se propone una estrategia alternativa consistente en la aplicación de varias señales de reloj ligeramente desfasadas. También se hace una breve reseña al sistema numérico de residuos (RNS: *Residue Number System*), cuyas características motivaron su elección como base de los sistemas analizados durante el desarrollo de este trabajo.

# 1.1. Evolución y estado actual de las prestaciones en sistemas digitales

Desde el inicio de la fabricación de dispositivos integrados la tendencia dominante ha sido la disminución del tamaño de los transistores y el incremento en los niveles de integración de los circuitos y, como consecuencia, un aumento de la frecuencia de funcionamiento y la cantidad de dispositivos incluidos en un mismo circuito integrado. En 1965 Moore escribió un artículo [MOO65] en el que afirmaba: "La complejidad de los componentes se ha multiplicado aproximadamente por 2 cada año. A corto plazo, se puede esperar que esta tasa se mantenga, o incluso que aumente. A largo plazo, la tasa de aumento es un poco más incierta, aunque no hay razón para creer que no permanecerá constante por lo menos durante 10 años. Esto significa que para 1975, el número de componentes en cada circuito integrado de mínimo coste será de 65.000. Creo que un circuito tan grande puede construirse en una sola oblea". La predicción de Moore, enunciada tres años antes de la aparición del microprocesador, se mantuvo hasta principios de los 70; a mediados de esa misma década se constató que dicho ritmo había

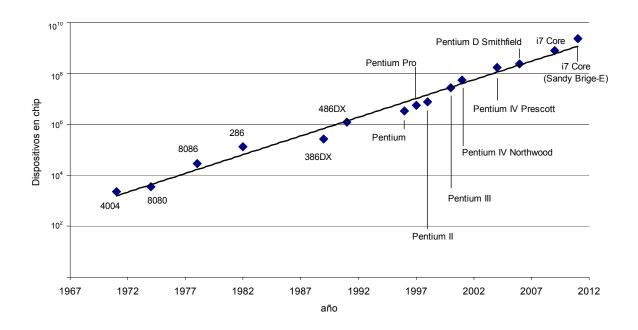

Figura 1.1. Evolución del número de dispositivos integrados en un solo microprocesador.

Capítulo 1. Introducción

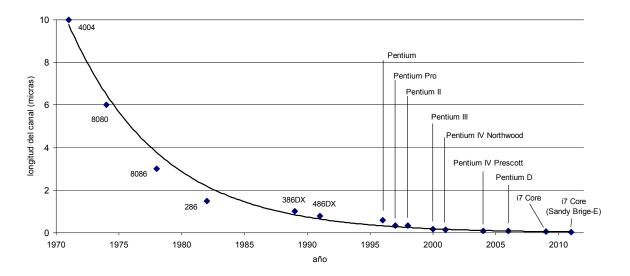

disminuido hasta ser necesarios aproximadamente dos años para que se duplicase el número de componentes en un sólo chip. Esta tendencia, conocida como Ley de Moore, se ha mantenido vigente hasta la actualidad, tal como se puede apreciar en la Figura 1.1, que muestra la evolución del número de dispositivos integrados en un solo chip de diferentes microprocesadores de los últimos 40 años. Este incremento está directamente relacionado con la disminución del tamaño característico de los dispositivos del chip. En la Figura 1.2 se representa la evolución de la longitud del canal de los transistores y se puede apreciar la tendencia exponencial de disminución de la misma. Los últimos valores de la gráfica muestran que el estado actual de la tecnología permite la fabricación de dispositivos con una longitud de canal de 32nm. A modo de ilustración sobre la evolución de la tecnología en la fabricación de dispositivos integrados se podría comparar el primer PC, el Altair computer de Intel producido en 1974, que incorporaba el microprocesador 8080 con 6.000 transistores implementados con una tecnología de 6µm capaz de funcionar a 2MHz, con el procesador de Intel i7-390X Processor Extreme Edition (Sandy Bridge-E) (2011) de séxtuple núcleo, con capacidad de 12 procesos en paralelo, que contiene 2.270 millones de transistores fabricados mediante un proceso de 32nm, con una frecuencia de funcionamiento de 3.30GHz capaz de alcanzar los 3.90GHz en modo turbo. Otros ejemplos del impresionante desarrollo de la industria electrónica hasta el momento son el hecho de que desde el año 2004 el sector de los semiconductores produce más transistores (y a un menor coste) que granos de arroz en todo el mundo, según la Asociación del Sector de Semiconductores de los Estados

Figura 1.2. Evolución del tamaño característico de los transistores.

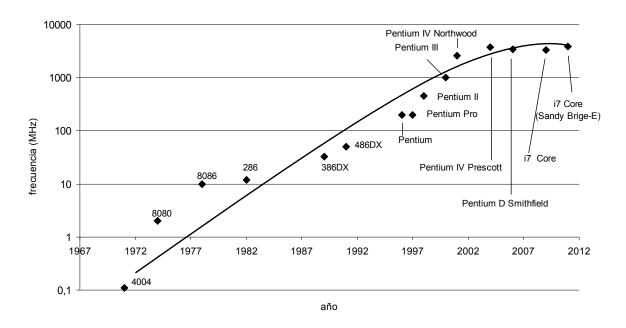

Figura 1.3. Evolución de la frecuencia de funcionamiento de microprocesadores.

Unidos (*U.S. Semiconductor Industry Association*), o que si el desarrollo de la industria aeronáutica hubiera sido similar al de los semiconductores, actualmente se podría viajar de Nueva York a París por un céntimo de euro y en menos de un segundo.

De seguir la progresión marcada por la ley de Moore en el año 2012 deberían existir chips de 10 GHz con 2.000 millones de transistores. Sin embargo, el mercado del microprocesador comercial se ha estancado en frecuencias de reloj de en torno a 4GHz; la disipación térmica de cientos de millones de transistores a tan elevadas frecuencias es muy complicada y los efectos capacitivos, inductivos y de emisión electromagnética cobran una mayor relevancia complicando extraordinariamente el diseño de circuitos integrados. La figura 1.3 muestra la evolución de la frecuencia de funcionamiento de los microprocesadores de los últimos 40 años. La alternativa actual parece dirigir sus esfuerzos hacia sistemas multiprocesador. En el primer tercio del año 2005 se comenzaron a comercializar los sistemas biprocesador. Los *Pentium Dual-Core* de Intel y los *Athlon X2* de AMD abrieron el camino a sus inmediatos sucesores: los procesadores *Core 2 Duo* de Intel, optimizados y capaces de un mayor rendimiento incluso a frecuencias inferiores (2.4GHz en la primera mitad de 2007). Actualmente se han desarrollado los procesadores de séxtuple núcleo, *i7 core Sandy Bridge-E* de Intel y el procesador *AMD FX 8150 Black Edition* de óctuple núcleo capaz de alcanzar los

Capítulo 1. Introducción

4.2GHz de AMD. La conclusión es que se ha alcanzado un límite rentable en la frecuencia del reloj de los microprocesadores y los diseñadores incrementan la capacidad de procesamiento mejorando la arquitectura y aprovechando las ventajas del procesamiento paralelo. En sistemas supercomputador se ha producido la misma situación. Los supercomputadores más potentes, dedicados bien a la atención de múltiples usuarios o al cálculo masivo (meteorología, aeronáutica, prospección minera y petrolífera, etc.) mejoran su rendimiento mediante la paralelización masiva de microprocesadores. Como ejemplo, el supercomputador *Roadrunner* de IBM que funciona con de 12.240 procesadores *PowerXCell 8i* en paralelo y 6.912 procesadores *Opteron* de AMD de doble núcleo conectados mediante 92 km de fibra óptica y está diseñado para realizar alrededor de 1.7 petaFlops (*peta Floating-point Operations Per Second*, 10<sup>15</sup> operaciones en punto flotante por segundo) con un consumo de 3 megawatios.

# 1.2. Problemática en la sincronización de circuitos VLSI

La disminución del tamaño característico de los transistores que forman los circuitos integrados actuales ha sido la causa del gran incremento tanto en el nivel de integración de los sistemas electrónicos como en la velocidad de operación de los mismos. La combinación de estos dos factores lleva a la implementación de sistemas VLSI (*Very Large Scale of Integration*) mayores, más complejos y más rápidos, lo que se traduce en que la influencia de una serie de efectos, hasta ahora de segundo orden, se haga más significativa. La espectacular disminución en el tamaño de los dispositivos y del periodo de la señal de reloj no se ha producido de manera proporcional en el error asociado a retardos, ruido o variaciones de proceso. A medida que los tiempos de conmutación se reducen al rango de los nanosegundos (y por lo tanto las frecuencias se incrementan hasta los GHz), las líneas de distribución de las diferentes señales comienzan a presentar efectos inductivos [KAR10, MAH06, ZHO91] que atenúan y retardan de manera apreciable la propagación de dichas señales. El incremento de la frecuencia de la señal de reloj tiene como resultado que se deban propagar componentes de alta frecuencia que sufren mayor atenuación, por lo que la señal de reloj se degrada, pasando

de un perfil abrupto a otro más suave. Este perfil suavizado es la causa de dos problemas de importancia capital a los que los diseñadores dedican gran parte de tiempo y recursos. Por un lado se producen incertidumbres en el instante que conmutan las señales, con lo que no se sabe con exactitud en momento en el que los sistemas cambian de estado. A medida que la frecuencia de funcionamiento aumenta se hace más significativa dicha incertidumbre frente al periodo del reloj. En el Capítulo 3 se abundará en esta cuestión y en dos de los principales efectos que esto provoca: el *skew* y el *jitter*. Por otro lado, se produce un incremento del consumo dinámico ya que, en la tecnología CMOS, los dispositivos conducen únicamente durante la fase de conmutación. Otro problema derivado de los altos niveles de integración y, consecuentemente del aumento en el número de dispositivos, es el brusco incremento de las demandas de corriente de las fuentes de alimentación en instantes muy concretos. Esto provoca variaciones en las tensiones de alimentación de los sistemas con el consiguiente aumento de las incertidumbres en la señal de reloj.

De modo general se puede asumir que la señal más crítica en una sistema digital síncrono es la señal de reloj; es la que se debe propagar a lo largo de más dispositivos, debe llegar a todos los módulos operativos del sistema y, por lo tanto, ha de propagarse a través de largas líneas de interconexión, es la señal que más rápidamente debe conmutar y su calidad determina el funcionamiento del resto del sistema. En sistemas digitales de altas prestaciones el consumo asociado a la distribución de la señal de reloj puede alcanzar hasta el 60% del consumo total del chip, por lo que se debe poner especial énfasis en el diseño de la red de distribución de la señal de reloj.

Algunos de los problemas de mayor relevancia, y que más pueden afectar al rendimiento de los sistemas, relacionados con la generación y distribución de la señal de reloj son los siguientes:

- dificultad para que una única señal de reloj se transmita y actúe de forma simultánea en todos los módulos de un circuito extenso o con elevados requerimientos de velocidad (*skew*) [NIC12, KIM10, ESM10, KHL04, CEL99, KEE91, AFG90, YUA89];

- retardo en la propagación de la señal de reloj a lo largo de una línea,

Capítulo 1. Introducción

ocasionado por aumento del tamaño de los circuitos integrados junto con el incremento de la frecuencia de operación, que provoca la limitación de la velocidad de funcionamiento global [MOH11, HIG11, CEL99, ZHO91];

- dispersión en el periodo de la señal de reloj (*clock jitter*), ocasionado por efectos de ruido que se hacen más significativos cuando disminuyen las corrientes de funcionamiento y el periodo [JAN12, SHI10, JIA10, YAM01, HEY00, HER99];

- la demanda de corriente puede alcanzar niveles elevados en determinados instantes muy concretos, mientras que en el resto del tiempo el consumo es sensiblemente más bajo. Esto es consecuencia del funcionamiento síncrono, que requiere que las diferentes partes del circuito funcionen simultáneamente [SOM11, BHA98];

- la necesidad de conducir corrientes elevadas supone el uso de líneas de interconexión de gran sección, que a su vez implican grandes capacidades que ralentizan la carga y descarga de dichas líneas, producen efectos de acoplamiento entre líneas y ocupan grandes áreas [KAR10, BAI04, LEE98];

- aparición de efectos inductivos en las interconexiones debido al incremento de las frecuencias de funcionamiento, con la consiguiente degradación en el perfil de la señal de reloj y la aparición de señales reflejadas en las interconexiones [KAR10, MAH06, ZHO91].

La falta de sincronía entre diferentes módulos del sistema (*skew*) se produce cuando el tiempo de respuesta de los módulos de proceso se hace comparable a las diferencias entre los retardos de la señal en cada ruta de distribución, de tal forma que la señal de reloj adquiere valores sensiblemente diferentes en distintas partes del circuito en un mismo instante. Este efecto se hace relevante en circuitos de gran tamaño y con frecuencias de funcionamiento elevadas. Una estrategia para la reducción del *skew* en un circuito requiere el uso de la teoría de estructuras RC en árbol (*RC-trees*), consistente en modelar las líneas de distribución como una estructura ramificada en la que cada

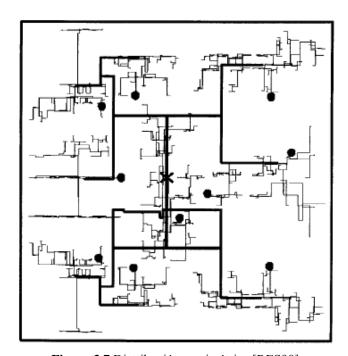

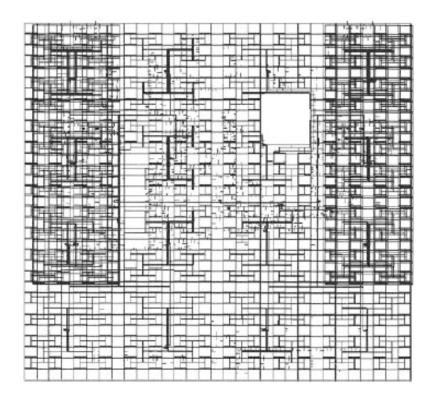

línea de distribución es una asociación de una resistencia y una capacidad, y cada módulo operativo una capacidad terminal [RAM94]. El análisis del sistema de distribución según su modelo RC permite calcular el retardo a lo largo de cada línea y, de esta manera, establecer una distribución de los módulos operativos y elementos de retardo adicionales, de forma que el retardo en la distribución de reloj sea lo más similar posible a lo largo de las diferentes líneas de distribución. Éste es un método de resolución de peor caso, ya que conduce a realizaciones seguras pero implica un aumento en el periodo del reloj como consecuencia de la inclusión de buffers cuya única finalidad es producir un retardo adicional en una ruta para igualarla al resto [RAM94]. Una alternativa consiste en realizar una aproximación estadística que proporciona situaciones en las que la probabilidad de error es muy pequeña, pero no nula, y produce periodos de reloj menores [JIA01]. Otros enfoques distribuyen los módulos operativos de forma simétrica (en forma de H o X, H-trees o X-trees, respectivamente), de manera que las señales de reloj sufran los mismos retardos en todos los caminos [FRI01]. Estos métodos tienden a igualar el retardo a lo largo de las diferentes líneas de distribución del reloj evitando diferencias en la sincronía, pero no resuelven el problema del retardo global del sistema y acentúan el problema del consumo de potencia, ya que, en definitiva, como resultado los módulos funcionan al mismo tiempo, haciendo que la demanda de corriente en determinados instantes se incremente.

# 1.3. Estrategias de sincronización de sistemas VLSI

Existen dos metodologías diferentes de sincronización en los sistemas VLSI, dependiendo de si los elementos de memoria están controlados por nivel (*latches* o cerrojos) o por flanco (*flip-flops*). En los sistemas controlados por nivel, los bloques combinacionales que realizan el procesamiento de los datos están separados por estructuras que pueden estar en dos estados dependiendo del nivel (alto o bajo) de la señal de reloj. En estado abierto, se establece conexión (y por lo tanto transferencia de datos) entre los bloques y, en el estado cerrado, se bloquea el paso de datos aislando una etapa de la otra. En los sistemas gobernados por flanco los elementos de memoria son biestables del tipo D que transfieren el valor de la entrada al de la salida cuando ocurre un flanco en la señal de reloj.

Capítulo 1. Introducción

Los sistemas sincronizados por nivel son más rápidos y requieren menos recursos hardware, pero su funcionamiento es más complicado y su optimización más compleja. Por otro lado los sistemas controlados por flanco tienen un funcionamiento menos complejo y se pueden optimizar de forma más sencilla, pero son más lentos y requieren más dispositivos.

Los sistemas controlados por nivel se pueden sincronizar utilizando diferentes estrategias que pueden requerir el uso de una o más señales de reloj. Una de las primeras estrategias de sincronización en este tipo de sistemas fue la NPTC (Non-overlapping Pseudo Two Phase Clock) [YUA89] que requiere la distribución de cuatro señales de reloj no solapadas. Los recursos necesarios y la condición necesaria de no-solapamiento tienen como consecuencia fuertes restricciones en cuanto a la calidad de las señales y los límites permisibles de skew y retardo. En este mismo tipo de sistemas la técnica de sincronización NORA (No Race) [GON83] simplificaba la labor de diseño limitando a dos las señales necesarias (señal de reloj y complementaria), pero seguía presentando la dificultad de tener que distribuir dos señales de reloj. Por último la metodología TSPC (True Single Phase Clock) [KAR88, AFG90] sólo necesita de una única señal de reloj y es actualmente la técnica de sincronización en uso. Esta técnica es la más adecuada en los sistemas controlados por flanco, ya que lo único que se necesita de la señal que controla el sistema es su cambio de nivel, es decir, su flanco. En el tercer capítulo se analizan las técnicas de distribución de reloj basadas en TSPC más frecuentes en la actualidad.

Todas las metodologías de sincronización son en una u otra medida sensibles a los mismos problemas. Las estrategias que requerían más señales de reloj eran más vulnerables al *skew* y al *clock jitter*; la técnica TSPC presenta mejor comportamiento frente al *skew*, pero éste se vuelve a hacer patente a medida que aumenta la frecuencia de funcionamiento. En lo concerniente a esta memoria, se empleará un sistema controlado por flanco de bajada, y por lo tanto se aplicará una única señal de reloj en la que se inducirá un *skew* controlado para aplicar diferentes señales levemente desfasadas a los diferentes canales que formarán el sistema analizado.

# 1.4. Nueva estrategia de sincronización

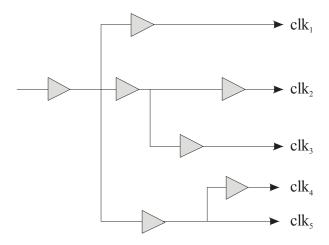

Como alternativa a los circuitos con una única señal de reloj se ha propuesto [GAR99] una estructura que a partir de una única señal de reloj genera otras señales ligeramente desfasadas respecto de la original. Cada una de estas señales controla diferentes partes del circuito de forma que éstas funcionan en diferentes instantes, dentro del mismo ciclo de reloj, distribuyéndose de esta manera el consumo y reduciéndose los picos de corriente. Esta estrategia también elimina la necesidad de una sincronía global. El análisis detallado de las restricciones que deben cumplir las señales, de su diseño, de los circuitos que las generan y los resultados de su aplicación a sistemas concretos se realizará en el capítulo cuarto.

La idea de usar una señal levemente desfasada (como consecuencia del *skew*) para mejorar el rendimiento de los sistemas, aparece en la bibliografía en diversos trabajos [FISH90, FRI93, FRI01]. En concreto, se plantea la posibilidad de disminuir el periodo de funcionamiento y, consecuentemente, aumentar la frecuencia, haciendo llegar a registros adyacentes señales desfasadas (la más retrasada al primero de ellos). La aplicación de esta estrategia está limitada por la aparición del problema de carreras si el desfase resulta ser superior al tiempo necesario para realizar el proceso de los datos tal como se analizará en el tercer capítulo. Otros autores han propuesto sistemas que producen un *skew* sobre una única señal para conseguir un funcionamiento distribuido [YOO99] y limitar los valores de pico de las corrientes [BEN96]. Posteriormente se ha propuesto [GAR99] la generación de diferentes señales levemente desfasadas para controlar diferentes canales en un sistema basado en el RNS. En esta memoria se parte de esta última idea y se aplica y analizan los resultados sobre varios sistemas, un filtro CIC para diezmado de Hogenauer, un controlador PID y un sistema para el cálculo de la transformada *wavelet* 1D-DWT por transformación al dominio de los índices.

Para poder aplicar varias señales de reloj en un circuito digital es necesario que el diseño permita el funcionamiento paralelo e independiente de módulos diferentes. De esta manera, tan sólo es necesario que los datos estén disponibles de forma síncrona a la salida. Los circuitos de cálculo basados en el Sistema Numérico de los Residuos cumplen con esta característica. Una característica del RNS [SZA67] es que en las operaciones de suma no existe un acarreo que se transmita de un residuo a otro, por lo

Capítulo 1. Introducción

que el sistema consta de una serie de canales que pueden operar de forma independiente. El RNS es un sistema de representación numérica muy eficaz en el cálculo de sumas y productos, pero presenta dificultades en operaciones de división, comparación y detección de signo, y desbordamiento, por lo que el uso de esta alternativa queda restringido a sistemas en los que sea necesario calcular gran cantidad de sumas y productos. Sin embargo, existen multitud de aplicaciones en las que estas limitaciones no son un obstáculo, entre las que se incluyen la transformada rápida de Fourier (FFT: Fast Fourier Transform) y otras transformadas discretas y, en general, la mayoría de aplicaciones de procesamiento digital de señales (DSP: Digital Signal Processing).

Es objetivo de este trabajo profundizar más en las posibilidades y características de esta nueva estrategia de sincronización, así como comprobar su comportamiento en sistemas reales.

### 1.5. Conclusión

En este capítulo se han planteado las diferentes técnicas que se han usado hasta el momento para sincronizar sistemas VLSI y se han sugerido los principales problemas que pueden surgir en la sincronización de circuitos extensos que operan a elevadas frecuencias de reloj. Se ha comentado una estrategia de sincronización para sistemas controlados por flanco, consistente en generar diferentes señales de reloj desfasadas entre sí de manera que cada señal controla una parte del circuito. La plena aplicación de esta técnica requiere sistemas cuyo funcionamiento se pueda separar en diferentes módulos o canales independientes entre sí, de forma que cada canal esté gobernado por una de estas señales desfasadas. Los sistemas basados en el RNS presentan esta característica, por lo que serán un campo más que adecuado para la aplicación de la estrategia en estudio.

# **CAPÍTULO 2**

# FUNDAMENTOS DEL SISTEMA NUMÉRICO DE RESIDUOS

En este capítulo se introduccen los Sistemas Numéricos de Residuos y las operaciones más comunes en la aritmética de residuos, tales como suma, resta, multiplicación y escalado. Además, se presentan algunas otras características del RNS, tales como la posibilidad de detección y corrección de errores, nociones sobre conversión, etc. También se describe la principal ventaja del RNS consistente en que es un sistema de representación numérica en el que cada número es representado por un conjunto de módulos de tal manera que las operaciones de suma, diferencia y producto de varios números no implica la propagación de acarreo entre los diferentes módulos que representan a cada uno de los números, con lo que dichas las operaciones se resuelven en paralelo para cada canal de manera independiente.

## 2.1. Los Sistemas Numéricos de Residuos

Los sistemas numéricos usuales son lineales, posicionales y pesados, es decir, el valor de cada dígito depende de la posición que ocupe. Los sistemas basados en el RNS, en cambio, parten de un conjunto de bases previamente establecidas y cada número queda representado por el conjunto de residuos en dichas bases, esto es, los restos de las divisiones enteras de dicho número entre cada una de las bases que definen el sistema numérico. Cada número queda unívocamente representado por el conjunto de sus residuos siempre que sea menor que el producto de las bases tal y como establece el Teorema del Resto Chino (CRT: *Chinese Remainder Theorem*) [TAY84, SOD86].

**Teorema 2.1.** Considérese el conjunto de módulos  $\{m_1, m_2, ..., m_n\}$  todos ellos primos relativos entre sí. Cualquier número X tal que X < M siendo:

$$M = \prod_{i=1}^{n} m_i \tag{2.1}$$

tiene una representación única dada por  $X = [x_{1,}x_{2},...,x_{n}]$  donde:

$$x_i = X \bmod m_i \tag{2.2}$$

**Demostración**. Supóngase que existen dos números X e Y que tengan la misma representación en residuos, es decir,  $x_i = y_i$  para todo i, siendo:

$$x_i = X \mod m_i$$

$$y_i = Y \mod m_i$$

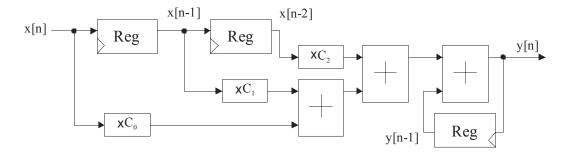

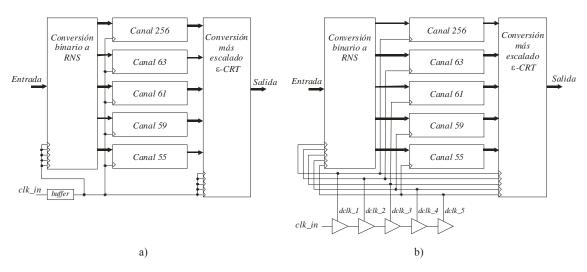

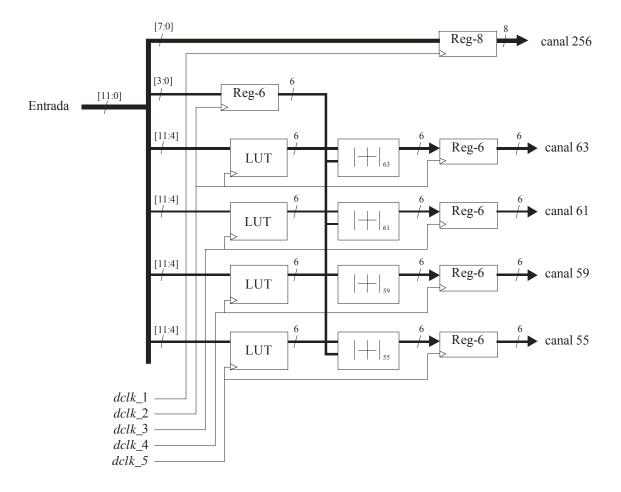

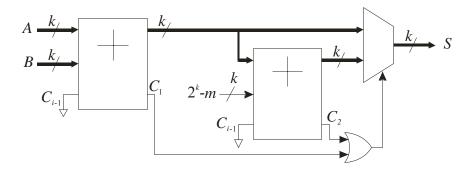

Entonces se cumple que X-Y debe ser múltiplo de cada  $m_i$  y, por lo tanto, también del mínimo común múltiplo de los  $m_i$ . Como los  $m_i$  son primos entre sí, su mínimo común múltiplo es M y al ser X-Y múltiplo de M, no pueden ser ambos simultáneamente mayores que M.