## UNIVERSIDAD DE GRANADA $\text{AND} \\ \text{INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE}$

Departamento de Electrónica y Tecnología de Computadores and Institut de Microélectronique, Électromagnétisme et Photonique

# CHARACTERIZATION, MODELLING AND SIMULATION OF DECANANOMETER SOI MOSFETs

Doctoral Thesis

Noel Rodríguez Santiago

Granada-Grenoble 2008

Editor: Editorial de la Universidad de Granada Autor: Noel Rodríguez Santiago D.L.: Gr. 706 - 2008 ISBN: 978-84-338-4932-8

**Dr. Francisco J. Gámiz Pérez**, Professor of Electronics at the Departamento de Electrónica y Tecnología de Computadores of the Universidad de Granada in Spain, and **Dr. Sorin Cristoloveanu**, Director of Research at the Centre National de la Recherche Scientifique in France.

#### **CERTIFY:**

that the research work contained in the present report, entitled *Characterization, Modelling and Simulation of Decananometer SOI MOSFETs*, and presented by **Mr. Noel Rodriguez Santiago** to obtain the Doctor Degree by the Universidad de Granada and the Institut National Polytechnique de Grenoble with the *Doctor Europeus* mention, has been made under our full supervision at the Departamento de Electrónica y Tecnología de Computadores of the Universidad de Granada and the Institut de Microélectronique, Électromagnétisme et Photonique of the Institut National Polytechnique de Grenoble.

Granada,  $10^{th}$  of December, 2007

Prof. Dr. Francisco J. Gámiz Pérez Professor of Electronics UGR Prof. Dr. Sorin Cristoloveanu Director of Research CNRS

$To\ my\ parents,\ brother$   $and...\ future\ girl\ friends$

I never paint dreams or nightmares, I paint my own reality.

Frida Kahlo (1907-1953)

#### Acknowledgements

I would like to have a special thought for those people that in one way or another have contributed to carry out this work.

First, I would like to thank my advisors, Prof. Francisco J. Gámiz Pérez and Prof. Sorin Cristoloveanu, for all the support, encouragements, assistance and patience. Despite being really busy, they always found time for me to discuss research and other non-technical deliberations day by day, holding out a hand every time I needed it. I will always adore their innovative thinking. Thanks for embarking with me on this journey.

I would like to express my gratitude to the committee of this thesis: Dr. Carlos Mazuré, Prof. Jean Pierre Colinge, Dr. Olivier Faynot and Prof. Cor Claeys. I am honored by their participation and expert judgement.

This work could not have been completed without the support of the heads of the Departamento de Electrónica y Tecnología de Computadores and the Institut de Microélectronique, Électromagnétisme et Photonique during my research. I would like to thank Professors Juan Enrique Carceller Beltrán and Pedro Cartujo Estébanez from Granada and Professors Gérard Ghibaudo and Francis Balestra from Grenoble.

I would like to deeply thank the members of my research group at the Universidad de Granada, Dr. Juan B. Roldán Aranda, Dr. Andrés Godoy Medina (thanks for the thorough corrections), Dr. Pedro Cartujo Cassinello, Dr. Francisco Jiménez Molinos, Dr. Carlos Sampedro Matarín who contributed to the edition of this document, Dr. Luca Donetti, Dr. Francisco J. García Ruiz, Dr. Isabel Tienda Luna,

Miss María Balaguer Jiménez who generously helped me with the translations into French, Mr. Francisco Martínez Carricondo and all the members of the Department of Electronics.

Many thanks to Prof. Juan Antonio López Villanueva, for all the useful discussions.

I am deeply indebted to the members of the Institut de Microélectronique, Électromagnétisme et Photonique. I appreciate the efforts of Dr. Raphaël Clerc. I will always be grateful to Dr. Leily Zafari and Miss Wipa Chaisantikulwat for all the aid they gave me. I would like to strongly thank Miss Loan Pham Nguyen for all her support and being an excellent scientific colleague. Thanks to Mr. Tuan Nguyen for experimental data.

My collaboration with  $Soitec^{TM}$  engineers and scientists was very appreciated (Dr. F. Allibert, Dr. F. Brunier, Dr. N. Bresson, Miss G. Hamaide).

I wish to place on record the valuable assistance rendered by administrative officers Dalhila Alouani and Valérie Miscioscia.

A great deal of thanks goes to several people that have played a decisive role during my stay in Grenoble: Dr. Ana Romero, Miss Carmen Gailan, Dr. Sandra Rocha and, I cannot find words to express my acknowledgement to Miss Janelle Sánchez, Miss Pilar García and Miss Mónica López.

I am grateful to the European Commission for the Marie Curie Project EDITH (EST 504195).

Loving thanks to my parents, brother and friends. Without their support and motivation, my achievements would have been incomplete. I would like to mention María J. Ramírez, Zoraida Callejas (never enough thanks for helping me with the figure captions), Ana B. Fernández, María G. Vallejo, Dr. Darine Kaddour, Hamza Issa, Santiago Rodríguez, Daniel Castro, Alejandro Torres and also in the distance, Claudia Moreno.

## Contents

| Li | st of         | Figures                                                          | V    |

|----|---------------|------------------------------------------------------------------|------|

| A  | bbre          | viations and acronisms                                           | xix  |

| P  | rolog         | rue x                                                            | xiii |

| Ι  | $\mathbf{TH}$ | IE ULTIMATE MOSFET TECHNOLOGY                                    | 1    |

| 1  | MO            | OSFET quantum simulation                                         | 3    |

|    | 1.1           | Introduction: The Schrödinger equation                           | 3    |

|    | 1.2           | Effective-mass approximation for arbitrarily oriented MOSFETs    | 5    |

|    | 1.3           | Poisson-Schrödinger Self-Consistent solver                       | 8    |

|    | 1.4           | Conclusions                                                      | 11   |

| 2  | Cry           | stallographic orientation influence on static properties         | 13   |

|    | 2.1           | Introduction                                                     | 13   |

|    | 2.2           | Inversion layer centroid model                                   | 22   |

|    | 2.3           | Polysilicon depletion effect                                     | 29   |

|    | 2.4           | Gate-to-channel capacitance modelling                            | 32   |

|    | 2.5           | Conclusions                                                      | 35   |

| 3  | Acc           | cumulated carrier quantization and its effects on silicide-gated |      |

|    | MO            | OSFET                                                            | 37   |

|    | 3.1           | Introduction                                                     | 37   |

|    | 3.2 | Higher polysilicon doping                                   | 38         |

|----|-----|-------------------------------------------------------------|------------|

|    | 3.3 | The role of the majority carriers                           | 42         |

|    | 3.4 | Flat-band voltage shift                                     | 42         |

|    | 3.5 | Conclusions                                                 | 46         |

| 4  | Ren | note scattering mechanisms in ultra-thin-gate-oxide MOSFETs | 47         |

|    | 4.1 | Introduction                                                | 47         |

|    | 4.2 | Simulator description                                       | 49         |

|    | 4.3 | Remote scattering model                                     | 51         |

|    | 4.4 | Comparison with experimental results                        | 58         |

|    | 4.5 | Conclusions                                                 | 59         |

|    |     |                                                             |            |

| II | TI  | HE SOI PARADIGM                                             | 61         |

| 5  | SOI | technology                                                  | 63         |

|    | 5.1 | SOI technology motivation                                   | 64         |

|    | 5.2 | SOI wafers fabrication                                      | 66         |

|    |     | 5.2.1 SIMOX                                                 | 66         |

|    |     | 5.2.2 ELTRAN $^{\textcircled{R}}$                           | 68         |

|    |     | 5.2.3 Smart-CUT <sup><math>TM</math></sup>                  | 69         |

|    | 5.3 | Advantages of the SOI technology                            | 71         |

|    | 5.4 | SOI devices classification                                  | 72         |

|    |     | 5.4.1 Partially depleted MOSFETs                            | 72         |

|    |     | 5.4.2 Fully depleted MOSFETs                                | 72         |

|    |     | 5.4.3 Multigate devices                                     | 73         |

|    |     | 5.4.4 Non-conventional effects                              | 75         |

|    | 5.5 | Conclusions                                                 | 77         |

| 6  | SOI | wafers characterization                                     | <b>7</b> 9 |

|    | 6.1 | Introduction                                                | 79         |

|    | 6.2 | Second Harmonic Generation in $\Psi$ -MOS                   | 79         |

|    | 6.3 | Pseudo-MOSFET                                               | 82         |

|    |     | 6.3.1 Threshold voltage shift                               | 83         |

|   |     | 6.3.2    | Vertical potential profile                                      | 86  |

|---|-----|----------|-----------------------------------------------------------------|-----|

|   |     | 6.3.3    | Analytical model for the threshold voltage                      | 88  |

|   |     | 6.3.4    | Empirical model for the threshold voltage                       | 93  |

|   | 6.4 | Concl    | usions                                                          | 94  |

| 7 | Mo  | bility 6 | extraction for SOI transistors                                  | 95  |

|   | 7.1 | Introd   | luction                                                         | 95  |

|   | 7.2 | Chara    | cterization techniques                                          | 95  |

|   |     | 7.2.1    | Threshold voltage                                               | 96  |

|   | 7.3 | Mobil    | ity extraction                                                  | 99  |

|   |     | 7.3.1    | Transconductance peak                                           | 100 |

|   |     | 7.3.2    | Split-CV                                                        | 100 |

|   |     | 7.3.3    | Magnetoresistance                                               | 101 |

|   | 7.4 | Y-fun    | ction based extraction                                          | 102 |

|   | 7.5 | Two-c    | channel model                                                   | 104 |

|   |     | 7.5.1    | PD MOSFETs: two independent channels                            | 105 |

|   |     | 7.5.2    | FD MOSFETs with two separate, intercoupled channels $$ . $$ .   | 107 |

|   | 7.6 | Balan    | ced double-gate mode                                            | 112 |

|   |     | 7.6.1    | Y-function for balanced double-gate operation                   | 112 |

|   |     | 7.6.2    | Partially depleted transistor                                   | 114 |

|   |     | 7.6.3    | Fully depleted transistor                                       | 116 |

|   | 7.7 | Exper    | imental results                                                 | 117 |

|   |     | 7.7.1    | Partially depleted transistors                                  | 118 |

|   |     | 7.7.2    | Ultrathin fully depleted transistor                             | 118 |

|   |     | 7.7.3    | Balanced charge double-gate operation                           | 122 |

|   | 7.8 | Concl    | usions                                                          | 125 |

| 8 | Mo  | bility s | simulation results                                              | 127 |

|   | 8.1 | Introd   | luction                                                         | 127 |

|   | 8.2 | Carrie   | er mobility in arbitrarily oriented bulk and SOI MOSFETs $$     | 128 |

|   |     | 8.2.1    | Electron mobility in bulk MOSFETs                               | 132 |

|   |     | 8.2.2    | Double Gate structures                                          | 137 |

|   | 8.3 | Low-fi   | eld mobility simulation in strained double-gate SOI transistors | 143 |

|              |       | 8.3.1 Self-consistent solution of Poisson and Schrödinger equations     | 145 |

|--------------|-------|-------------------------------------------------------------------------|-----|

|              |       | 8.3.2 Monte Carlo mobility results                                      | 148 |

|              | 8.4   | Magnetoresistance simulation and results                                | 150 |

|              | 8.5   | Conclusions                                                             | 153 |

| Co           | onclu | sions                                                                   | 157 |

| II           | I A   | PPENDIX                                                                 | 161 |

| $\mathbf{A}$ | Sho   | rt summaries                                                            | 163 |

|              | A.1   | English                                                                 | 163 |

|              | A.2   | Français                                                                | 164 |

|              | A.3   | Español                                                                 | 165 |

| В            | Rés   | umé de la Thèse                                                         | 167 |

|              | B.1   | Simulation quantique du MOSFET avec orientations cristallographi-       |     |

|              |       | ques alternatives et grilles de siliciurées (chapitres 1, 2 et 3)       | 168 |

|              | B.2   | Mécanismes de dispersion dans MOSFETs avec oxyde de grille ul-          |     |

|              |       | tramince (chapitre 4)                                                   | 168 |

|              | B.3   | Technologie Silicium sur Isolant: caractérisation des wafers (chapitres |     |

|              |       | 5, 6 et 7)                                                              | 169 |

|              | B.4   | Simulations de mobilité avec la technique Monte Carlo (chapitre $8$ ) . | 171 |

| $\mathbf{C}$ | List  | of publications                                                         | 173 |

|              | C.1   | Referenced papers                                                       | 173 |

|              | C.2   | Conference contributions                                                | 174 |

| Bi           | hlios | ranhy                                                                   | 177 |

## List of Figures

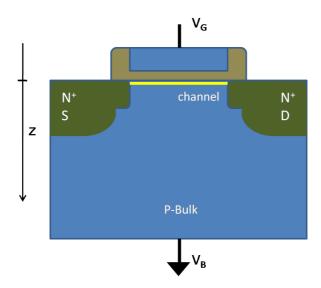

| 1.1 | Schematic MOSFET structure                                                                                                                                                                                                                                                                                                                                                                              | 4  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

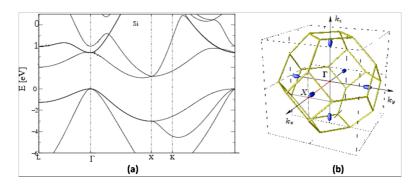

| 1.2 | (a) Silicon band structure. (b) First Brillouin zone and associated isoenergetic ellipsoids for silicon. Source http:\\iue.tuwien.ac.at                                                                                                                                                                                                                                                                 | 6  |

| 1.3 | Flowchart for the effective-mass evaluation                                                                                                                                                                                                                                                                                                                                                             | 9  |

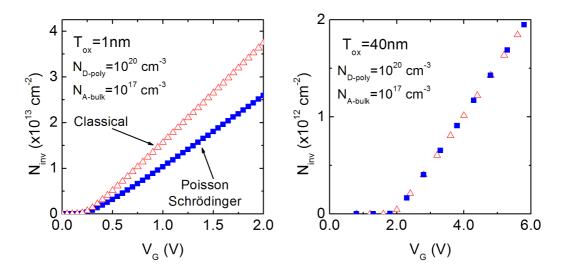

| 2.1 | Electron density versus gate voltage in a MOS structure for two values of the gate oxide thickness. Classical modeling (Expression 2.1, open symbols) fails dramatically when oxide thickness is reduced due to inversion charge penetration in the silicon bulk and polysilicon depletion effect. Closed symbols are calculated from the self-consistent solution of Poisson and Schrödinger equations | 14 |

| 2.2 | Charge distribution in a MOS structure obtained from the self consistent solution of Poisson-Schrödinger equations                                                                                                                                                                                                                                                                                      | 15 |

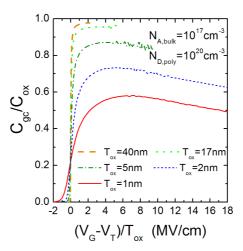

| 2.3 | Gate-to-channel capacitance versus $\left(V_G - V_T\right)/T_{ox}$ in a n-channel MOSFET for various gate-oxide thicknesses                                                                                                                                                                                                                                                                             | 16 |

| 2.4 | Inversion charge centroid versus the inverson electron concentration in a MOS structure for three common silicon crystallographic orientations.                                                                                                                                                                                                                                                         | 18 |

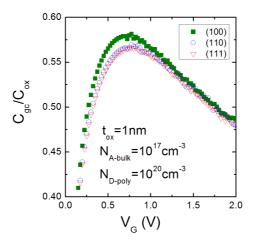

| 2.5 | Gate-to-channel capacitance versus the gate voltage in an ultrathin-<br>gate-oxide NMOSFET for various silicon crystallographic orienta-<br>tions. As shown, $C_{gc}$ is greater for the (100) crystallographic ori-<br>entation due to the lower value of the centroid of the inversion charge<br>associated with this orientation                                                                     | 20 |

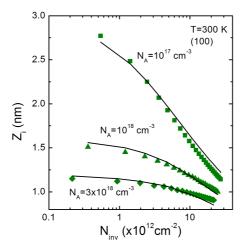

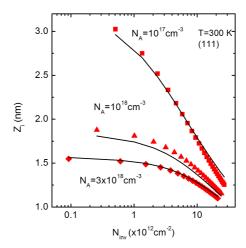

| 2.0  | for MOSFETs on (100) wafers at room temperature for different substrate doping concentrations. The results obtained from the Poisson-Schrödinger solution are shown in solid lines, and the data calculated with the model (Eq. 2.11) are shown in symbols                                                                                                            | 24 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.7  | Inversion charge centroid versus inversion charge concentration for MOSFETs on (110) wafers at room temperature for different substrate doping concentrations. The results obtained from the Poisson-Schrödinger solution are shown in solid lines and the data calculated with the proposed model in symbols                                                         | 25 |

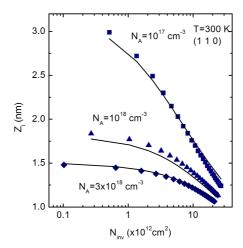

| 2.8  | Inversion charge centroid versus inversion charge concentration for MOSFETs on (111) wafers at room temperature for different substrate doping concentrations. The results obtained from the Poisson-Schrödinger solution are shown in solid lines and the data calculated with the proposed model in symbols                                                         | 26 |

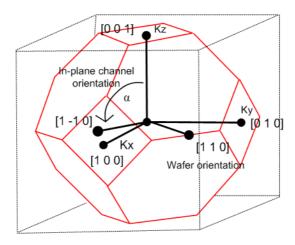

| 2.9  | First Brillouin Zone showing the in-plane transport direction variation angle for a (110) wafer                                                                                                                                                                                                                                                                       | 27 |

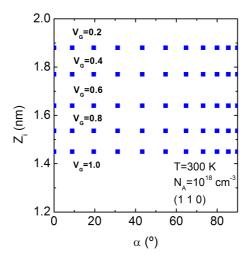

| 2.10 | Inversion charge centroid versus in-plane transport direction variation angle for different gate voltages in a MOSFET fabricated on a (110) wafer                                                                                                                                                                                                                     | 28 |

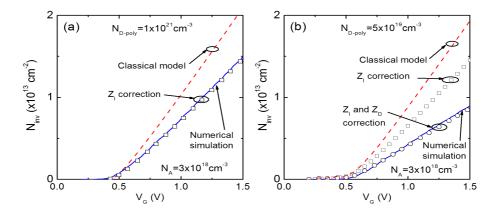

| 2.11 | Electron concentration versus gate voltage in an n-channel MOS-FET with $T_{ox}=1nm$ and the following polysilicon doping levels: (a) $N_{D-poly}=1\times10^{21}\mathrm{cm^{-3}}$ ; (b) $N_{D-poly}=5\times10^{19}\mathrm{cm^{-3}}$ ; A comparison among different models and the self-consistent solution of Poisson and Schrödinger equations (solid line) is shown | 29 |

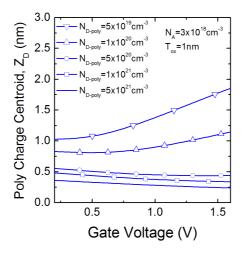

| 2.12 | Polysilicon charge centroid in an n-MOSFET versus gate voltage, for different values of polysilicon doping                                                                                                                                                                                                                                                            | 30 |

|      |                                                                                                                                                                                                                                                                                                                                                                       |    |

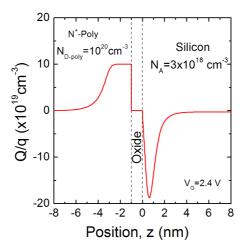

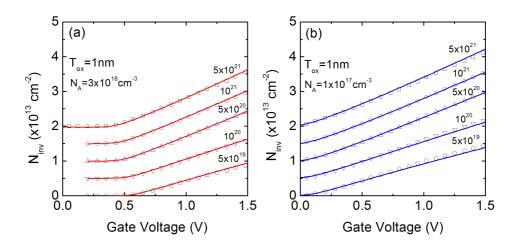

| 2.13 | Inversion electron concentration versus the gate voltage in an n-channel                          |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | MOSFET for different values of the polysilicon doping concentration.                              |    |

|      | Two different values of the silicon doping concentration have been                                |    |

|      | considered: (a) $N_A = 3 \times 10^{18} cm^{-3}$ , (b) $N_A = 10^{17} cm^{-3}$ Solid lines        |    |

|      | correspond to the self-consistent solution of Poisson and Schrödinger                             |    |

|      | equations, and symbols correspond to data obtained with the pro-                                  |    |

|      | posed model (Eqs. 2.20 & 2.21). For the sake of reading clar-                                     |    |

|      | ity, curves corresponding to poly doping concentrations higher than                               |    |

|      | $N_{D-poly} = 5 \times 10^{19} cm^{-3}$ have been vertically drifted by a fixed                   |    |

|      | amount, i.e., we added $5 \times 10^{12} cm^{-2}$ to the curve corresponding to                   |    |

|      | $N_{D-poly} = 1 \times 10^{20} cm^{-3}$ (down triangles), $1 \times 10^{13} cm^{-2}$ to the curve |    |

|      | corresponding to $N_{D-poly} = 5 \times 10^{20} cm^{-3}$ (up triangles) and so on.                |    |

|      | In fact, all the curves should coincide in the lower left-hand corner of                          |    |

|      | the graph                                                                                         | 32 |

|      |                                                                                                   |    |

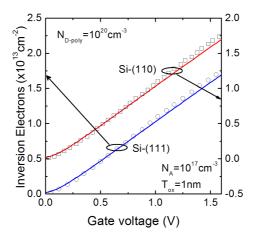

| 2.14 | Inversion electron concentration versus gate voltage in an n-channel                              |    |

|      | MOSFET for different silicon crystallographic orientations                                        | 33 |

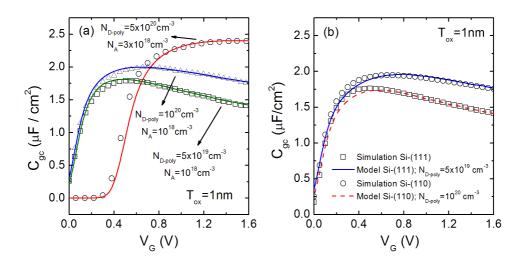

| 2.15 | (a) Gate-to-channel capacitance versus gate voltage in an n-channel                               |    |

|      | MOSFET with $T_{ox} = 1nm$ . Solid line: model results Eq. 2.27).                                 |    |

|      | Symbols: simulation results. (b) Gate-to-channel capacitance versus                               |    |

|      | gate voltage in an n-channel MOSFET with $T_{ox} = 1nm$ for different                             |    |

|      | silicon crystallographic orientations $(N_A = 10^{17} cm^{-3})$                                   | 34 |

|      | income of second graphic effections (x.A 10 ene )                                                 | 0. |

| 0.1  |                                                                                                   |    |

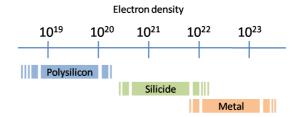

| 3.1  | Estimated free electron density range in polysilicon, silicide and metals                         | 20 |

|      | [AM76]                                                                                            | 39 |

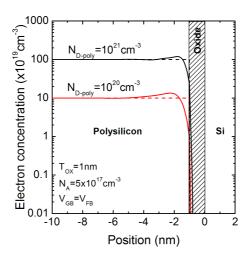

| 3.2  | Cross section electron concentration of the Metal-Oxide-Semiconductor                             |    |

|      | structure at flat-band bias for two different polysilicon doping levels.                          |    |

|      | Classical solution: dashed line, full-quantum: continuous line                                    | 40 |

|      | ·                                                                                                 |    |

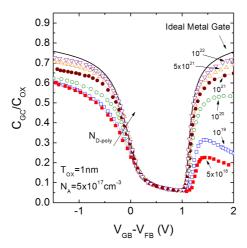

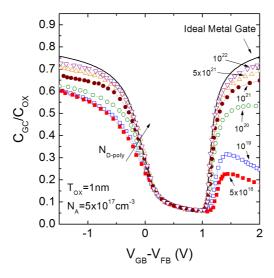

| 3.3  | Low-frequency gate-to-channel capacitance normalized by the phys-                                 |    |

|      | ical oxide capacitance for different polysilicon doping levels. Ideal                             |    |

|      | metal behavior is never reproduced                                                                | 41 |

|      |                                                                                                   |    |

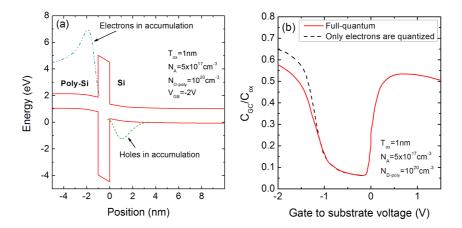

| 3.4 | (a) Energy-band diagram (maximum of the valence band and minu-                                                                          |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | mum of the conduction band) of the MOS structure in accumulation                                                                        |     |

|     | for $V_G = -2V$ . The corresponding charge density in superposed. (b)                                                                   |     |

|     | Low-frequency gate-to-channel capacitance normalized by the physical inculator capacitance. Classical calculators for halos and account |     |

|     | ical insulator capacitance. Classical solution for holes and quantum                                                                    | 4.0 |

|     | for electrons: dashed line. Full-quantum: continuous line                                                                               | 43  |

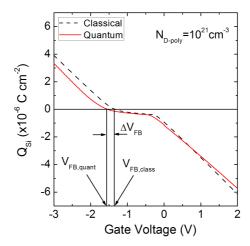

| 3.5 | Total charge in silicon versus gate voltage for the classical (dashed-                                                                  |     |

|     | line) and full-quantum (continuous-line) solution. Flat-band voltage                                                                    |     |

|     | is defined for zero charge the silicon                                                                                                  | 44  |

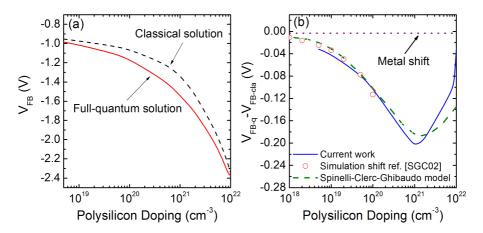

| 3.6 | (a) Simulation extracted flat-band voltage for different polysilicon                                                                    |     |

|     | doping levels. Solid line: from full-quantum solution; dashed line:                                                                     |     |

|     | from classical solution. (b) Comparison between simulation results                                                                      |     |

|     | (continuous line and circles) and the model (dashed line) for the shift                                                                 |     |

|     | in the flat-band voltage as a function of the polysilicon doping                                                                        | 45  |

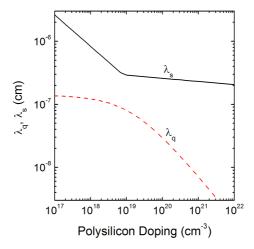

| 3.7 | $\lambda_q$ and $\lambda_s$ variation as a function of the polysilicon doping                                                           | 46  |

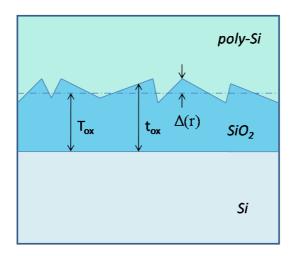

| 4.1 | Schematic representation of the modeled scattering mechanisms. The                                                                      |     |

|     | polysilicon- $SiO_2$ roughness is equivalent to a change in the insulator                                                               |     |

|     | thickness, while the depleted charges in the polysilicon cause remote                                                                   |     |

|     | Coulomb scattering                                                                                                                      | 49  |

| 4.2 | Schematics of the polysilic<br>on-oxide interface roughness considered. $$ .                                                            | 50  |

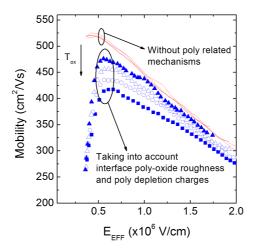

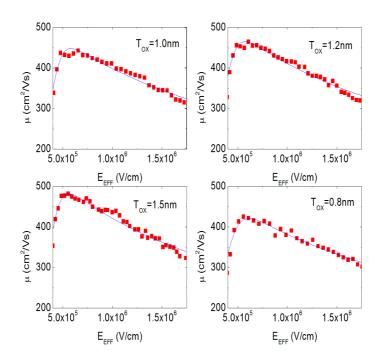

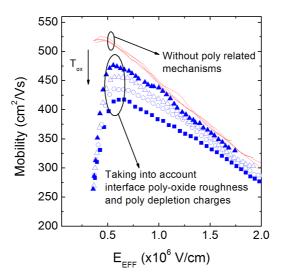

| 4.3 | Electron mobility versus effective field for the MOSFET devices used.                                                                   |     |

|     | The mobility curves plotted in symbols are calculated taking into ac-                                                                   |     |

|     | count the surface-roughness of the polysilicon-oxide interface as well                                                                  |     |

|     | as the polysilicon depletion charge by means of the remote surface-                                                                     |     |

|     | roughness and Coulomb scattering mechanisms. The curves shown in                                                                        |     |

|     | lines are calculated by neglecting these mechanisms. $T_{OX}$ = 0.8 nm                                                                  |     |

|     | (■), $T_{OX}$ = 1.0 nm (o), $T_{OX}$ = 1.2 nm (△), $T_{OX}$ = 1.5 nm (▲)                                                                | 51  |

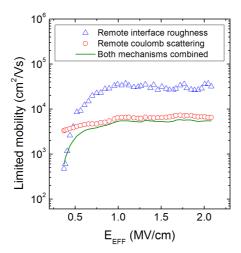

| 4.4 | Mobility versus electric field showing the distinct remote scattering                                                                   |     |

|     | mechanisms obtained by means of Mathiessen's rule for a MOS struc-                                                                      |     |

|     | ture $(N_{\text{D-poly}} = 10^{20} cm^{-3}, N_{\text{A}} = 5 \times 10^{17} cm^{-3}, L_{\text{sr-remote}} = 1.5 nm,$                    |     |

|     | $\Delta_{\text{sr-remote}} = 0.185 nm$ ). Open triangles: remote surface-roughness scat-                                                |     |

|     | tering. Open circles: remote coulomb scattering                                                                                         | 53  |

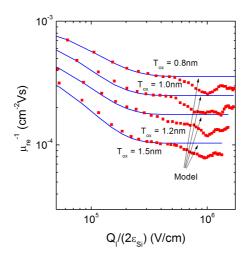

| 4.5 | Remote scattering mobility component versus the inversion charge.  Accuracy in modelling this component is only needed at low inversion charges; at high inversion charges its role is minor in comparison with other scattering mechanisms such as Si–SiO <sub>2</sub> surface-roughness scattering                                                                                                                                                                                                                                                                                      | 55 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

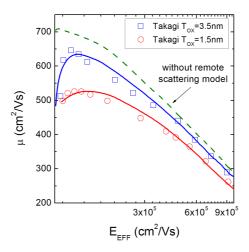

| 4.6 | Electron mobility versus effective field for different oxide thicknesses at room temperature. Monte Carlo calculated results are shown in symbols and the data obtained using the analytical model are shown in solid lines                                                                                                                                                                                                                                                                                                                                                               | 57 |

| 4.7 | Electron mobility versus effective field at room temperature. The experimental electron mobility curves reported in [TT02] are shown in symbols. The mobility modelled including phonons, interface Si-SiO <sub>2</sub> roughness, Coulomb scattering, remote roughness and Coulomb scattering due to polysilicon depletion charges are shown in solid lines. The mobility modelled without taking remote mechanisms into account is shown in dashed lines. $(N_A=3\times10^{16}cm^{-3},N_{D-poly}=6\times10^{19}cm^{-3},N_{it}=5\times10^{10}cm^{-2},L_{sr}=1.3nm,\Delta_{sr}=0.35nm)$ . | 58 |

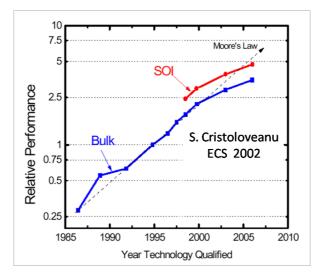

| 5.1 | Comparison between Moore prediction and the perfomances of traditional bulk Si and SOI technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 |

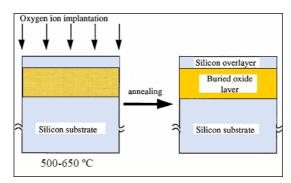

| 5.2 | The principle of SIMOX: a heavy-dose oxygen implantation into silicon followed by a very high temperature annealing step produces a buried layer of silicon dioxide below a thin, single-crystal silicon overlayer.                                                                                                                                                                                                                                                                                                                                                                       | 66 |

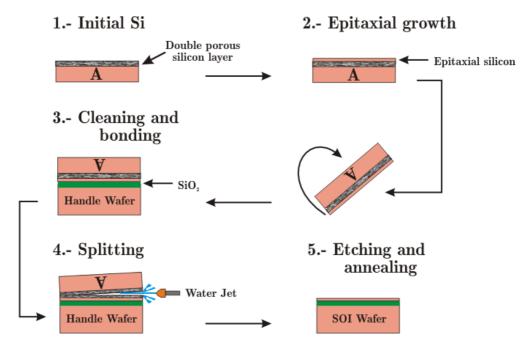

| 5.3 | Schematic of the ELTRAN process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68 |

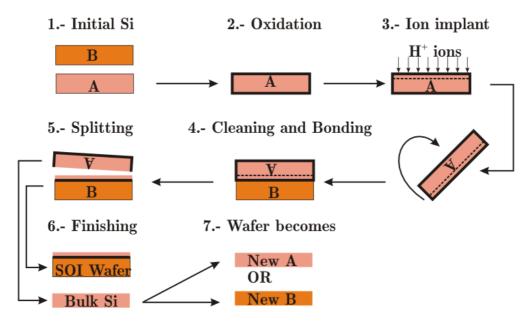

| 5.4 | Obtaining SOI wafers by Smart-Cut $^{TM}$ method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |

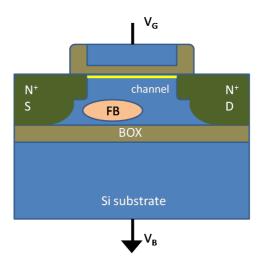

| 5.5 | Configuration of a partially depleted SOI MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73 |

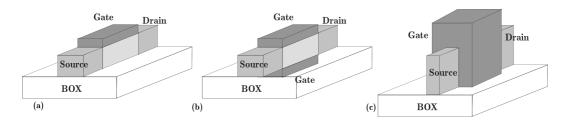

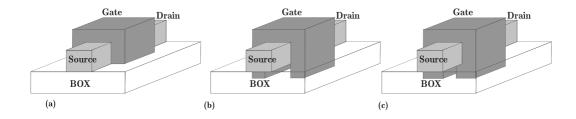

| 5.6 | Schematic representation of SOI devices: (a)SGSOI, (b) DGSOI, (c) FinFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 74 |

| 5.7 | Schematic representation of SOI devices: (a) Trigate, (b) $\Pi$ -Gate, (c) $\Omega$ -Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

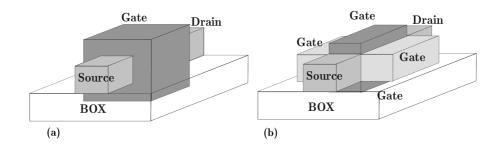

| 5.8 | Schematic representation of SOI devices: (a) GAA, (b) $G^4FET.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

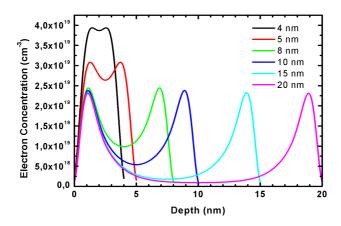

| 5.9  | Charge density dependence along the silicon thickness in double gate devices. The interaction between both channels (volume inversion) is revealed being specially significant below 10nm                                                                                        | 76 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

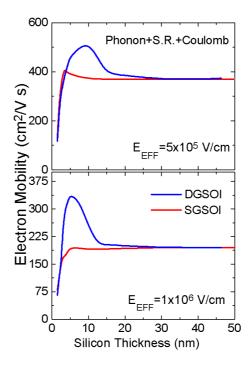

| 5.10 | Monte Carlo simulated mobility dependence on the silicon film thickness. The effect of volume inversion is clearly seen leading to an important mobility increase for silicon films thinner than 10nm                                                                            | 77 |

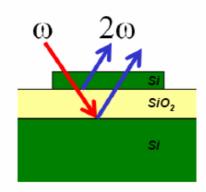

| 6.1  | Schematic diagram of UNIBOND wafer structure for optical measurements: Incident fundamental beam and selected SHG signals                                                                                                                                                        | 80 |

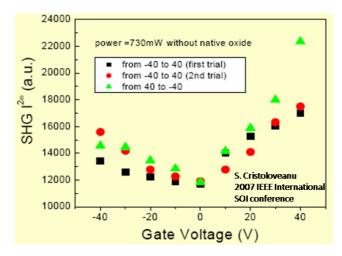

| 6.2  | Transistor like contact less $\Psi$ -MOSFET curves similar to drain-gate voltage curves                                                                                                                                                                                          | 82 |

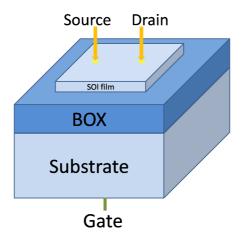

| 6.3  | Schematic configuration of the $\Psi$ -MOSFET                                                                                                                                                                                                                                    | 83 |

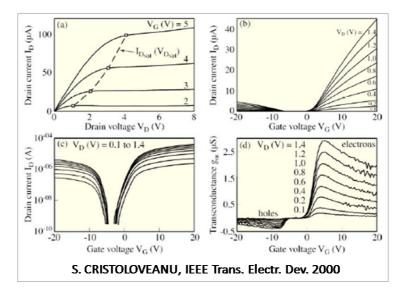

| 6.4  | Typical $\Psi$ -MOSFET characteristics in UNIBOND <sup>©</sup> material: (a) drain current versus drain voltage, (b) drain current versus gate voltage in strong inversion and strong accumulation, (c) weak inversion/accumulation curves, and (d) transconductance curves      | 84 |

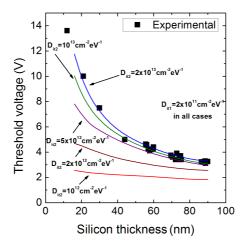

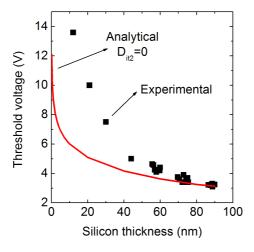

| 6.5  | Experimental extracted (solid symbols) and simulated threshold voltage versus the silicon thickness for various trap densities of surface states. For $D_{it2}=2\times 10^{13}cm^{-3}eV^{-1}$ the simulation fits the experimental data. $t_{BOX}=145\mathrm{nm}$                | 85 |

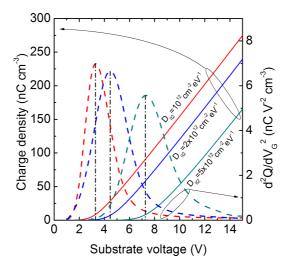

| 6.6  | Charge density (continuous line) and second derivative of the charge density (dashed line) illustrating the threshold voltage extraction procedure. In all cases $D_{it1}=2\times10^{11}cm^{-2}eV^{-1}$                                                                          | 86 |

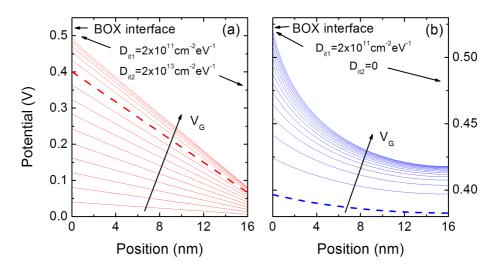

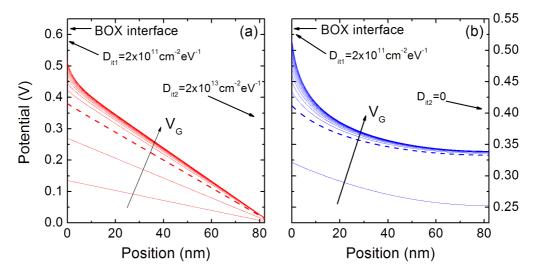

| 6.7  | Potential profiles from BOX interface to free surface for a 16nm thick pseudo-MOSFET with (a) high and (b) zero density of states at the top surface. $V_G$ increases from 1V by 1V steps. The portential profile corresponding to the threshold voltage is shown in dashed line | 87 |

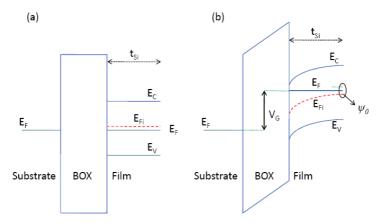

| 6.8  | Schematic energy band diagram. (a) No bias is supplied. (b) For positive bias, as a consequence of the absence of top potential condition, the band shifts leading an additional potential term supported by the                                                                 |    |

|      | gate voltage (circled area)                                                                                                                                                                                                                                                      | 88 |

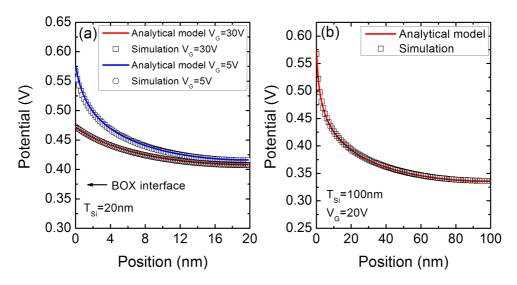

| 6.9  | Potential profiles from BOX interface to free surface for a 83nm thick pseudo-MOSFET with (a) high and (b) zero density of states at the                                                                                                                                                        |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | top surface. $V_G$ increases from 1V by 1V steps. The portential profile                                                                                                                                                                                                                        |     |

|      | corresponding to the threshold voltage is shown in dashed line                                                                                                                                                                                                                                  | 89  |

| 6.10 | Potential profile comparison between Eq. 6.14 and the numerical solution of Poisson equation (Eq. 6.10)                                                                                                                                                                                         | 90  |

| 6.11 | Comparison between the the analytical model (Eq. 6.21) considering a buried interface density of charge (BOX/Si-film interface) determined by $D_{it1}=2\times10^{11}cm^{-2}eV^{-1}$ and the experimental extracted values for the threshold voltage                                            | 92  |

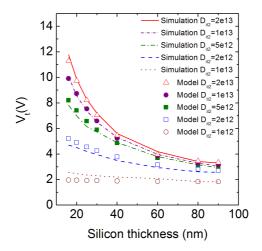

| 6.12 | Comparison between the empirical model (symbols) presented in Eq. 6.22 and the simulation results (lines). $D_{it1}=2\times10^{11}cm^{-2}eV^{-1}$ , $t_{BOX}=145nm$ , for all the curves shown.                                                                                                 | 93  |

| 7.1  | Threshold voltage extraction procedure from the drain current. A tangent is drawn at the inflexion point of the current curve. The intercept yields the extrapolated threshold voltage                                                                                                          | 96  |

| 7.2  | Constant-current threshold voltage extraction procedure                                                                                                                                                                                                                                         | 97  |

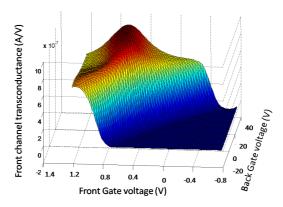

| 7.3  | Experimental typical front-channel transconductance distortion versus front- and back-gate voltages. As soon as the back channel is inverted a characteristic plateau appears as a consequence of the channel coupling. $T_{\rm Si}=10nm,\ L=10\mu m,\ W=1\mu m,\ T_{ox1}=2nm,\ T_{ox2}=145nm,$ |     |

|      | $N_A = 10^{15} cm^{-3}$                                                                                                                                                                                                                                                                         | 98  |

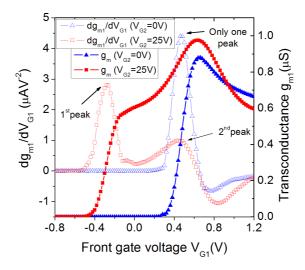

| 7.4  | Front-channel threshold voltage evaluation from the transconduct-<br>ance inflexion point (second-order current derivative) for two different                                                                                                                                                   |     |

|      | back-gate biases                                                                                                                                                                                                                                                                                | 99  |

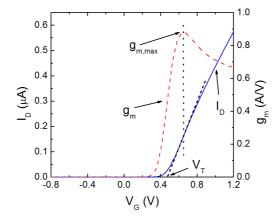

| 7.5  | Experimental drain current, $I_D$ , and transconductance, $g_m$ , versus gate voltage, $V_G$ . SOI-MOSFET characteristics: $L=10\mu m$ , $T_{ox}=2nm$ , $T_{si}=10nm$ , $T_{box}=145nm$ , $V_D=50mV$                                                                                            | 103 |

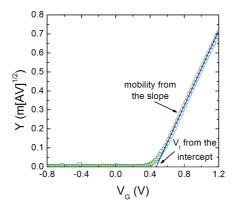

| 7.6  | Experimental Y-function MOSFET characteristic ilustrating the para-                                                                                                                                                                                                                             |     |

|      | meter extraction. Same device as in Figure 7.5                                                                                                                                                                                                                                                  | 104 |

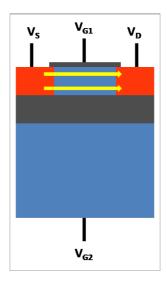

| 7.7  | Double channel sketch for a SOI MOSFET                                                                                                                                                                                                                                                          | 105 |

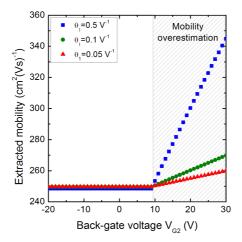

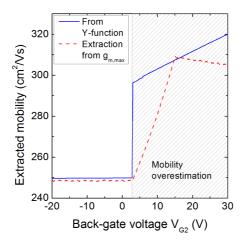

| 7.8  | Extracted front-channel mobility versus back-gate bias for different values of $\theta_1$ . Y-function leads to an overestimation of the mobility when the back channel is opened (Eqs. 7.15 and 7.16)                                                                                                                                                                                                                             | 107 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

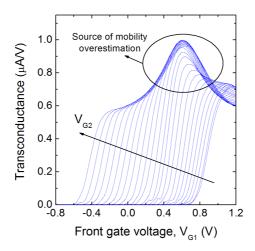

| 7.9  | Experimental front-channel transconductance as a function of the back-gate bias. Note that the transconductance peak is artificially increased as a consequence of the back-channel activation. $T_{\rm Si}=10nm$ , $L=10\mu m$ , $W=1\mu m$ , $T_{ox1}=2nm$ , $T_{ox2}=145nm$ , $N_A=10^{15}cm^{-3}$ . $V_{G2}$ starts in -20V with step of 2V up to 32V                                                                          | 108 |

| 7.10 | Extracted front-channel mobility from Y-function and from maximum value of the transconductance. A dramatic overestimation is observed as soon as the back channel is activated. Parameters: $t_{ox_1} = 2nm$ , $t_{ox_2} = 145nm$ , $V_{G_1} = 1V$ , $\mu_{01} = 250cm^2/Vs$ , $\mu_{02} = 350cm^2/Vs$ , $\theta_1 = 0.2V^{-1}$ , $\theta_2 = 0.0028V^{-1}$                                                                       | 109 |

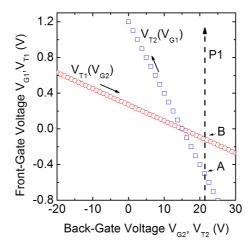

| 7.11 | Analytical choice for the threshold voltage dependencies in the region of interest. Symbols show the variation of the front-channel threshold voltage with back-gate bias and back-channel threshold voltage with front-gate bias. $P1$ bias: $Back$ gate is positive and back-channel is activated first when front bias is increased (point $A$ )                                                                                | 110 |

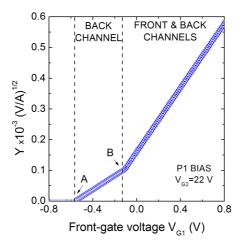

| 7.12 | Front-gate Y-function for $V_{G_2}=22V$ . Back channel is activated first according to Figure 7.11. Point A: back-channel activation; point B: front-channel activation. The <i>back</i> channel mobility can be extracted in region $A$ - $B$ with the Y-function. Parameters: $t_{ox_1}=2nm$ , $t_{ox_2}=145nm$ , $\mu_{01}=250cm^2/Vs$ , $\mu_{02}=350cm^2/Vs$ , $\theta_1=0.2V^{-1}$ , $\theta_2=0.0028V^{-1}$                 | 111 |

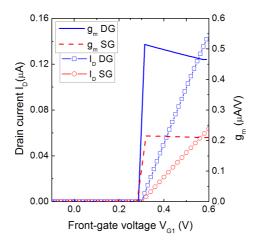

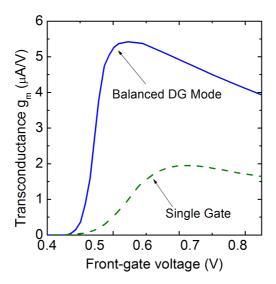

| 7.13 | Modeled drain current and transconductance curves of a PD-SOI transistor operated in DG balanced charge mode. The back-gate bias is adjusted with Eq. 7.22. An increase in drain current and transconductance is observed in DG mode compared to SG operation. Parameters: $t_{ox_1}=2nm,\ t_{ox_2}=145nm,\ V_{T_1}=0.3V,\ V_{T_2}=9V,$ $\mu_{01}=250cm^2/Vs,\ \mu_{02}=350cm^2/Vs,\ \theta_1=0.2V^{-1},\ \theta_2=0.0028V^{-1}$ . | 115 |

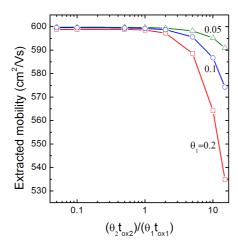

| 7.14 | Extracted mobility sum when the condition (7.24) is more or less                                                                            |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | satisfied. Only when $\theta_2 t_{ox2} > 3\theta_1 t_{ox1}$ is the mobility underestimated.                                                 |     |

|      | Transistor parameters: $t_{ox_1}=2nm$ , $t_{ox_2}=145nm$ , $V_{T_1}=0.3$ , $V_{T2}=9V$ ,                                                    |     |

|      | $\mu_{01} = 250  \text{cm}^2 / \text{Vs}, \ \mu_{02} = 350  \text{cm}^2 / \text{Vs}. \ \dots \dots \dots \dots \dots \dots \dots$           | 116 |

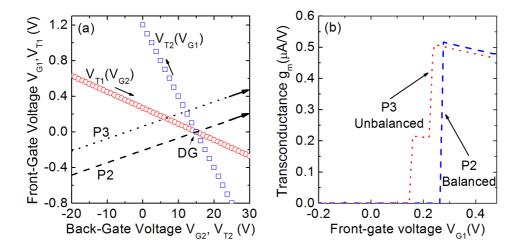

| 7.15 | (a) Analytical choice for the threshold voltage dependencies in the                                                                         |     |

|      | region of interest. Symbols show the variation of the front-channel                                                                         |     |

|      | threshold voltage with back-gate bias and back-channel threshold                                                                            |     |

|      | voltage with front-gate bias. P2 & P3: Balanced double-gate bias-                                                                           |     |

|      | ing polarization lines corresponding to Eq. (7.22). P2 bias: Correct                                                                        |     |

|      | choice using the crossing point $(DG)$ of the threshold voltage lines.                                                                      |     |

|      | P3 bias: example of wrong choice defining the threshold voltages                                                                            |     |

|      | for zero bias at the opposite gate. (b) Transconductance versus                                                                             |     |

|      | front-gate voltage (the back-gate bias was adjusted with Eq. 7.22).                                                                         |     |

|      | P2 dashed line: perfect balanced choice for the threshold voltages                                                                          |     |

|      | $(V_{T_1} = 0V, V_{T_2} = 15V)$ , the activation of both channels is achieved                                                               |     |

|      | simultaneously. $P3$ dotted line: Unbalanced line; back channel opens                                                                       |     |

|      | before front channel                                                                                                                        | 117 |

| 7.16 | HP4155A Semiconductor parameter analyzer (leftt hand side). Karl                                                                            |     |

|      | Suss four probe station (right hand side)                                                                                                   | 118 |

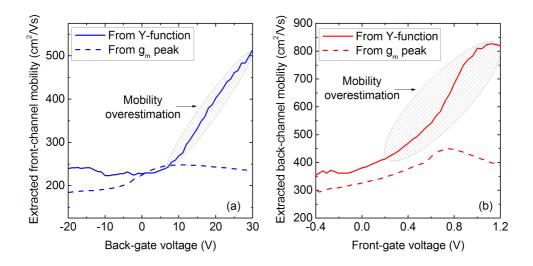

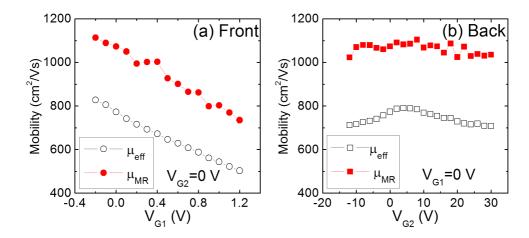

| 7.17 | (a) Experimentally extracted front-channel mobility versus back-gate                                                                        |     |

|      | voltage using the $Y$ -function or the transconductance peak. (b) Ex-                                                                       |     |

|      | perimentally extracted back-channel mobility versus front-gate voltage                                                                      |     |

|      | using the $Y$ -function or the transconductance peak. Ultrathin FD                                                                          |     |

|      | $\label{eq:MOSFET: T_Si=10nm, L=10} \text{MOSFET: } T_{\text{Si}} = 10nm, \ L = 10\mu m, \ W = 1\mu m, \ T_{ox1} = 2nm, \ T_{ox2} = 145nm,$ |     |

|      | $N_A = 10^{15} cm^{-3}$                                                                                                                     | 119 |

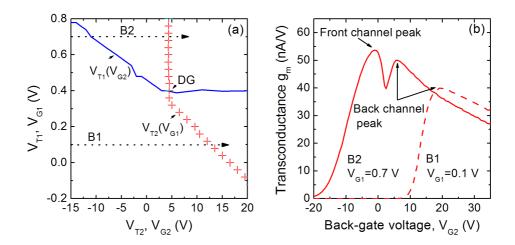

| 7.18 | (a) Experimental threshold voltages (extracted from the peak of the                                                                         |     |

|      | second derivative of the drain current) for the $front$ and $back$ chan-                                                                    |     |

|      | nels versus the opposite gate bias. $B1$ & $B2$ dotted lines: Bias                                                                          |     |

|      | conditions corresponding to continuous and dashed curves in Figure                                                                          |     |

|      | 7.18(b). Same device as in Figure 7.17. (b) Back-gate transconduct-                                                                         |     |

|      | ance measured for two different front-gate voltages. The activation                                                                         |     |

|      | of $front$ channel before $back$ channel can be seen in the $B\mathcal{Z}$ curve                                                            |     |

|      | corresponding to the bias shown in Figure 7.18(a)                                                                                           | 120 |

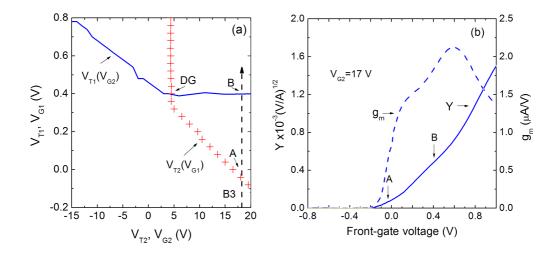

| 7.19 | (a) Experimental threshold voltages extracted from the peak of the transconductance for the <i>front</i> and <i>back</i> channels versus the oppos- |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | ite gate bias. $B3$ dashed line: Bias conditions for extracting the                                                                                 |     |

|      | back-channel mobility from the front-gate Y-function. Same device                                                                                   |     |

|      | as in Figure 7.17. (b) Front gate Y-function (continuous line) and                                                                                  |     |

|      | transconductance (dashed line) corresponding to $B3$ bias in Figure                                                                                 |     |

|      | 7.19 (a)                                                                                                                                            | 121 |

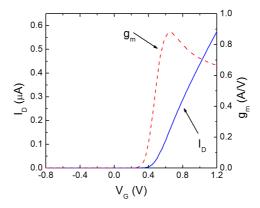

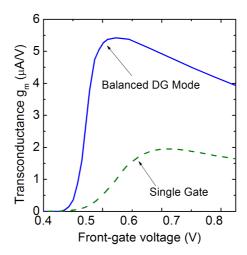

| 7.20 | $\operatorname{SG}$ and $\operatorname{DG}$ transconductance measured in an ultrathin FD SOI MOS-                                                   |     |

|      | FET. An increment of $200\%$ is observed for DG operation, which is                                                                                 |     |

|      | induced by volume inversion and cannot be explained by a 2-channels                                                                                 |     |

|      | model. Same device as in Figure 7.17                                                                                                                | 123 |

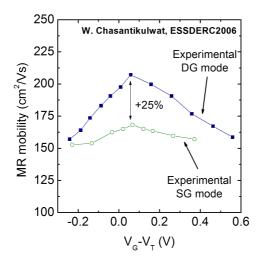

| 7.21 | Magnetoresistance mobility of a DG transistor operating in DG and                                                                                   |     |

|      | SG mode as a function of $V_G$ - $V_T$ . Transistor parameters: $t_{\rm Si}$ =6nm,                                                                  |     |

|      | $t_{ox1} = t_{ox2} = 2nm, L_g = 70nm, W = 10 \mu m.$                                                                                                | 124 |

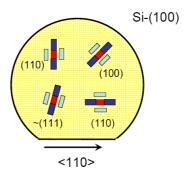

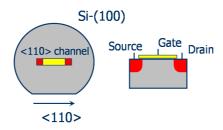

| 8.1  | Different orientations of DG-MOSFETs on a Si-(100) wafer                                                                                            | 129 |

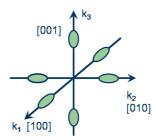

| 8.2  | Constant energy ellipsoids for Si conduction band                                                                                                   | 131 |

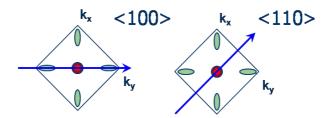

| 8.3  | Two-dimensional schematic constant-energy ellipses for (001), (110),                                                                                |     |

|      | and (111) Si conduction band [SH70]. Lower energy subbands are                                                                                      |     |

|      | shown in red                                                                                                                                        | 132 |

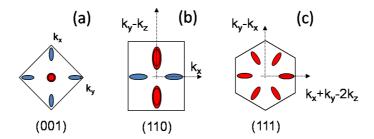

| 8.4  | Schematic representation of a MOSFET transistor fabricated on a                                                                                     |     |

|      | (100) Si wafer                                                                                                                                      | 133 |

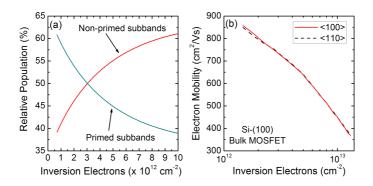

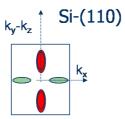

| 8.5  | (a) Relative primed and non-primed subbands population as a func-                                                                                   |     |

|      | tion of the inversion electron density. For high inversion charge most                                                                              |     |

|      | of the electrons populate the non-primed subbands with isotropic con-                                                                               |     |

|      | duction mass. (b) Electron mobility as a function of the inversion                                                                                  |     |

|      | charge in a (100) – MOSFET for two channel directions                                                                                               | 133 |

| 8.6  | Two-dimensional schematic constant energy ellipses for (100) confine-                                                                               |     |

|      | ment crystallographic orientation. Channel $\langle 100 \rangle$ and $\langle 110 \rangle$ directions                                               |     |

|      | are presented                                                                                                                                       | 134 |

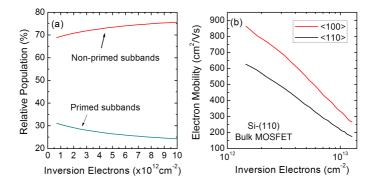

| 8.7  | Two-dimensional schematic constant energy ellipses for (110) confine-                                                                               |     |

|      | ment crystallographic orientation. Channel $\langle 011 \rangle$ and $\langle 100 \rangle$ directions                                               |     |

|      | are presented                                                                                                                                       | 135 |

| 8.8  | (a) Relative primed and non-primed subbands population as a function of the inversion electron density. For all the inversion charge range, most of the electrons populate the non-primed subbands with anisotropic conduction mass. (b) Electron mobility as a function of |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | the inversion charge in a (110) –MOSFET for two channel directions.                                                                                                                                                                                                         | 135  |

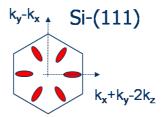

| 8.9  | Two-dimensional schematic constant energy ellipses for (111) confinement crystallographic orientation. The quantization does not split the degenerancy of the Si conduction band minima                                                                                     | 136  |

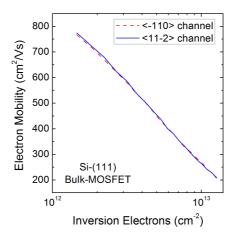

| 8.10 | Electron mobility as a function of the inversion charge in a (111)-MOSFET for two channel directions                                                                                                                                                                        | 137  |

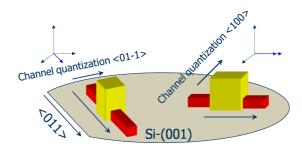

| 8.11 | Schematic representation of alternative quatization and channel crystallographic orientations for DG-FETs on a (100) silicon wafer                                                                                                                                          | 138  |

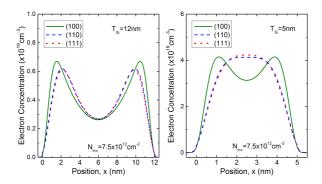

| 8.12 | Electron distribution in a DG-MOSFET for different surface orienta-                                                                                                                                                                                                         |      |

|      | tions and different silicon thicknesses                                                                                                                                                                                                                                     | 138  |

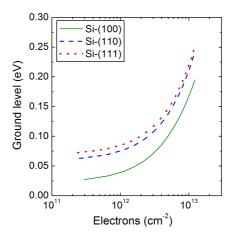

| 8.13 | The higher quantization mass in the Si-(100) orientations produces lower subband - levels (electrons are more confined to the $\rm Si/SiO_2$ interface)                                                                                                                     | 139  |

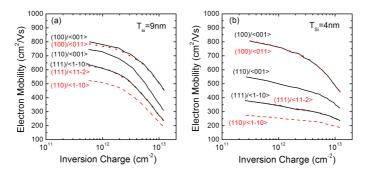

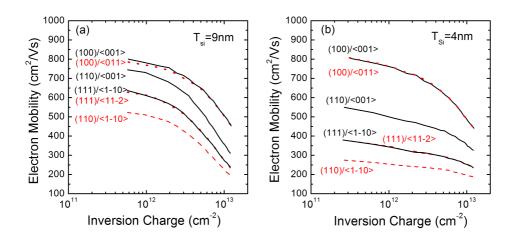

| 8.14 | Electron mobility as a function of the inversion charge in a DG MOS-FET for different surface orientations $(hkl)$ and different channel orientations $\langle hkl \rangle$ for two different Si film thicknesses: (a) 9nm, (b)                                             |      |

|      | 4nm                                                                                                                                                                                                                                                                         | 140  |

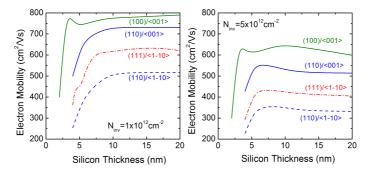

| 8.15 | Evolution of the electron mobility in a DG MOSFET with the silicon thickness for different combinations of surface orientation $(khl)$ and channel direction $\langle hkl \rangle$ .(a) $N_{inv} = 10^{12} cm^{-2}$ ; (b) $N_{inv} = 5 \times 10^{12} cm^{-2}$ .            | 141  |

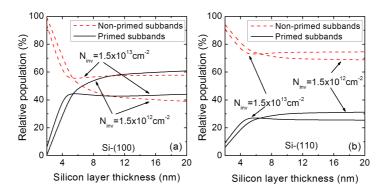

| 8.16 | Subbands population as a function of the silicon thickness for two values of the inversion charge. Two confinement orientations are                                                                                                                                         | 1.40 |

|      | presented: (a) Si-(100), (b) Si-(110)                                                                                                                                                                                                                                       | 142  |

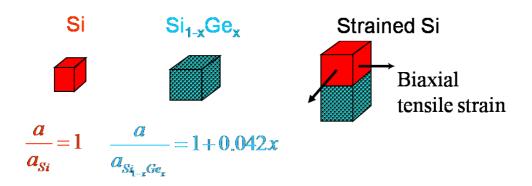

|      | Lattice constant modification when Si is grown on $Si_{1-x}Ge_x$                                                                                                                                                                                                            | 143  |

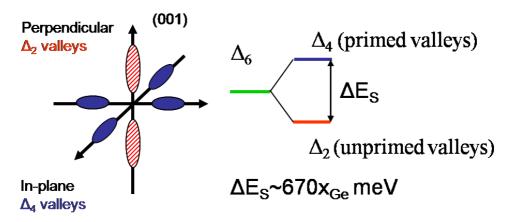

| 8.18 | Schematic representation of the isoenergetic ellipsoids when biaxial strain is applied on the plane parallel to the channel                                                                                                                                                 | 144  |

| 0 10 | Schematic of a strained DGSOI MOSFET                                                                                                                                                                                                                                        | 144  |

| 0.19 | OCHEHIALIC OF A SITAINED DATOUT MOOFFILE                                                                                                                                                                                                                                    | 140  |

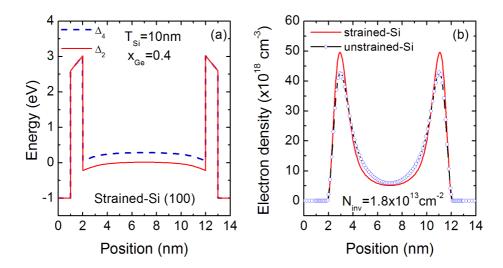

| 8.20 | (a): Potential well in a strained DGSOI MOSFET. Silicon thickness was assumed to be 10 nm. Solid line shows the conduction band edge for the two valleys with longitudinal effective mass perpendicular to the interface $(\Delta_2)$ while dashed line represents the conduction band edge for the four valleys with transverse effective mass perpendicular to the interface $(\Delta_4)$ . (b): Electron density in a strained DGSOI MOSFET (solid line) and an unstrained DGSOI MOSFET (symbols) for the same value of the inversion charge concentration | 146 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.21 | Electron density in a strained DGSOI MOSFET (solid line) and an unstrained DGSOI MOSFET (dashed line) for the same value of the inversion charge concentration                                                                                                                                                                                                                                                                                                                                                                                                | 147 |

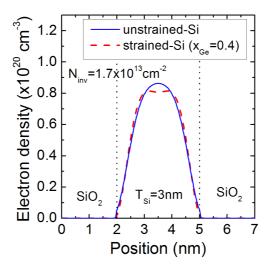

| 8.22 | Difference between the energy level of ground subband for unprimed and primed valleys and the Fermi level as a function of the electron density. Different $Ge$ mole fractions have been considered. Strained-Si thickness: (a) $T_w = 10nm$ , (b) $T_w = 3nm$                                                                                                                                                                                                                                                                                                | 148 |

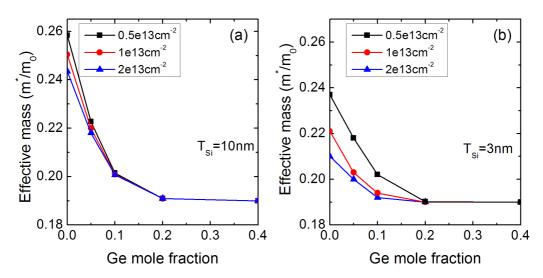

| 8.23 | Evolution of the conduction effective mass with the strain in a sDG-SOI transistor for two values of the silicon thickness and three values of the electron density                                                                                                                                                                                                                                                                                                                                                                                           | 149 |

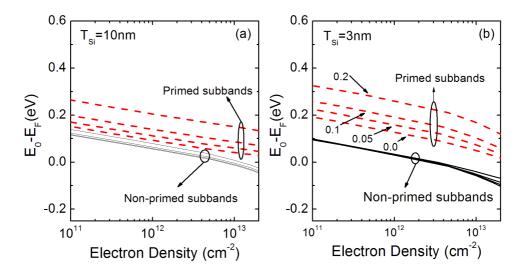

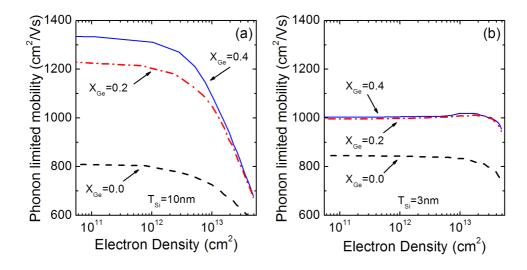

| 8.24 | Phonon limited mobility in a strained-Si DGSOI MOSFET for two values of the silicon thickness ((a) $T_w$ =10 $nm$ , and (b) $T_w$ =3 $nm$ ) and different strain grade magnitudes (Ge concentration)                                                                                                                                                                                                                                                                                                                                                          | 150 |

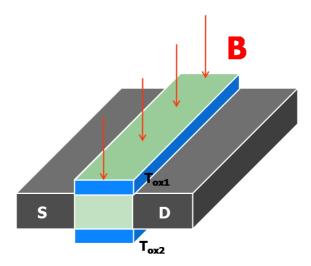

| 8.25 | Schematic representation of the device considered for Monte Carlo simulations. Magnetic field is applied perpendicular to the gates when magnetoresistance measurements are required                                                                                                                                                                                                                                                                                                                                                                          | 151 |

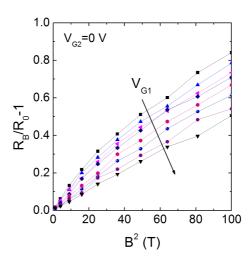

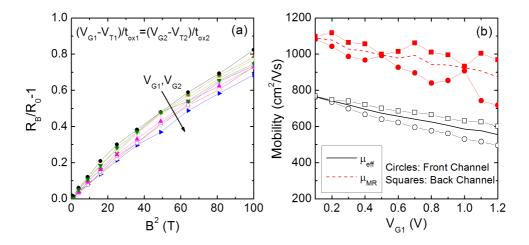

| 8.26 | Normalized magnetoresistance $R_B/R_0-1$ versus the square of the magnetic field for different front-channel bias $V_{G1}$ . Transistor parameters: $t_{Si}=20nm,\ \Delta_1=0.25nm.\ V_{G1}$ starts from -0.2V with step 0.2V                                                                                                                                                                                                                                                                                                                                 | 152 |

| 8.27 | Front (a) and back (b) channel effective mobility and magnetoresistance mobility for a SOI MOSFET with $t_{\rm Si}=20nm,~\Delta_1=0.25nm,$ $\Delta_2=0.1nm.$                                                                                                                                                                                                                                                                                                                                                                                                  | 153 |

| 8.28 | (a) Normalized MR $R_B/R_0 - 1$ versus the square of the magnetic                    |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | field for different values of $V_{G1}$ and $V_{G2}$ in DG mode. $V_{G1}$ starts from |     |

|      | -0.2V with step 0.2V. (b) Front-channel, back-channel and total DG                   |     |

|      | effective mobility (line) and magnetoresistance mobility (dashed line)               |     |

|      | for a DG MOSFET with $t_{\rm Si}=20nm,\Delta_1=0.25nm,\Delta_2=0.1nm.$               | 154 |

| B.1  | Capacité grille-canal aux basses fréquences normalisée par la capa-                  |     |

|      | cité de l'épaisseur physique de l'oxyde pour différentes concentrations              |     |

|      | d'électrons libres dans la grille. Le comportement idéal du métal n'est              |     |

|      | jamais atteint                                                                       | 169 |

| B.2  | Nous avons proposé un modèle empirique qui permet de reproduire                      |     |

|      | les corbes de mobilité en fonction du champ vertical, obtenues avec                  |     |

|      | la simulation Monte Carlo et avec des techniques expérimentales. Ce                  |     |

|      | modèle combine les différents mécanismes de collision selon la loi de                |     |

|      | Mathiessen                                                                           | 170 |

| B.3  | Transconductance mesurée pour modes simple-grille (SG) et double-                    |     |

|      | grille (DG) dans un transistor SOI MOSFET ultramince. Une aug-                       |     |

|      | mentation de 290% est observée en mode DG, qui est induite par                       |     |

|      | l'inversion de volume et ne peut pas être expliquée par un modèle                    |     |

|      | classique de superposition des canaux                                                | 171 |

## Abbreviations and acronyms

1D, 2D, 3D Uni, Bi, Tri-Dimensional.

**BJT** Bipolar Junction Transistor.

**BOX** Buried OXide.

**BTE** Boltzmann Transport Equation.

**CMOS** Complementary MOS.

CYNTHIA Cylindrical Thin Pillar.

**DC** Direct Current.

**DD** Drift Difussion.

**DG** Double Gate.

**DGSOI** Double Gate SOI transistor.

**DIBL** Drain Induced Barrier Lowering.

**ELTRAN** Epitaxial Layer Transfer.

EMC Ensemble Monte Carlo.

**EME** Effective Mass Equation.

**EOT** Effective Oxide Thickness.

FDSOI Fully Depleted SOI Transistor.

**FET** Field Effect Transistor.

GAA Gate All Around transistor.

GeOI Germanium On Insulator.

**ITOX** High temperature Internal Oxidation.

ITRS International Technology Roadmap for Semiconductors.

**JFET** Junction Field Effect transistor.

**LDMOS** Lateral Double-Diffused MOS.

**LIGBT** Lateral Insulated Gate Bipolar Transistor.

MC Monte Carlo.

**MEMS** Micro Electro-Mechanical Systems.

MIS Metal Insulator Semiconductor.

**MODFET** Modulation-doped Field Effect Transistor.

MOS Metal Oxide Semiconductor.

**MR** Magnetoresistance.

**PDSOI** Partially Depleted SOI transistor.

**SCE** Short Channel Effects.

**SDE** Source Drain Engineering.

**SDE-DC** Source Drain Engineering and Doping Compensation.

**SSDOI** Strain Silicon Directly On Insulator.

SSi-GeOI Strain Silicon on Germanium On Insulator.

sSi/SiGeOI Strain Silicon on Silicon Germanium On Insulator.

**SET** Single Electron Transistor.

SG Single Gate.

SGSOI Single Gate SOI transistor.

**SHG** Second Harmonics Generation.

**SIMOX** Separation by Implantation of OXygen.

SIMOX MLD Modified Low Dose SIMOX.

**SOI** Silicon On Insulator.

**SOR** Succesive Over Relaxations.

**SR** Surface Roughness.

SSDOI Strain Silicon Directly On Insulator.

**ULSI** Ultra Large Scale of Integration.

**UTB** Ultra Thin Body.

**VCBM** Voltage-Controlled Bipolar MOS Device.

**VDMOS** Vertical Lateral double-diffused MOS.

VM Velocity Modulation.

VMT Velocity Modulation Transistor.

### Prologue

For many years, inside the Electronic World, the best way to explore the future has been to concoct it. Since in 1947 Dr. John Bardeen and Dr. William Shockley invented the transistor at Bell Labs, the Electronics has experimented a vertiginous advance. Six years after the revolutionary device saw the light, in 1954, Texas Instruments built the first transistorized radio receiver. In 1958, the American engineers Jack Kilby and Robert Noyce developed the first integrated circuit merging, in the same silicon chip, different components by means of gold connections: the first solid state circuit was born.

At the end of 1961 Dr. Steven Hofstein and Dr. Frederic Heiman, from RCA Princeton Lab., built the first operating MOSFET transistor. Although initially it was slower than the junction bipolar transistor, the MOSFET was smaller, cheaper and it needed less power to operate, allowing a higher number of transistors in the same area and reducing the power dissipation problems.

Currently most of the electronic integrated circuits are built with MOSFETs as basic component. The take off of the electronics industry has been exponential: adaptive automatic equalizers, the pocket calculator, the CD-ROM, computers on chip... The performance of the commercial applications has improved spectacularly due to the underlying increment in the device performance. This improvement is linked to the progressive transistor miniaturization, making possible a higher integration level, a higher operation speed and reducing the cost.

Nevertheless, the device miniaturization causes a set of problems with complex solution. Nowadays feature dimensions of the transistors are in the range of few atomic layers. The discrete nature of the matter and the quantum limitations make these effects, ignored a few years ago, to be included in the current design and

modelling.

This work studies the impact, chances and challenges of the decananometric miniaturization on the performance of the incoming transistor generation (45nm node [ITR06]).

Two are the main research task accomplished: