www.acsami.org Research Article

# Wafer-Scale Demonstration of BEOL-Compatible Ambipolar MoS<sub>2</sub> Devices Enabled by Plasma-Enhanced Atomic Layer Deposition

Alberto Martínez, Carlos Márquez, Francisco Lorenzo, Francisco Gutiérrez, Manuel Caño-García, Jorge Avila, José Carlos Galdón Gil, Ruben Ortega Lopez, Carlos Navarro, Luca Donetti, and Francisco Gámiz

Cite This: ACS Appl. Mater. Interfaces 2025, 17, 52902-52912

ABSTRACT: The relentless scaling of semiconductor technology demands materials beyond silicon to sustain performance improvements. Transition metal dichalcogenides (TMDs), particularly MoS<sub>2</sub>, offer excellent electronic properties; however, achieving scalable and CMOS-compatible fabrication remains a critical challenge. Here, we demonstrate a scalable and BEOLcompatible approach for the direct wafer-scale growth of MoS<sub>2</sub> devices using plasma-enhanced atomic layer deposition (PE-ALD) at temperatures below 450 °C, fully compliant with CMOS thermal budgets. This method enables the fabrication of MoS2-based devices directly on target substrates, eliminating material transfer while ensuring robust adhesion and integration with semiconductor processing. The resulting field-effect transistors (FETs) exhibit stable ambipolar behavior, consistent across semiconductor thickness variations and environmental conditions. Electrical characterization reveals minimal Fermi-level pinning, with Schottky barrier heights below 120 meV for both carriers, supporting a well-defined thermionic transport regime. Low-frequency noise measurements confirm flicker noise characteristics, typical of planar field-effect devices. Material conductivity is significantly enhanced through in situ, BEOL-compatible dielectric passivation or sulfur-atmosphere annealing. This work highlights the potential to directly fabricate, lithographically pattern, and encapsulate MoS2 devices for three-dimensional (3D) integration, fully compliant with silicon CMOS thermal constraints.

KEYWORDS: two-dimensional materials, molybdenum disulfide, atomic layer deposition, TMD transistors, CMOS integration, BEOL compatibility

## ■ INTRODUCTION

In recent decades, the push for higher transistor densities has driven transformative advancements in electronic devices. As transistor nodes shrink below 2 nm, innovative architectures such as nanosheet, forksheet, and complementary FET (C-FET) designs have been proposed to enhance device performance and overcome the physical limitations of conventional scaling. These architectures exploit the vertical stacking of n-type and p-type MOSFETs to reduce lateral dimensions, requiring the development of novel materials and processes to address challenges such as carrier tunneling and other quantum effects.

Transition metal dichalcogenides (TMDs), a prominent family of two-dimensional (2D) materials, have emerged as promising candidates for next-generation electronic and optoelectronic devices. 1,2 Their CMOS-compatible bandgaps, large effective masses (which suppress source-to-drain tunneling), and atomic-scale tunability provide distinct advantages for scaling and three-dimensional integration.<sup>3,4</sup> These properties have already enabled remarkable progress in interconnect scaling for back-end-of-line (BEOL) processes

June 18, 2025 Received: Revised: August 26, 2025 Accepted: September 1, 2025 Published: September 5, 2025

or 2D barriers and passivation layers. Moreover, integrating 2D materials into 3D architectures for logic memory cells and memristors<sup>8</sup> holds considerable potential for addressing system-on-chip (SoC) challenges. In addition, recent investigations are exploring the influence of different underlying materials on MoS<sub>2</sub> films deposited by sputtering for the development of 2D-CFETs.

Despite these promising advancements, the integration of TMDs into semiconductor fabrication processes remains challenging. 10,11 Conventional synthesis methods, including mechanical exfoliation and high-temperature techniques (e.g., chemical vapor deposition at T > 450 °C), are not totally suitable for large-scale production or CMOS-compatible workflows.<sup>2</sup> Moreover, defects and impurities in TMDs often compromise device performance, resulting in phenomena such as Fermi-level pinning, Schottky barrier formation, high contact and sheet resistances, current hysteresis, or Coulomb scattering. 12-15

A critical challenge lies in effective doping control. Pristine MoS<sub>2</sub> and WS<sub>2</sub>, two of the most promising TMD materials, theoretically exhibit ambipolar behavior. <sup>16</sup> However, in practice, they predominantly demonstrate n-type behavior.<sup>17</sup> Sulfur vacancies, interface states, 16,18-20 and surface carbon atoms<sup>21</sup> are key contributors to Fermi-level pinning near the conduction band of the semiconductor.

On the other hand, achieving reliable p-type operation with sulfur as the chalcogen remains a significant challenge.<sup>2</sup> Success has been achieved in limited cases, such as chemical doping<sup>23</sup> or through metal-assisted growth techniques.<sup>24</sup> The presence of adsorbates like H<sub>2</sub>O and O<sub>2</sub> has also been reported to induce p-type behavior, although these effects are typically removed after material or device annealing.<sup>25</sup>

The experimental demonstration of ambipolar MoS<sub>2</sub> devices is rare, with reports mainly limited to exfoliated flakes transferred onto PMMA layers<sup>26</sup> or under ionic liquid gating.<sup>2</sup> These infrequent occurrences are attributed to substrateinduced Fermi-level pinning, which limits the current flow in any of the branches.1

While notable progress has been made in device performance through the use of interfacial insulators (e.g., hexagonal boron nitride),<sup>28</sup> vertically stacked heterostructures,<sup>25</sup> encapsulation techniques, several challenges persist. 10 These challenges include scalable, wafer-level fabrication, direct growth of 2D materials at CMOS-compatible temperatures for 3D integration, and doping optimization to achieve highperformance p-type and n-type devices using the same material. 18,30,31

Atomic layer deposition (ALD), a cyclic thin-film deposition technique widely used in the industry for producing thicknesscontrolled and uniform dielectric films, has recently garnered considerable attention for the synthesis of TMDs.<sup>32</sup> Plasmaenhanced (PE)-ALD, which employs highly reactive radicals and ionic species, promises to enable reduced growth temperatures and greater flexibility in tailoring the gas-phase chemistry to produce specific film characteristics.<sup>33</sup> Additionally, PE-ALD often outperforms chemical vapor deposition (CVD) in terms of precise thickness control, film conformality, and uniformity. These aspects make PE-ALD-grown TMDs well-suited to meet the semiconductor industry's requirements for large-area coverage and low thermal budget synthesis. Notably, MoS<sub>2</sub>-grown at temperatures as low as 100 °C has been demonstrated, allowing precise thickness control and tunable material morphology. 34-36 Further advancements have

enabled chemical doping for p-type devices,  $^{23}$  contact optimization,  $^{37}$  and front-gate dielectric deposition for CMOS cointegration. PE-ALD-grown MoS<sub>2</sub> has shown complete wafer coverage with satisfactory uniformity on 200 mm substrates, such as alkali-free glass, 40 undoped silicate glass, and Al<sub>2</sub>O<sub>3</sub> wafers.<sup>41</sup>

Despite these advancements, ALD processes typically yield polycrystalline layers with point defects and grain boundaries, often requiring postannealing treatment to enhance crystallinity. 36,37,39,42 The high temperature of the annealing process typically exceeds the thermal budget constraints. Moreover, challenges such as material delamination during lithography processing or high contact and sheet resistances remain substantial, primarily due to the low adhesion energy of van der Waals layers and the limitations of low-temperature synthesis routes. 38,43

In this work, we demonstrate the direct, wafer-scale, CMOScompatible (<450 °C) fabrication of crystalline molybdenum disulfide (MoS<sub>2</sub>) back-gated transistors using plasma-enhanced atomic layer deposition. Devices with varying material thicknesses were systematically characterized both morphologically and electrically.

The low-temperature direct growth on prepatterned pad structures eliminates the need for material transfer, simplifying and accelerating the process. This method enables the formation of crystalline films with ambipolar operation (both p-type and n-type) due to the absence of Fermi level pinning, without requiring postgrowth thermal annealing, ensuring full CMOS compatibility. The ambipolar behavior on transistors offers significant versatility for advanced applications such as reconfigurable devices, 44 complementary logic, and energyefficient designs, while also simplifying fabrication by eliminating the need for separate doping or distinct materials. In fact, polarity switching via gate bias transistors, based on black phosphorus, have been demonstrated with promising applications in hardware security circuits.<sup>45</sup>

Furthermore, we provide clear experimental evidence of flicker noise, a characteristic low-frequency noise commonly observed in electronic devices, in these back-gated transistors.

To the best of our knowledge, this is the first report of largearea direct MoS<sub>2</sub> deposition that consistently exhibits ambipolar behavior across multiple devices fabricated at CMOS-compatible temperatures.

#### EXPERIMENTAL METHODS

Substrates Preparation and Devices Photolithography. The material was synthesized at the wafer scale directly on prepatterned source and drain metal electrodes, ensuring better adhesion and minimizing the risk of delamination during subsequent lithographic steps. For the metal stack, ultraviolet (UV) photolithography was employed to define the source and drain patterns directly on the Si/ SiO<sub>2</sub> substrate with a 90 nm thick oxide layer. Both wet etching and lift-off processes were used to define the device pads, with the lift-off process showing superior resolution for submicron channel lengths. Metal evaporation was performed via thermal physical vapor deposition (PVD, Leybold UNIVEX 250) under a vacuum of 8 × 10<sup>-5</sup> mbar to deposit Cr/Au electrodes (10/90 nm).

Following metal patterning, MoS<sub>2</sub> was deposited using PE-ALD, as described below. In case of passivation, Si<sub>3</sub>N<sub>4</sub> encapsulation layer was deposited at 300 °C using bis(tert-butylamino)silane (BTBAS,  $SiH_2(NHtBu)_2$ ) as the silicon precursor and  $N_2$  plasma as the coreactant. UV photolithography was repeated to perform a dry etching process that removed the MoS2 material outside the channel region between the source and drain contacts. This was achieved

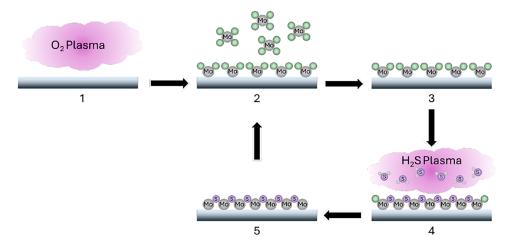

Figure 1. Schematic representation of the plasma-enhanced atomic layer deposition process for MoS<sub>2</sub>.

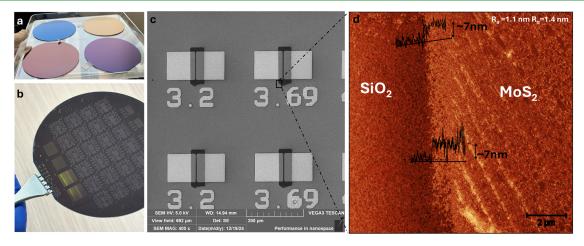

Figure 2. (a) Si/SiO<sub>2</sub> wafers were coated with MoS<sub>2</sub> layers of varying thicknesses, deposited using different numbers of cycles in PE-ALD. The synthesis process was conducted at a temperature of 400 °C, with the number of ALD cycles varying from 10 (magenta) to 40 (blue). (b) Photograph of a 100 mm Si/SiO<sub>2</sub>/MoS<sub>2</sub> wafer after photolithography processing. Various device design layouts, including van der Pauw structures, back-gate transistors, capacitors, and sensors, were fabricated. (c) A scanning electron microscopy (SEM) image showing back-gated devices with varying channel dimensions. Cr/Au was used for the deposition of square pads. (d) Atomic force microscopy (AFM) topography of a SiO<sub>2</sub>/MoS<sub>2</sub> region, highlighting the distinction between SiO<sub>2</sub> and MoS<sub>2</sub> areas. The accompanying profiles indicate a MoS<sub>2</sub> layer thickness of approximately 7 nm in the etched region for the case of 40 ALD-cycles.

using fluorine-based chemistry (SF<sub>6</sub>/Ar: 5/45 sccm) at a power of 50 W and a pressure of 6 mTorr.

MoS<sub>2</sub> Synthesis. MoS<sub>2</sub> deposition was performed using plasmaenhanced atomic layer deposition on an Oxford Instrument FlexAL ALD system, utilizing bis(t-butyl)(dimethylamido)molybdenum(IV)  $(Mo(N^tBu)_2(NMe_2)_2)$  and hydrogen sulfide  $(H_2S)$  as precursors. The deposition process, summarized in Figure 1, involved the following steps:

- 1. Substrate Cleaning: A remote O2 plasma treatment was applied for 1 min to clean the Si/SiO<sub>2</sub>/Cr/Au prepatterned substrate, effectively removing residual organic contaminants.

- 2. Precursor Dosing:  $Mo(N^tBu)_2(NMe_2)_2$  was introduced as reactive gas, reacting with the substrate to form a thin chemisorbed layer. The Mo precursor was stored in an electropolished stainless steel bubbler (Pot) at 60 °C to ensure sufficient vapor pressure. The precursor dose was introduced at a pressure of 80 mTorr for 2 s.

- 3. Purge Step: The chamber was purged with Argon gas for 6 s at pressures below 0.1 mTorr (full pump), removing any unreacted precursor molecules and byproducts.

- 4. Sulfidation: Reactive gas (H<sub>2</sub>S/H<sub>2</sub>) was introduced, reacting with the Mo precursor under remote plasma to form MoS<sub>2</sub>. Plasma was activated using 100 W RF power, with a gas flow of

- 40 sccm Ar, 8 sccm H<sub>2</sub>S, and 2 sccm H<sub>2</sub> for 30 s, while maintaining a pressure below 0.1 mTorr to sustain the plasma.

- 5. Final Purge: A final Argon purge was conducted for 4 s to eliminate any residual unreacted species and byproducts from the reaction chamber.

This cycle was repeated to achieve the desired MoS<sub>2</sub> film thickness. The growth temperature inside the chamber was maintained at 400 °C throughout the process.

Characterization Setup. For structural characterization, atomic force microscopy (AFM), Raman spectroscopy, and X-ray photoelectron spectroscopy (XPS) were employed. AFM was performed using an NTMDT NTEGRA system in semicontact mode with metallic tips. Raman spectra were acquired with a Witec alpha300 system using 532 nm laser excitation, a laser power of 20 mW, a 100× objective, and a grating of 600 lines per mm. Each spectrum was accumulated over 50 scans. XPS measurements were conducted using a Kratos Axis Ultra-DLD spectrometer with Al Kα (1486.6 eV) radiation.

For electrical characterization, a semiconductor analyzer (Keysight B1500) and various temperature- and pressure-controlled probe stations (Suss PA-300PS and Janis cryostat) were utilized. Transfer characteristics  $(I_D-V_G)$  were measured using a sweep from -42 to +42 V and back, with 1002 points per curve and a sweep duration of 110 s. A 1-s hold time was applied at the initial gate voltage before the sweep. Low-frequency noise measurements were performed using a low-noise current amplifier connected to a software-based spectrum analyzer.

#### RESULTS AND DISCUSSION

Structural and Morphological Characterization. Figure 2a shows a photograph of the as-synthesized samples at the wafer level, highlighting the high MoS<sub>2</sub> homogeneity and the noticeable color variations corresponding to the different number of ALD cycles employed. Notably, the uniform color of MoS<sub>2</sub> across the wafer demonstrates its significant homogeneity. Figure 2b presents a directly lithographed wafer featuring various devices and structures prepared for electrical characterization. Different back-gate transistors with varying drain-source lengths and widths, as well as multiple van der Pauw structures and designs for biosensors, were successfully fabricated. Significantly, no material delamination was observed in any of the more than 20 wafers fabricated for this work. Figure 2c illustrates the scanning electron microscopy (SEM) characterization of several devices, where the contacts and TMD material are distinguishable. A zoomedin atomic force microscopy (AFM) view of a region containing both SiO<sub>2</sub> and MoS<sub>2</sub> is provided in Figure 2d. In this etched area, the thickness of the MoS<sub>2</sub> layer is determined to be around 7 nm. It is important to note that this profile thickness may exceed the actual MoS<sub>2</sub> layer thickness, as some SiO<sub>2</sub> substrate may have been etched during the reactive-ion process. Figure S1 shows a zoomed-in area of a MoS2 region, corroborating a MoS<sub>2</sub> layer formed by grains approximately 7 nm in thickness and less than 100 nm in diameter. The MoS<sub>2</sub> region exhibits an average surface roughness  $(R_a)$  of 1.1 nm and a root-mean-square roughness  $(R_q)$  of 1.4 nm. This grain size and layer roughness are consistent with the expected results for low-temperature ALD-grown MoS<sub>2</sub> materials, which exhibit smaller grain sizes compared to the CVD case. 32,38,40,41

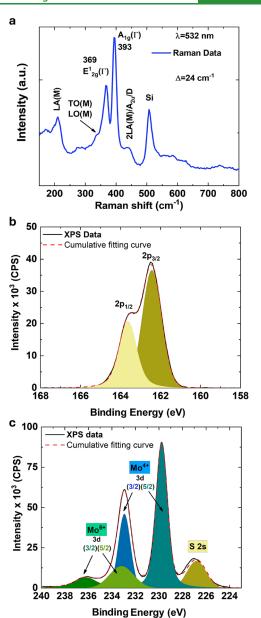

Figure 3a shows the Raman spectrum of the  $MoS_2$  layer excited by a 532 nm laser under ambient conditions. The spectrum reveals two characteristic Raman bands at 369 and 393 cm<sup>-1</sup>, corresponding to the in-plane  $(E_{2g}^1)$  and out-of-plane  $(A_{1g})$  vibrational modes, respectively, demonstrating the crystalline nature of the  $MoS_2$  layer. The peak separation  $(\Delta)$  is approximately 24 cm<sup>-1</sup> across the  $MoS_2$  layer, consistent with multilayer  $MoS_2$ ,  $^{46,47}$  and also in agreement with the  $MoS_2$  thickness measured by the AFM topography.

Additionally, the Raman spectrum exhibits a peak centered at 440 cm<sup>-1</sup>, which is attributed to a combination of factors:<sup>47</sup>

- The double frequency of the LA(M) mode (observed around 210 cm<sup>-1</sup>), which is related to disorder-induced Raman scattering or increased partial oxidation in the MoS<sub>2</sub> samples. This phenomenon has also been reported in other ALD-grown MoS<sub>2</sub> studies. <sup>23,35,40</sup>

- 2. The first-order optical phonon peak  $A_{2u}$ , associated with asymmetric translations of Mo and S atoms along the c-axis.<sup>49</sup>

- The D peak, attributed to Mo—S vibrations in oxysulfide species.

These features are further linked to the presence of bridging Mo-S-Mo species in reduced molybdenum compounds or  $Mo^{6+}$  oxysulfide species. Additionally, peaks corresponding to the longitudinal optical (LO) and transverse optical (TO) phonon branches are also observed. No changes in the

**Figure 3.** (a) Raman spectrum of the synthesized  $MoS_2$  under 532 nm light excitation. High-resolution XPS spectrum: (b) S 2p core. (c) Mo 3d core.

Raman characterization were observed before and after the device photolithography process. Figure S2 presents Raman spectra measured across the entire wafer, confirming the previously noted uniformity of the  $MoS_2$  film.

X-ray photoelectron spectroscopy (XPS) was performed to measure the binding energies of sulfur (S, Figure 3b) and molybdenum (Mo, Figure 3c) atoms. The S 2p peaks at 162.4 and 163.6 eV (Figure 3b) are attributed to the spin—orbit components S  $2p_{3/2}$  and S  $2p_{1/2}$ , with a  $2p_{1/2}$ : $2p_{3/2}$  ratio of 0.6 (slightly higher than the ideal 0.5 ratio expected for S ions with a single binding state to Mo ions<sup>36</sup>) and a spin—orbit splitting of 1.2 eV. Figure 3c displays two broad peaks at approximately 229.7 and 232.9 eV, corresponding to the main doublet Mo  $3d_{5/2}$  and Mo  $3d_{3/2}$  of the Mo<sup>4+</sup> chemical state, with a  $3d_{3/2}$ : $3d_{5/2}$  ratio of 0.46 and a spin—orbit splitting of 3.1 eV. S1,52 Additionally, a minor peak at 226.8 eV is assigned to the S 2s component. These results, along with the wide XPS

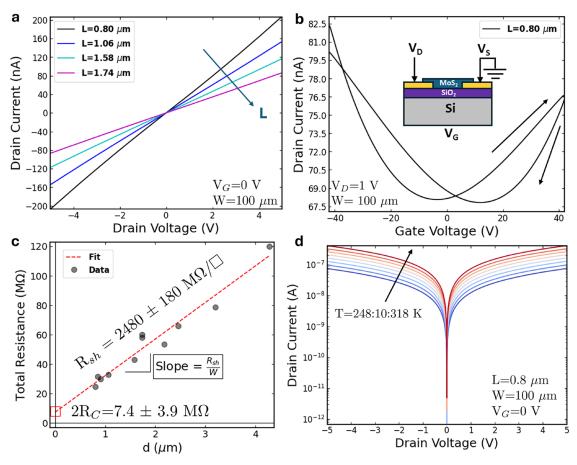

Figure 4. (a) Drain current versus drain voltage characteristic for devices with  $W=100~\mu\mathrm{m}$  and varying channel lengths (L). (b) Transfer characteristics  $(I_{\mathrm{D}}-V_{\mathrm{G}})$  for a device with  $L=800~\mathrm{nm}$ . The experimental setup and device cross-section are shown in the inset. (c) Extrapolation of contact resistance  $(R_{\mathrm{c}})$  and sheet resistance  $(R_{\mathrm{sh}})$  for a series of devices with different contact distances or pitch (d) and  $W=100~\mu\mathrm{m}$ . (d) Output characteristics  $(I_{\mathrm{D}}-V_{\mathrm{D}})$  at various temperatures ranging from 248 to 318 K.

spectrum in Figure S3a, are consistent with previously reported binding energy values for MoS<sub>2</sub>.<sup>53</sup> Smaller contributions at approximately 233.2 and 236.2 eV correspond to binding energies typically attributed to Mo<sup>6+</sup> oxidation states, indicating the presence of suboxide species.<sup>52</sup> The Mo<sup>6+</sup> peaks suggest oxygen incorporation into the synthesized MoS<sub>2</sub> film, <sup>52,54</sup> which is corroborated by the Raman results mentioned earlier and the Mo–O peak observed in the O 1s spectrum of Figure S3b. These findings imply the presence of defects that distort the stoichiometry of the MoS<sub>2</sub> films, consistent with observations in other ALD-grown MoS<sub>2</sub> samples under similar growth conditions.<sup>35,36</sup> However, Mo<sup>5+</sup> states, which are also commonly associated with oxide incorporation in CVD-grown MoS<sub>2</sub>, <sup>19</sup> are not detected in these samples.

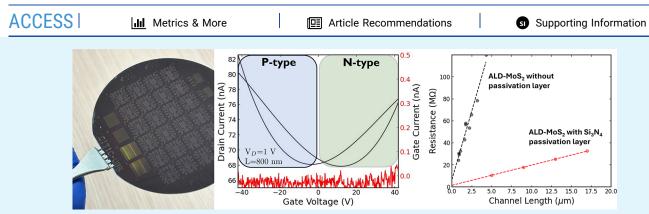

**Electrical Characterization.** The output  $(I_{\rm D}-V_{\rm D})$  and transfer  $(I_{\rm D}-V_{\rm G})$  characteristics of back-gated devices with varying channel lengths (L) and a fixed channel width (W) of 100  $\mu$ m are presented in Figure 4a,b, respectively. The output characteristics exhibit linear behavior and symmetrical current responses for both positive and negative voltages, indicative of low Schottky barrier contacts. <sup>19,20</sup> Furthermore, as the channel length decreases, the output current increases, consistent with channel-limited transport. This behavior contrasts with the contact-limited injection observed in the p-branch of other ALD-grown devices. <sup>38</sup>

The transfer characteristics  $(I_{\rm D}-V_{\rm G})$  measured in the devices, following the schematic shown in the inset of Figure 4b, demonstrate the modulation of channel resistance with the applied back-gate voltage. The double-swept curves exhibit hysteresis, which is commonly attributed to charge trapping and detrapping phenomena associated with defects. The back-gate current (Figure S4) remains significantly lower than 100 pA, indicating that gate leakage does not substantially affect the observed behavior. Notably, these devices exhibit clear ambipolar performance, with both hole (negative gate voltages) and electron (positive gate voltages) conduction. As introduced, such behavior is rare in  ${\rm MoS}_2$  devices, regardless of the synthesis method, where n-type characteristics are predominantly observed. S6,57

The ambipolar behavior here reported was consistently observed across all measured devices, regardless of the number of ALD cycles (ranging from 20 to 60) (Figure S5) and applied drain voltages (Figure S6).

Despite this promising behavior, certain limitations, such as a low on/off current ratio and low current levels, are observed. These performance constraints may be related to several factors, including Schottky barriers, carrier population limitations due to defect trapping effects, reduced current modulation with back-gate voltage in thick materials, or Fermilevel pinning at the SiO<sub>2</sub> substrate. <sup>18</sup>

To further elucidate these phenomena, the Transmission Line Model (TLM) was employed to extract both the sheet

resistance and contact resistance of the devices. Figure 4c shows the total resistance as a function of contact separation distance (d) at zero back-gate voltage. From this analysis, the y-intercept yields the total contact resistance ( $2R_c \approx 7.4 \text{ M}\Omega$ ), while the slope corresponds to the sheet resistance of the MoS<sub>2</sub> channel ( $2480 \text{ M}\Omega/\square$ ). The dependence of the resistance on the full range of gate voltages is presented in Figure S7.

These results were corroborated using Four-Contact characterization performed on the as-synthesized materials. Devices synthesized at two different temperatures (350 and 400 °C) were characterized for varying numbers of ALD cycles (Figure S8). A clear trend of decreasing sheet resistance with increasing ALD cycles and lower synthesis temperatures was observed. It is important to note that material resistivity typically decreases with lower synthesis temperatures, although this often comes at the expense of crystallinity. In this case, sheet resistances as low as 130 MQ/ $\square$  were achieved, values in good agreement with those reported for ALD-grown WS<sub>2</sub><sup>31</sup> and MoS<sub>2</sub> devices. Considering the AFM-measured thicknesses, the corresponding resistivity ( $\rho$ ) is approximately  $10^2 \Omega$  cm for as-synthesized samples with 75 ALD cycles at 350 °C.

Figure 4d illustrates the expected increase in current levels at elevated temperatures, according to the typical behavior of semiconductors. Symmetry between positive and negative  $V_{\rm D}$  voltages is still observed. This temperature-dependent characterization is first employed to investigate the Schottky barrier height at the metal/semiconductor junction. In the thermionic emission regime, the electrical transport is described by  $^{16,59,60}$

$$I_{\rm D} = AA^*T^2 e^{-(q/k_{\rm B}T)(\phi_{\rm B} - (V_{\rm D}/n))}$$

(1)

where A is the diode area,  $A^*$  is the Richardson constant, q is the elementary charge,  $k_{\rm B}$  is the Boltzmann constant,  $\phi_{\rm B}$  is the Schottky barrier height, n is the ideality factor, and T is the temperature. The slope  $S(V_{\rm D})$  is obtained by extrapolating  $\ln(I_{\rm D}/T^2)$  versus 1000/T for different  $V_{\rm D}$ .

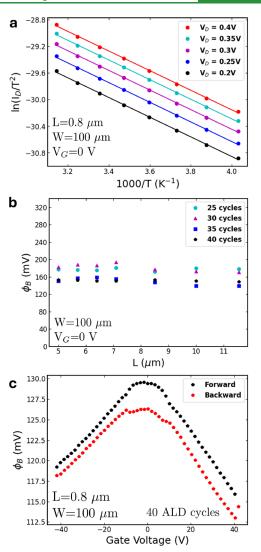

Figure 5a shows the Arrhenius plot for a device with a length of 800 nm, width of 100  $\mu$ m, and varying drain voltages. The Schottky barrier height is obtained from the extrapolated slope at zero  $V_{\rm D}$  (S<sub>0</sub>)

$$S_0 = -\frac{q\Phi_b}{1000k_B} \tag{2}$$

Figure 5b presents the Schottky barrier heights extrapolated for devices with different channel lengths and varying numbers of ALD cycles, measured at zero gate voltage. Values ranging from 150 to 200 mV are observed across all cases. Devices with a lower number of ALD cycles exhibit higher Schottky barrier heights, suggesting a correlation with layer thickness. The Schottky barrier height presents no dependence on the device length. Figure 5c illustrates the  $\Phi_{\rm B}$ –V $_{\rm G}$  relationship, which shows a linear and decreasing dependence on  $V_{\rm G}$  for both electron and hole branches. Slight differences between forward and backward bias sweeps are observed. Same results in other MoS $_2$  thicknesses have been shown in Figure S9.

The observed symmetry in the Schottky barriers for electrons and holes is consistent with the ambipolar behavior and, consequently, with the absence of strong Fermi-level pinning. However, the relatively low extracted barrier heights are difficult to attribute solely to gate-induced band bending and thermionic emission, especially considering the reported bandgap for  $MoS_2$  (1.29–1.90 eV).<sup>61</sup> This discrepancy

**Figure 5.** (a) Arrhenius plot showing  $\ln(I_{\rm D}/T^2)$  versus 1000/T curves for various  $V_{\rm D}$  values for a device with  $L=0.85~\mu{\rm m}$  and  $W=100~\mu{\rm m}$ . (b) Extrapolated  $\Phi_{\rm B}$  for devices with different numbers of ALD cycles and varying channel lengths. (c) Extrapolated  $\Phi_{\rm B}$  as a function of gate voltage. Unless otherwise indicated, the samples were synthesized with 40 ALD cycles.

suggests that additional mechanisms may significantly influence the effective barrier height.

To gain further insight into the origin of this behavior, we independently analyzed the temperature dependence of the contact resistance ( $R_c$ ) and sheet resistance ( $R_{\rm sh}$ ), as detailed in Supporting Note 1 (Figures S10–S16). Sheet conductivity is consistent with a thermally activated nearest-neighbor hopping conduction mechanism, which is typically indicative of charge transport through localized states. Although the MoS<sub>2</sub> films are grown in a crystalline phase, structural disorder (possibly arising from chalcogen vacancies, grain boundaries, or other point defects) may introduce localized states within the bandgap. These defects may cause band tailing and bandgap narrowing. This interpretation is supported by the temperature dependence of  $R_c$  which aligns with the thermionic emission model  $^{59}$  and yields Schottky barriers consistent with the previously extracted in Figure 5.

Another relevant parameter is the field-effect mobility ( $\mu_{FE}$ ), which is given by

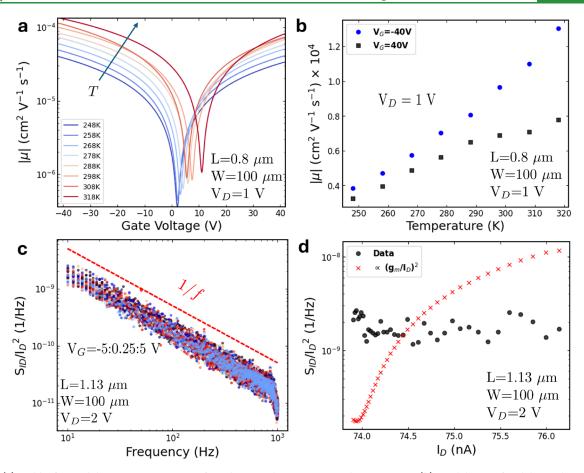

Figure 6. (a) Field effect mobility versus temperature for a device with  $L=0.8~\mu{\rm m}$  and  $W=100~\mu{\rm m}$ . (b) Modulation of mobility with temperature. (c) Normalized low-frequency noise spectra of a device with  $L=1.13~\mu{\rm m}$  and  $W=100~\mu{\rm m}$  at different back-gate voltages ranging from -5 to +5 V, showing a clear 1/f characteristic. The device is operated in the ON state with a source-to-drain bias of 2 V. (d) Normalized spectral noise (black circles) and  $\propto (g_{\rm m}/I_{\rm D})^2$  fit versus drain current obtained at different gate voltages.

$$\mu_{\rm FE} = \frac{L}{W C_{\rm ox} V_{\rm D}} \cdot \frac{{\rm d}I_{\rm D}}{{\rm d}V_{\rm G}} \end{dsuperpose} \end$$

where  $C_{ox}$  is the oxide capacitance per unit area. Figure 6a shows the  $\mu$ - $V_{\rm G}$  curves on a logarithmic scale for different temperatures. Linear dependence of  $\mu$  on  $V_{\rm G}$  is evident over a certain range, with a continuous increase in mobility. This  $V_{G}$ dependent mobility has been previously documented in 2D materials and can be explained by two effects: First, as carrier concentration increases, screening gets stronger, reducing the scattering potential and thus increasing the Coulomb impuritylimited mobility. 63 Second, as  $V_{\rm G}$  increases, more trap states in the material are filled, allowing more carriers to remain free to move, which further enhances mobility.<sup>64</sup> In all cases, the mobility values are consistent with those reported for ALD-grown 2D materials in the literature, <sup>23,37,43</sup> as confirmed by benchmarking presented in the Supporting Information (Tables S1 and S2). The dependence of mobility on temperature, as depicted in Figure 6b, aligns with a traplimited and charged-impurity Coulomb scattering mobility regimes<sup>63,65</sup> which can be in agreement with thermally activated hopping transport mechanism. The low mobility indicates a high density of trap states, which also contribute to the hysteretic behavior observed in the transfer characteristic shown in Figure 4b. This hysteresis arises from the trapping and detrapping of charge carriers, whose potential adds to that of the back-gate. 13,19,60

Another critical parameter, essential for benchmarking new devices, is the low-frequency noise (LFN). The normalized noise spectrum for various back-gate biases is shown in Figure 6c. As depicted, the device exhibits 1/f noise characteristics, demonstrating a flicker noise due to charge carrier trapping and detrapping at defect states or impurities in the material.<sup>67</sup>

Figure 6d presents the normalized device noise as a function of the drain current for varying gate voltages. The noise shows minimal dependence on the drain current, ruling out Hooge mobility fluctuations within this voltage—current range. Similarly, carrier number fluctuations are excluded, as the noise remains flat even when  $(g_{\rm m}/I_{\rm D})^2$  increases. As detailed in Supporting Note 2, the data are fitted using a combined carrier number fluctuation and correlated mobility fluctuation (CNF-CMF) model, yielding a surface trap state density on the order of  $10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> (Figure S17). However, the constant normalized noise level observed across devices with varying channel lengths suggests significant resistance fluctuations at the metal—semiconductor interface (Figure S18), indicating a contact-dominated regime within these voltage ranges. To

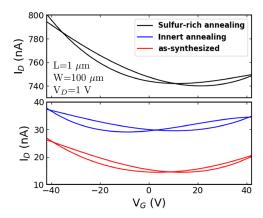

To investigate whether thermal annealing affects one of the carrier branches (holes or electrons) or the material resistivity, annealing processes were performed at a maximum temperature of 700 °C for 15 min in both sulfur-rich and inert gas environments at low pressure (3 Torr). Figure 7 shows that sulfur-rich annealing increases the current levels (decreases

Figure 7. Transfer characteristics of  $MoS_2$  devices before and after sulfur-rich and inert annealing processes carried out at 700  $^{\circ}$ C and low pressure for 15 min.

material resistivity) while partially suppressing the n-type branch, in line with sulfur vacancy suppression. In contrast, inert gas annealing results in only a slight improvement in the current levels. Notably, the p-type branch remains unaffected by the annealing process, with current levels increasing, thereby demonstrating persistent ambipolar behavior and ruling out any influence from chemi-absorbed impurities such as  $O_2$  or  $H_2O$ .

The preservation of ambipolar behavior, regardless of ambient-related effects, was further corroborated using a complementary passivation approach. A thin Si<sub>3</sub>N<sub>4</sub> layer was sequentially deposited by ALD after MoS2 growth, avoiding any exposure to ambient conditions. As shown in Figure S19a, the passivated devices retained their ambipolar characteristics, confirming that the behavior is intrinsic and not dominated by surface adsorbates. At the same time, the devices exhibited enhanced performance, including a consistent reduction of sheet resistance by at least 1 order of magnitude (Figure S19b) and a noticeable decrease in hysteresis, suggesting improved material quality and reduced trapping effects due to surface protection. Additionally, artificial light exposure and vacuum ambient conditions were evaluated during the electrical characterization of the devices, revealing only slight variations in the current levels, as shown in Figure S20.

### CONCLUSIONS

This work demonstrates the direct wafer-scale fabrication of ambipolar  $MoS_2$  back-gated FETs at BEOL-compatible temperatures using plasma-enhanced ALD. The devices exhibit stable ambipolar behavior, low Schottky barrier heights, and minimal Fermi-level pinning, enabling efficient operation in both n- and p-type regimes. An extensive transport analysis reveals thermionic emission as the dominant mechanism, with structural disorder and defect-induced states facilitating balanced electron and hole injection.

While these results establish the potential of MoS<sub>2</sub>-based devices for 3D integration within silicon CMOS technology, further improvements are needed to enhance performance and integration. Ongoing efforts targeting defect passivation through in situ, BEOL-compatible dielectric encapsulation or sulfur-rich annealing have demonstrated promising results improving material conductivity. Additionally, engineering of gate dielectric and contact interfaces is expected to reduce interface trap densities and contact resistance, enabling higher mobility and better switching characteristics. Combined with

scalable device patterning, these strategies will help realize energy-efficient, reconfigurable logic circuits and advanced CMOS-compatible architectures. The insights and methodologies presented here provide a strong foundation for the continued advancement of 2D-material-based electronics.

#### ASSOCIATED CONTENT

# Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.5c12014.

AFM topography of  ${\rm MoS}_2$  grains; Raman wafer mapping and average spectra; XPS survey and O-1s spectra; transfer characteristics and leakage currents; device statistics and Neutral Charge Point trends; output/transfer curves at varied biases; contact and sheet resistance vs gate voltage; sheet resistance and current vs synthesis conditions; temperature-dependent transfer and Schottky barrier data; transport mechanism analysis; ALD-grown TMD device benchmarking; low-frequency noise and trap density; in situ dielectric passivation improvements; light/dark and air/vacuum device responses (PDF)

#### AUTHOR INFORMATION

# **Corresponding Author**

Carlos Márquez — Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain; orcid.org/0000-0003-0159-9951; Email: carlosmg@ugr.es

### **Authors**

Alberto Martínez - Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain Francisco Lorenzo - Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain Francisco Gutiérrez – Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain Manuel Caño-García - Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain Jorge Avila - Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain José Carlos Galdón Gil - Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain Ruben Ortega Lopez - Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain; orcid.org/0009-0004-6522-8273 Carlos Navarro – Nanoelectronics Graphene and 2D

© orcid.org/0009-0004-6522-8273

Carlos Navarro — Nanoelectronics Graphene and 2D

Materials Laboratory, CITIC-UGR, Department of

Electronics, University of Granada, Granada 18014, Spain

Luca Donetti — Nanoelectronics Graphene and 2D Materials

Laboratory, CITIC-UGR, Department of Electronics,

University of Granada, Granada 18014, Spain;

© orcid.org/0000-0002-5189-867X

Francisco Gámiz – Nanoelectronics Graphene and 2D Materials Laboratory, CITIC-UGR, Department of Electronics, University of Granada, Granada 18014, Spain

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.5c12014

#### **Author Contributions**

<sup>†</sup>A.M. and C.M. contributed equally to this work. A.M. and C.M. wrote the initial manuscript. C.M. and J.C.G. performed the synthesis of the MoS<sub>2</sub> films. A.M., C.M., and C.N. conducted the electrical measurements and analyzed the data. C.M. and F.L. performed the morphological measurements. FG and MCG carried out the lithography processes. C.N., R.O., J.A. and L.D. contributed to the writing and editing of the manuscript. C.M. and F.G. supervised the project and provided guidance on the results. All authors reviewed and approved the final manuscript.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This research was partially funded by The C-ING-357-UGR23 project, supported by the Andalusian University, Investigation and Innovation Council, and the EU FEDER Andalucia 2021-2027, and the Spanish projects MICIU/AEI PID2023-152467OA-I00, MCIN/AEI PID2021-128547OB-I00, and MICIU/AEI PLEC2022-009381, with backing from the European Union NextGeneration EU/PRTR. M.C. acknowledges the financial support from the CONCEPT-2D MSCA project (Grant Agreement No. 101062995). The +QCHIP TSI-069100-2023-0003, HORIZON-JU-GH-EDCTP3-2023-01 (EPOCA Grant 101145795) and HORIZON-JU-Chips-2023-RIA-CPL-2 (FAMES ID 101182279) projects are also acknowledged for their financial support. Funding for open access charge: Universidad de Granada / CBUA.

# REFERENCES

- (1) Yao, J.; Yang, G. All-2D architectures toward advanced electronic and optoelectronic devices. *Nano Today* **2021**, *36*, No. 101026.

- (2) Akinwande, D.; Huyghebaert, C.; Wang, C.-H.; Serna, M. I.; Goossens, S.; Li, L.-J.; Wong, H.-S. P.; Koppens, F. H. Graphene and two-dimensional materials for silicon technology. *Nature* **2019**, *573*, 507–518.

- (3) Zeng, S.; Liu, C.; Zhou, P. Transistor engineering based on 2D materials in the post-silicon era. *Nat. Rev. Electr. Eng.* **2024**, *1*, 335–348

- (4) Jayachandran, D.; Pendurthi, R.; Sadaf, M. U. K.; Sakib, N. U.; Pannone, A.; Chen, C.; Han, Y.; Trainor, N.; Kumari, S.; Mc Knight, T. V.; Redwing, J. M.; Yang, Y.; Das, S. Three-dimensional integration of two-dimensional field-effect transistors. *Nature* **2024**, *625*, 276–281.

- (5) Lo, C. L.; Helfrecht, B. A.; He, Y.; Guzman, D. M.; Onofrio, N.; Zhang, S.; Weinstein, D.; Strachan, A.; Chen, Z. Opportunities and challenges of 2D materials in back-end-of-line interconnect scaling. *J. Appl. Phys.* **2020**, *128*, No. 080903.

- (6) Naylor, C. H.; Maxey, K.; Jezewski, C.; O'Brien, K. P.; Penumatcha, A. V.; Kavrik, M. S.; Agrawal, B.; Littlefield, C. V.; Lux, J.; Barley, B.; Weber, J. R.; Gupta, A. S.; Dorow, C. J.; Arefin, N.; King, S.; Chebiam, R.; Plombon, J.; Clendenning, S. B.; Avci, U. E.; Kobrinsky, M.; Metz, M. In 2D Materials in the BEOL, 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits); IEEE, 2023; pp 1–2.

- (7) Bhattacharjee, S.; Caruso, E.; McEvoy, N.; Ó Coileáin, C.; O'Neill, K.; Ansari, L.; Duesberg, G. S.; Nagle, R.; Cherkaoui, K.;

- Gity, F.; Hurley, P. K. Insights into Multilevel Resistive Switching in Monolayer MoS<sub>2</sub>. ACS Appl. Mater. Interfaces **2020**, 12, 6022–6029.

- (8) Zhu, K.; Pazos, S.; Aguirre, F.; Shen, Y.; Yuan, Y.; Zheng, W.; Alharbi, O.; Villena, M. A.; Fang, B.; Li, X.; Milozzi, A.; Farronato, M.; Muñoz-Rojo, M.; Wang, T.; Li, R.; Fariborzi, H.; Roldan, J. B.; Benstetter, G.; Zhang, X.; Alshareef, H. N.; Grasser, T.; Wu, H.; Ielmini, D.; Lanza, M. Hybrid 2D-CMOS microchips for memristive applications. *Nature* **2023**, *618*, 57–62.

- (9) Matsunaga, N.; Imai, S.; Shirokura, T.; Tsutsui, K.; Kakushima, K.; Wakabayashi, H. In *High quality PVD-MoS2 Film on Plasma-ALD-SiO2 Underlaying Material for CFET Integration*, 2024 8th IEEE Electron Devices Technology & Manufacturing Conference (EDTM); IEEE, 2024; pp 1–3.

- (10) Chen, J.; Sun, M.-Y.; Wang, Z.-H.; Zhang, Z.; Zhang, K.; Wang, S.; Zhang, Y.; Wu, X.; Ren, T.-L.; Liu, H.; Han, L. Performance Limits and Advancements in Single 2D Transition Metal Dichalcogenide Transistor. *Nano-Micro Lett.* **2024**, *16*, No. 264.

- (11) Schram, T.; Sutar, S.; Radu, I.; Asselberghs, I. Challenges of Wafer-Scale Integration of 2D Semiconductors for High-Performance Transistor Circuits. *Adv. Mater.* **2022**, *34*, No. 2109796.

- (12) Marquez, C.; Salazar, N.; Gity, F.; Galdon, J. C.; Navarro, C.; Sampedro, C.; Hurley, P. K.; Chang, E. Y.; Gamiz, F. Hysteresis in As-Synthesized MoS<sub>2</sub> Transistors: Origin and Sensing Perspectives. *Micromachines* **2021**, *12*, No. 646.

- (13) Illarionov, Y. Y.; Smithe, K. K. H.; Waltl, M.; Knobloch, T.; Pop, E.; Grasser, T. Improved Hysteresis and Reliability of MoS<sub>2</sub> Transistors With High-Quality CVD Growth and Al<sub>2</sub>O<sub>3</sub> Encapsulation. *IEEE Electron Device Lett.* **2017**, 38, 1763–1766.

- (14) Illarionov, Y. Y.; Banshchikov, A. G.; Polyushkin, D. K.; Wachter, S.; Knobloch, T.; Thesberg, M.; Mennel, L.; Paur, M.; Stöger-Pollach, M.; Steiger-Thirsfeld, A.; Vexler, M. I.; Waltl, M.; Sokolov, N. S.; Mueller, T.; Grasser, T. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. *Nat. Electron.* **2019**, *2*, 230–235.

- (15) Bhattacharjee, S.; Ganapathi, K. L.; Nath, D. N.; Bhat, N. Surface state engineering of metal/MoS<sub>2</sub> contacts using sulfur treatment for reduced contact resistance and variability. *IEEE Trans. Electron Devices* **2016**, *63*, 2556–2562.

- (16) Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High performance multilayer  $MoS_2$  transistors with scandium contacts. *Nano Lett.* **2013**, *13*, 100–105.

- (17) Penumatcha, A.; O'Brien, K. P.; Maxey, K.; Mortelmans, W.; Steinhardt, R.; Dutta, S.; Dorow, C. J.; Naylor A, C. H.; Kitamura, K.; Zhong, T.; Tronic, T.; Buragohain, P.; Rogan, C.; Lin, C.-C.; Kavrik, M.; Lux, J.; Oni, A.; Vyatskikh, A.; Lee, S.; Arefin, N.; Fischer, P.; Clenndenning, S.; Radosavljevic, M.; Metz, M.; Avci, U. In *High Mobility TMD NMOS and PMOS Transistors and GAA Architecture for Ultimate CMOS Scaling*, 2023 International Electron Devices Meeting (IEDM); IEEE, 2023; pp 1–4.

- (18) Mootheri, V.; Leonhardt, A.; Verreck, D.; Asselberghs, I.; Huyghebaert, C.; De Gendt, S.; Radu, I.; Lin, D.; Heyns, M. Understanding ambipolar transport in MoS<sub>2</sub> field effect transistors: the substrate is the key. *Nanotechnology* **2021**, 32, No. 135202.

- (19) Marquez, C.; Salazar, N.; Gity, F.; Navarro, C.; Mirabelli, G.; C Galdon, J.; Duffy, R.; Navarro, S.; K Hurley, P.; Gamiz, F. Investigating the transient response of Schottky barrier back-gated MoS<sub>2</sub> transistors. 2D Mater. **2020**, 7, No. 025040.

- (20) Di Bartolomeo, A.; Grillo, A.; Urban, F.; Iemmo, L.; Giubileo, F.; Luongo, G.; Amato, G.; Croin, L.; Sun, L.; Liang, S.; Ang, L. K. Asymmetric Schottky Contacts in Bilayer MoS <sub>2</sub> Field Effect Transistors. *Adv. Funct. Mater.* **2018**, 28, No. 1800657.

- (21) Park, Y.; Li, N.; Jung, D.; Singh, L. T.; Baik, J.; Lee, E.; Oh, D.; Kim, Y. D.; Lee, J. Y.; Woo, J.; Park, S.; Kim, H.; Lee, G.; Lee, G.; Hwang, C.-C. Unveiling the origin of n-type doping of natural MoS<sub>2</sub>: carbon. *npj* 2D Mater. Appl. **2023**, 7, No. 60.

- (22) Tang, L.; Zou, J. p-Type Two-Dimensional Semiconductors: From Materials Preparation to Electronic Applications. *Nano-Micro Lett.* **2023**, *15*, No. 230.

- (23) Vandalon, V.; Verheijen, M. A.; Kessels, W. M. M.; Bol, A. A. Atomic Layer Deposition of Al-Doped MoS<sub>2</sub>: Synthesizing a p-type 2D Semiconductor with Tunable Carrier Density. *ACS Appl. Nano Mater.* **2020**, 3, 10200–10208.

- (24) Chung, Y.-Y.; Lu, K.-C.; Cheng, C.-C.; Li, M.-Y.; Lin, C.-T.; Li, C.-F.; Chen, J.-H.; Lai, T.-Y.; Li, K.-S.; Shieh, J.-M.; Su, S.-K.; Chiang, H.-L.; Chen, T.-C.; Li, L.-J.; Wong, H.-S. P.; Jian, W.-B.; Chien, C.-H. Demonstration of 40-nm Channel Length Top-Gate p-MOSFET of WS $_2$  Channel Directly Grown on SiO  $_x$  /Si Substrates Using Area-Selective CVD Technology. *IEEE Trans. Electron Devices* **2019**, 66, 5381–5386.

- (25) Ovchinnikov, D.; Allain, A.; Huang, Y.-S.; Dumcenco, D.; Kis, A. Electrical transport properties of single-layer WS<sub>2</sub>. ACS Nano **2014**, 8, 8174–8181.

- (26) Bao, W.; Cai, X.; Kim, D.; Sridhara, K.; Fuhrer, M. S. High mobility ambipolar MoS<sub>2</sub> field-effect transistors: Substrate and dielectric effects. *Appl. Phys. Lett.* **2013**, *102*, No. 042104.

- (27) Zhang, Y.; Ye, J.; Matsuhashi, Y.; Iwasa, Y. Ambipolar MoS<sub>2</sub> Thin Flake Transistors. *Nano Lett.* **2012**, *12*, 1136–1140.

- (28) Han, X.; Lin, J.; Liu, J.; Wang, N.; Pan, D. Effects of Hexagonal Boron Nitride Encapsulation on the Electronic Structure of Few-Layer MoS<sub>2</sub>. J. Phys. Chem. C **2019**, 123, 14797–14802.

- (29) Liu, H.; Li, D.; Ma, C.; Zhang, X.; Sun, X.; Zhu, C.; Zheng, B.; Zou, Z.; Luo, Z.; Zhu, X.; et al. Van der Waals epitaxial growth of vertically stacked Sb<sub>2</sub>Te<sub>3</sub>/MoS<sub>2</sub> p-n heterojunctions for high performance optoelectronics. *Nano Energy* **2019**, *59*, 66–74.

- (30) O'Brien, K. P.; Dorow, C. J.; Penumatcha, A.; Maxey, K.; Lee, S.; Naylor, C. H.; Hsiao, A.; Holybee, B.; Rogan, C.; Adams, D.; Tronic, T.; Ma, S.; Oni, A.; Gupta, A. S.; Bristol, R.; Clendenning, S.; Metz, M.; Avci, U. In *Advancing 2D Monolayer CMOS Through Contact, Channel and Interface Engineering*, IEEE International Electron Devices Meeting (IEDM); IEEE, 2021.

- (31) Schram, T.; Smets, Q.; Groven, B.; Heyne, M. H.; Kunnen, E.; Thiam, A.; Devriendt, K.; Delabie, A.; Lin, D.; Lux, M.; Chiappe, D.; Asselberghs, I.; Brus, S.; Huyghebaert, C.; Sayan, S.; Juncker, A.; Caymax, M.; Radu, I. P. In WS2 Transistors on 300 mm Wafers with BEOL Compatibility, 2017 47th European Solid-State Device Research Conference (ESSDERC); IEEE, 2017; pp 212–215.

- (32) Knoops, H. C. M.; Faraz, T.; Arts, K.; Kessels, W. M. M. E. Status and prospects of plasma-assisted atomic layer deposition. *J. Vac. Sci. Technol. A* **2019**, 37, No. 030902.

- (33) Boris, D. R.; Wheeler, V. D.; Nepal, N.; Qadri, S. B.; Walton, S. G.; Eddy, C. C. R. The role of plasma in plasma-enhanced atomic layer deposition of crystalline films. *J. Vac. Sci. Technol., A* **2020**, 38, No. 040801.

- (34) Sharma, A.; Verheijen, M. A.; Wu, L.; Karwal, S.; Vandalon, V.; Knoops, H. C. M.; Sundaram, R. S.; Hofmann, J. P.; Kessels, W. M. M. E.; Bol, A. A. Low-temperature plasma-enhanced atomic layer deposition of 2-D MoS<sub>2</sub>: large area, thickness control and tuneable morphology. *Nanoscale* **2018**, *10*, 8615–8627.

- (35) Mattinen, M.; Gity, F.; Coleman, E.; Vonk, J. F.; Verheijen, M. A.; Duffy, R.; Kessels, W. M.; Bol, A. A. Atomic Layer Deposition of Large-Area Polycrystalline Transition Metal Dichalcogenides from 100°C through Control of Plasma Chemistry. *Chem. Mater.* **2022**, 34, 7280–7292.

- (36) Pyeon, J. J.; Kim, S. H.; Jeong, D. S.; Baek, S.-H.; Kang, C.-Y.; Kim, J.-S.; Kim, S. K. Wafer-scale growth of  $MoS_2$  thin films by atomic layer deposition. *Nanoscale* **2016**, *8*, 10792–10798.

- (37) Mahlouji, R.; Zhang, Y.; Verheijen, M. A.; Hofmann, J. P.; Kessels, W. M. M.; Sagade, A. A.; Bol, A. A. On the Contact Optimization of ALD-Based MoS <sub>2</sub> FETs: Correlation of Processing Conditions and Interface Chemistry with Device Electrical Performance. ACS Appl. Electron. Mater. 2021, 3, 3185–3199.

- (38) Asselberghs, I.; Smets, Q.; Schram, T.; Groven, B.; Verreck, D.; Afzalian, A.; Arutchelvan, G.; Gaur, A.; Cott, D.; Maurice, T.; Brems, S.; Kennes, K.; Phommahaxay, A.; Dupuy, E.; Radisic, D.; De Marneffe, J.-F.; Thiam, A.; Li, W.; Devriendt, K.; Huyghebaert, C.; Lin, D.; Caymax, M.; Morin, P.; Radu, I. In Wafer-scale integration of double gated WS2-transistors in 300mm Si CMOS fab, 2020 IEEE

- International Electron Devices Meeting (IEDM). San Francisco, CA, USA; IEEE, 2020; pp 40.2.1–40.2.4.

- (39) Mahlouji, R.; Zhang, Y.; Verheijen, M. A.; Karwal, S.; Hofmann, J. P.; Kessels, W. M. M.; Bol, A. A. Influence of High-κ Dielectrics Integration on ALD-Based MoS<sub>2</sub> Field-Effect Transistor Performance. *ACS Appl. Nano Mater.* **2024**, *7*, 18786–18800.

- (40) Jagosz, J.; Willeke, L.; Gerke, N.; Becher, M. J. M. J.; Plate, P.; Kostka, A.; Rogalla, D.; Ostendorf, A.; Bock, C. Wafer-Scale Demonstration of Polycrystalline MoS<sub>2</sub> Growth on 200 mm Glass and SiO<sub>2</sub>/Si Substrates by Plasma-Enhanced Atomic Layer Deposition. *Adv. Mater. Technol.* **2024**, *9*, No. 2400492.

- (41) Neubieser, R.-M.; Wree, J.-L.; Jagosz, J.; Becher, M.; Ostendorf, A.; Devi, A.; Bock, C.; Michel, M.; Grabmaier, A. Low-temperature ALD process development of 200 mm wafer-scale MoS<sub>2</sub> for gas sensing application. *Micro Nano Eng.* **2022**, *15*, No. 100126.

- (42) Aspiotis, N.; Morgan, K.; März, B.; Müller-Caspary, K.; Ebert, M.; Weatherby, E.; Light, M. E.; Huang, C.-C.; Hewak, D. W.; Majumdar, S.; Zeimpekis, I. Large-area synthesis of high electrical performance MoS<sub>2</sub> by a commercially scalable atomic layer deposition process. *npj* 2D Mater. Appl. **2023**, 7, No. 18.

- (43) Mattinen, M.; Leskelä, M.; Ritala, M. Atomic Layer Deposition of 2D Metal Dichalcogenides for Electronics, Catalysis, Energy Storage, and Beyond. *Adv. Mater. Interfaces* **2021**, *8*, No. 2001677.

- (44) Fei, W.; Trommer, J.; Lemme, M. C.; Mikolajick, T.; Heinzig, A. Emerging reconfigurable electronic devices based on twodimensional materials: A review. *InfoMat* **2022**, *4*, No. e12355.

- (45) Wu, P.; Reis, D.; Hu, X. S.; Appenzeller, J. Two-dimensional transistors with reconfigurable polarities for secure circuits. *Nat. Electron.* **2021**, *4*, 45–53.

- (46) Lee, Y.-H.; Zhang, X.-Q.; Zhang, W.; Chang, M.-T.; Lin, C.-T.; Chang, K.-D.; Yu, Y.-C.; Wang, J. T.-W.; Chang, C.-S.; Li, L.-J.; Lin, T.-W. Synthesis of Large-Area MoS<sub>2</sub> Atomic Layers with Chemical Vapor Deposition. *Adv. Mater.* **2012**, *24*, 2320–2325.

- (47) Li, H.; Zhang, Q.; Yap, C. C. R.; Tay, B. K.; Edwin, T. H. T.; Olivier, A.; Baillargeat, D. From Bulk to Monolayer MoS<sub>2</sub>: Evolution of Raman Scattering. *Adv. Funct. Mater.* **2012**, 22, 1385–1390.

- (48) Mignuzzi, S.; Pollard, A. J.; Bonini, N.; Brennan, B.; Gilmore, I. S.; Pimenta, M. A.; Richards, D.; Roy, D. Effect of disorder on Raman scattering of single-layer MoS<sub>2</sub>. *Phys. Rev. B* **2015**, *91*, No. 195411.

- (49) Golasa, K.; Grzeszczyk, M.; Bożek, R.; Leszczyński, P.; Wysmołek, A.; Potemski, M.; Babiński, A. Resonant Raman scattering in MoS<sub>2</sub>: From bulk to monolayer. *Solid State Commun.* **2014**, *197*, 53–56.

- (50) Schrader, G.; Cheng, C. In situ laser raman spectroscopy of the sulfiding of  $Mo/\gamma$ -Al<sub>2</sub>O<sub>3</sub> catalysts. *J. Catal.* **1983**, *80*, 369–385.

- (51) Park, W.; Baik, J.; Kim, T. Y.; Cho, K.; Hong, W. K.; Shin, H. J.; Lee, T. Photoelectron spectroscopic imaging and device applications of large-Area patternable single-layer MoS<sub>2</sub> synthesized by chemical vapor deposition. *ACS Nano* **2014**, *8*, 4961–4968.

- (\$2) Hussain, S.; Singh, J.; Vikraman, D.; Singh, A. K.; Iqbal, M. Z.; Khan, M. F.; Kumar, P.; Choi, D. C.; Song, W.; An, K. S.; Eom, J.; Lee, W. G.; Jung, J. Large-area, continuous and high electrical performances of bilayer to few layers MoS<sub>2</sub> fabricated by RF sputtering via post-deposition annealing method. *Sci. Rep.* **2016**, *6*, No. 30791.

- (53) Xia, P.; Feng, X.; Ng, R. J.; Wang, S.; Chi, D.; Li, C.; He, Z.; Liu, X.; Ang, K.-W. Impact and Origin of Interface States in MOS Capacitor with Monolayer MoS<sub>2</sub> and HfO2 High-κ Dielectric. *Sci. Rep.* **2017**, *7*, No. 40669.

- (54) Muratore, C.; Hu, J. J.; Wang, B.; Haque, M. A.; Bultman, J. E.; Jespersen, M. L.; Shamberger, P. J.; McConney, M. E.; Naguy, R. D.; Voevodin, A. A. Continuous ultra-thin MoS<sub>2</sub> films grown by low-temperature physical vapor deposition. *Appl. Phys. Lett.* **2014**, *104*, No. 261604.

- (55) Illarionov, Y. Y.; Rzepa, G.; Waltl, M.; Knobloch, T.; Grill, A.; Furchi, M. M.; Mueller, T.; Grasser, T. The role of charge trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN field-effect transistors. 2D Mater. **2016**, 3, No. 035004.

- (56) Lan, C.; Li, C.; Ho, J. C.; Liu, Y. 2D WS2: From Vapor Phase Synthesis to Device Applications. *Adv. Electron. Mater.* **2021**, 7, No. 2000688.

- (57) McDonnell, S.; Addou, R.; Buie, C.; Wallace, R. M.; Hinkle, C. L. Defect-Dominated Doping and Contact Resistance in MoS<sub>2</sub>. *ACS Nano* **2014**, *8*, 2880–2888.

- (58) Schroder, D. K. Semiconductor Material and Device Characterization, 3rd ed.; John Wiley & Sons, 2005; pp 2–21.

- (59) Sze, S.; Ng, K. Physics of Semiconductor Devices; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2006; pp 134–196.

- (60) Rhoderick, E. H.; Williams, R. H. Metal-Semiconductor Contacts; Clarendon Press: Oxford, 1988; Vol. 129.

- (61) Zhao, Y.; Ouyang, G. Thickness-dependent photoelectric properties of MoS2/Si heterostructure solar cells. *Sci. Rep.* **2019**, *9*, No. 17381.

- (62) Mott, N. F.; Davis, E. A. Electronic Processes in Non-Crystalline Materials, 2nd ed.; International series of monographs on physics; Clarendon Press: Oxford, 2012.

- (63) Zhuo, F.; Wu, J.; Li, B.; Li, M.; Tan, C. L.; Luo, Z.; Sun, H.; Xu, Y.; Yu, Z. Modifying the Power and Performance of 2-Dimensional MoS<sub>2</sub> Field Effect Transistors. *Research* **2023**, *6*, No. 0057.

- (64) Urban, F.; Martucciello, N.; Peters, L.; McEvoy, N.; Di Bartolomeo, A. Environmental Effects on the Electrical Characteristics of Back-Gated WSe2 Field-Effect Transistors. *Nanomaterials* **2018**, 8, No. 901.

- (65) Rashid, S. J.; Tajani, A.; Twitchen, D. J.; Coulbeck, L.; Udrea, F.; Butler, T.; Rupesinghe, N. L.; Brezeanu, M.; Isberg, J.; Garraway, A.; Dixon, M.; Balmer, R. S.; Chamund, D.; Taylor, P.; Amaratunga, G. A. J. Numerical Parameterization of Chemical-Vapor-Deposited (CVD) Single-Crystal Diamond for Device Simulation and Analysis. *IEEE Trans. Electron Devices* **2008**, 55, 2744–2756.

- (66) Di Bartolomeo, A.; Genovese, L.; Giubileo, F.; Iemmo, L.; Luongo, G.; Foller, T.; Schleberger, M. Hysteresis in the transfer characteristics of MoS<sub>2</sub> transistors. 2D Mater. **2018**, 5, No. 015014.

- (67) McWhorter, A. L. 1/f Noise and Germanium Surface Properties Semicond. Surf. Phys. 1957; Vol. 207.

- (68) Hooge, F. 1/f noise. Phys. B+C 1976, 83, 14-23.

- (69) Jomaah, J.; Balestra, F.; Ghibaudo, G. Low frequency noise in advanced Si bulk and SOI MOSFETs. *J. Telecommun. Inf. Technol.* **2005**, 24–33.

- (70) Kwon, J.; Delker, C. J.; Janes, D. B.; Harris, C. T.; Das, S. R. Molybdenum Contacts to MoS<sub>2</sub> Field-Effect Transistors: Schottky Barrier Extraction, Electrical Transport, and Low-Frequency Noise. *Phys. Status Solidi A* **2020**, *217*, No. 1900880.