MDPI

Article

# Hysteresis in As-Synthesized MoS<sub>2</sub> Transistors: Origin and Sensing Perspectives

Carlos Marquez <sup>1,\*,†</sup>, Norberto Salazar <sup>1,\*,†</sup>, Farzan Gity <sup>2</sup>, Jose C. Galdon <sup>1</sup>, Carlos Navarro <sup>1</sup>, Carlos Sampedro <sup>1</sup>, Paul K. Hurley <sup>2</sup>, Edward Yi Chang <sup>3</sup> and Francisco Gamiz <sup>1</sup>

- Nanoelectronics Research Group (CITIC-UGR), Department of Electronics, University of Granada, 18071 Granada, Spain; jcgaldon@ugr.es (J.C.G.); carlosnm@ugr.es (C.N.); csampe@ugr.es (C.S.); fgamiz@ugr.es (F.G.)

- Nanoelectronic Materials and Devices Group, Tyndall National Institute, University College Cork, T12 R5CP Cork, Ireland; farzan.gity@tyndall.ie (F.G.); paul.hurley@tyndall.ie (P.K.H.)

- International College of Semiconductor Technology, National Yang Ming Chiao Tung University, Hsinchu 30010, Taiwan; edc@mail.nctu.edu.tw

- \* Correspondence: carlosmg@ugr.es (C.M.); nsalazar@ugr.es (N.S.)

- † These authors contributed equally to this work.

Abstract: Two-dimensional materials, including molybdenum disulfide (MoS<sub>2</sub>), present promising sensing and detecting capabilities thanks to their extreme sensitivity to changes in the environment. Their reduced thickness also facilitates the electrostatic control of the channel and opens the door to flexible electronic applications. However, these materials still exhibit integration difficulties with complementary-MOS standardized processes and methods. The device reliability is compromised by gate insulator selection and the quality of the metal/semiconductor and semiconductor/insulator interfaces. Despite some improvements regarding mobility, hysteresis and Schottky barriers having been reported thanks to metal engineering, vertically stacked heterostructures with compatible thin-layers (such as hexagonal boron nitride or device encapsulation) variability is still an important constraint to sensor performance. In this work, we fabricated and extensively characterized the reliability of as-synthesized back-gated MoS<sub>2</sub> transistors. Under atmospheric and room-temperature conditions, these devices present a wide electrical hysteresis (up to 5 volts) in their transfer characteristics. However, their performance is highly influenced by the temperature, light and pressure conditions. The singular signature in the time response of the devices points to adsorbates and contaminants inducing mobile charges and trapping /detrapping carrier phenomena as the mechanisms responsible for time-dependent current degradation. Far from being only a reliability issue, we demonstrated a method to exploit this device response to perform light, temperature and/or pressure sensors in as-synthesized devices. Two orders of magnitude drain current level differences were demonstrated by comparing device operation under light and dark conditions while a factor up to 10<sup>5</sup> is observed at vacuum versus atmospheric pressure environments.

Keywords: two-dimensional materials; light sensor; molybdenum disulfide; MoS2; trapping; reliability

Citation: Marquez, C.; Salazar, N.; Gity, F.; Galdon, J.C.; Navarro, C.; Sampedro, C.; Hurley, P.K.; Chang, E.Y.; Gamiz, F. Hysteresis in As-Synthesized MoS<sub>2</sub> Transistors: Origin and Sensing Perspectives. *Micromachines* **2021**, *12*, 646. https://doi.org/10.3390/mi12060646

Academic Editor: Aiqun Liu

Received: 30 April 2021 Accepted: 30 May 2021 Published: 31 May 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

In the last decades, the limitations in chip integration to achieve Moore's law density requirements have been overcome through the progressive scaling of the transistor dimensions (particularly channel length) [1,2], the incorporation of high- $\kappa$  insulators [3] and the design of new device architectures (FinFet, SOI, trigate) [4] to achieve better control of the device performance. The advances in the lithography (deep ultraviolet (DUV) and multi-patterning techniques) have been employed to shrink the dimensions of transistors down-to sub-10 nm channel lengths [2]. However, to support more scaled process technologies, the half-pitch resolution should be improved. In this context, extreme ultraviolet (EUV) lithography has been proposed assuming that costly new manufacturing equipment

Micromachines **2021**, 12, 646 2 of 13

will be needed [5]. At the same time, other alternatives to increase the performance of the integrated circuits have been considered.

Silicon channel material substitution has been one of the most studied options to address Moore's law [6]. On the one hand, III-V and Germanium (Ge) compounds have been widely analyzed with outstanding results in high power, memory and photonics applications [7,8]. However, limitations in any of the carrier mobilities (electrons or holes), wider bandgaps and difficulties in their integration into silicon processes have limited the applications in complimentary MOS (CMOS) technology [6]. On the other hand, twodimensional materials, led by the discovery of graphene [9,10], have attracted tremendous attention due to their promising electrical properties [5,11]. Thanks to their low dimensionality, these thin materials present an optimal electrostatic control of the channel [12], flexibility and extremely sensitive capabilities to the changes in their surroundings. Despite the fact that graphene seems to be less attractive to the logical electronic applications due to its zero bandgap, other two-dimensional materials, such as transition metal dichalcogenides (TMDs), have demonstrated an indirect to direct bandgap modulation depending on the layer thickness inside an interesting range for electronic applications [13]. Within the family of TMDs, MoS<sub>2</sub> and WS<sub>2</sub> with thickness-dependent bandgaps in the range of 1.2–1.8 eV and usually n-type behavior have received special attention [14].

Intermediate solutions between the complete replacement of silicon by alternative materials and silicon hegemony have been proposed. Three-dimensional (3D) integration consists of employing multiple vertically stacked active layers (containing active devices such as transistors, diodes and logic memory devices) to achieve higher integration density, lower power consumption and better signal integrity [15,16]. In this context, the incorporation of atomically thin 2D-material-based devices and interconnects in monolithic-3D integration have been already proposed to overcome several major problems of conventional technologies such as inter-tier signal delay, chip overheating and inter-tier electrical interference problems [17,18]. In fact, some advances have already been demonstrated using 2D materials as back-end of the line (BEOL) to improve the interconnect scaling [19] or the chip heat dissipation [18]. Additionally, the 3D integration of 2D devices to perform logic memory cells [20], opto-electronic detectors or sensors [21,22], are promising approaches to realize system-on-chip (SoC) designs solving the density constraints. In this context, the integration of 2D materials could seem particularly interesting in sensing applications due to their atomic thickness and extreme sensitivity to changes in the environment. Nonetheless, there are still technological limitations regarding the two-dimensional material integration in semiconductor fabrication flow [23]: (i) the majority of studies that explore TMDs obtain films using methods that are not scalable, such as mechanical exfoliation or methods that are not CMOS compatible such as synthesis at high temperatures (T > 450  $^{\circ}$ C); (ii) the devices rarely accomplish the promised theoretical properties of these 2D materials. Defects and impurities inducing Fermi level pinning at the metal interfaces, Schottky-barrier formation, current hysteresis or Coulomb scattering are some of the reliability issues of the fabricated 2D devices [24–28]. Despite some performance and reliability improvements having been achieved by employing interfacial compatible thin insulator such as hexagonal boron nitride [29], vertically stacked heterostructures [30] or high-quality encapsulation processing [26], these processes may limit the environmental sensing capabilities of these two-dimensional devices. Regrettably, without these encapsulation or passivation processes, the selectivity and performance of 2D materials rapidly decreases as defects, imperfections and dislocations in the material and at the interfaces may mask the response to the detection target [31]. In spite of this difficulty, at the same time, defects and imperfections can also lead to electrical responses that could be used to enhance the sensing capabilities of these devices. Residual ions, adsorbates and trapped carriers are translated to mobile and fixed charges. These charge-related phenomena are also affected by device surroundings such as temperature, humidity or light conditions, which means that, if controlled and characterized, they could be used as sensing parameters.

Micromachines **2021**, 12, 646 3 of 13

In this work, our goal is to investigate the disturbing mechanisms that affect the operation of as-synthesized MoS<sub>2</sub> back-gated devices under different work conditions and evaluate how these mechanisms can be employed to enhance the sensing and detecting capabilities of the fabricated devices. The accomplishment of sensors employing as-synthesized two-dimensional materials without the need of passivation or encapsulation processes could lead to a huge advance in the integration of these thin materials and the relaxation of the fabrication complexity.

### 2. Materials and Methods

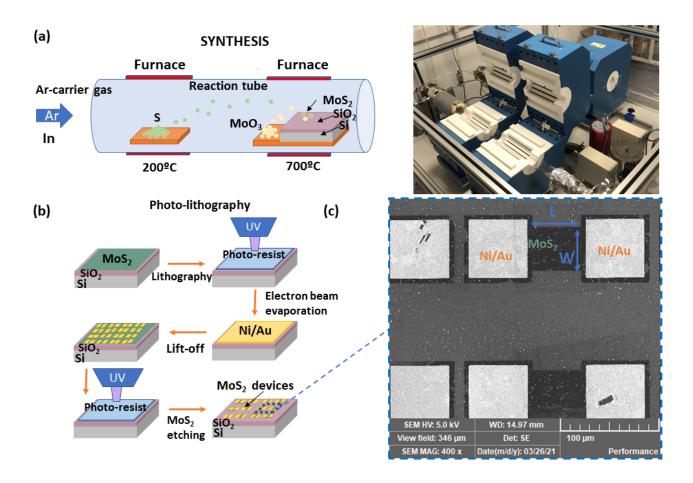

Devices were fabricated through the direct synthesis of large-area MoS<sub>2</sub> films on an n-type silicon substrate covered by a 100 nm thick SiO<sub>2</sub> layer. This substrate selection allows for the fabrication of back-gated transistors without any film transfer. Synthesis was accomplished via chemical vapor deposition (CVD) through sulfurization of molybdenum trioxide (MoO<sub>3</sub>) on the target substrates at a maximum temperature of 700 °C. Figure 1a (left) depicts a scheme of the process carried out in a two-temperature-zone tube furnace; a picture of the experimental setup is shown in Figure 1a (right). Further information regarding the synthesis of the  $MoS_2$  layer can be found in our previous work [32]. The device processing is summarized in Figure 1b: UV photo-lithography and lift-off were used to define the source and drain patterns on the MoS<sub>2</sub>. PMGI resist was spun at 4000 rpm for 50 s, and baked at 180 °C for 5 min, followed by spinning the S1813 resist at 4000 rpm for 50 s and baking at 115 °C for 2 min. Mask aligner was used in hard contact mode to expose the resist for 7 s. Then, the exposed resist was developed in MF-319 developer for 1 min 45 s. Electron beam evaporation was employed to deposit the Ni/Au electrodes. The thicknesses of the Ni and Au were 20 nm and 200 nm, respectively. The lift-off of the bi-layer resist stack was performed. Finally, the UV photo-lithography was repeated to perform a dry etching of the MoS<sub>2</sub> material outside the channel between source and drain contacts, employing fluorine-based chemistry (SF<sub>6</sub>/Ar: 5/45 sccm) at a power of 100 W and pressure of 6 mT. Scanning electron microscope characterization (SEM) (TESCAN VEGA3) corroborates the well-defined processing in Figure 1c.

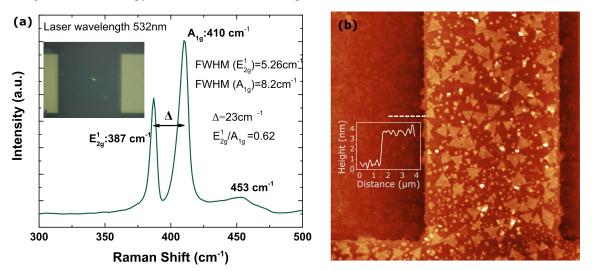

The chemical corroboration of the films was investigated by Raman spectroscopy (Jasco NRS-5100). Figure 2a shows the structural characterization of an  $MoS_2$  device (the inset indicates the channel zone where Raman characterization was performed) exhibiting the two Raman characteristic bands at 387 cm<sup>-1</sup> ( $E_{2g}^1$ ) and 410 cm<sup>-1</sup> ( $A_g^1$ ) with a separation between peaks ( $\Delta$ ) around 23 cm<sup>-1</sup>. These results are consistent with the presence of thin  $MoS_2$  layers [33]. Other parameters such as the full width at half maximum (FWHM) and the ratio of the peaks suggest multi-layer  $MoS_2$  devices [34]. Device thickness is measured using an atomic force microscope (NTMDT NTEGRA) in semicontact mode and with metallic tips. Figure 2b depicts the topography of the channel. Cross section in the inset determines around 4 nm thick  $MoS_2$  layer.

The electrical characteristics were measured in a Janis ST-500 cryogenic probe station with temperature, pressure and light intensity control capabilities. The direct-current (dc) characteristic was recorded using a Keithley SCS 4200 and an Agilent B1500 systems. The low-frequency noise characterization was carried out using a low-noise-current amplifier connected to a software-based spectrum analyzer [35].

Micromachines **2021**, 12, 646 4 of 13

**Figure 1.** (a) Scheme (**left**) and picture (**right**) of the chemical vapor deposition synthesis carried out in a two-temperature-zone tube furnace. Sulfur (S) and molybdenum trioxide (MoO<sub>3</sub>) are placed separately. During the reaction, an MoS<sub>2</sub> layer is deposited on the surface of the SiO<sub>2</sub>/Si substrate. (b) Diagram showing the sequence of the photo-lithography process. (c) Scanning electron microscopy (SEM) of the MoS<sub>2</sub> devices performed.

Figure 2. (a) Raman characterization of one of the  $MoS_2$  devices fabricated. Green dot in the inset indicates the area of characterization, corresponding with the channel of the device. (b) Atomic force microscopy (AFM) characterization of the channel of one  $MoS_2$  device. Inset presents the cross-section revealing an  $MoS_2$  layer thickness around 4 nm.

Micromachines **2021**, 12, 646 5 of 13

#### 3. Results

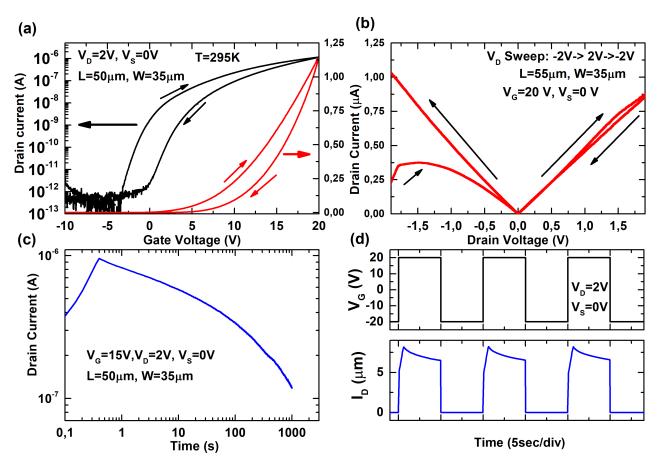

Figure 3a shows the transfer characteristic of a 50 µm length and 35 µm width MoS<sub>2</sub> back-gated device. Left and right axes show drain current in logarithmic and linear scale, respectively. Note that a wide hysteresis is observed when a double sweep gate bias is applied. Threshold voltage is shifted to positive levels while the device is forward-biased, presenting higher channel resistance during the backward sense. This phenomenon is expected when dealing with defective or non-passivated devices [26,36]. When a forward gate bias is applied, traps whose energy are below the Fermi level are filled by electrons with different characteristic times. The trapped electrons contribute to the increase of negative charge and therefore, increase the threshold voltage. However, Figure 3b shows a less usual aspect in the output characteristic. Considerable differences are observed between the forward and the backward sweep. Particularly interesting is the initial current increase during the first seconds of the measurement. In this  $I_D$ - $V_D$  curve, one can observe a non-linear and non-symmetrical behavior between positive and negative drain biases; this effect is attributed to the Schottky barriers formation at the metal-semiconductor interface. In this regard, our previous works have determined the formation of back-to-back Schottky diodes due to Fermi level pinning at the metal-semiconductor interfaces [32,37]. This Fermi level pinning induces Schottky barriers, which affect the performance of the device, in this case, blocking the hole carriers in the transfer characteristic. These results have also been presented in the literature [38,39]. However, this Schottky barrier formation does not entirely explain the curve shape.

**Figure 3.** (a) Transfer characteristic ( $I_D$ - $V_G$ ) of an MoS<sub>2</sub> device in logarithmic (left) and linear (right) scale. (b) Output characteristic ( $I_D$ - $V_D$ ) in a double sweep characterization. (c) Transient response ( $I_D$ -t) while a positive voltage is applied at the back gate. (d) Transient response of the device to successive positive (stress) and reverse (recover) pulses. L = 50 μm, W = 35 μm, T = 295K at atmospheric conditions.

*Micromachines* **2021**, 12, 646 6 of 13

To clarify this aspect, Figure 3c shows the transient response of the device while a positive gate pulse is applied. As observed, there is an initial time to reach the maximum drain current, followed by a decay period with a constant current decrease. To the best of our knowledge, this initial delay in the device operation is not reported in the literature for these two-dimensional devices, while the current decay is as expected for gated devices. Note that this time-dependent response implies that device hysteresis will depend on the measuring time. Fast measurements (less than 1 s) suffer from the current increase, whereas slow measurements (more than 1 s) will suffer an initial increase and then a current decrease. Therefore, the current level and the device hysteresis in each case will be different. Another relevant aspect is the permanent or temporal characteristic of this device degradation observed while operating. Figure 3d shows the transient response of the device when successive positive (stress) and negative (recover) pulses are applied. As observed, there is a full recovery of the device characteristic after the stress period ( $V_G$  = 20 V) if a recover pulse ( $V_G = -20 \text{ V}$ ) is then applied. This fact points to mobile charges and trapping/detrapping phenomena as the origin of the device instability. These defects can be associated with both extrinsic (diffused water molecules and the chemisorption of oxygen) and intrinsic defect at the interface due to oxygen and sulfur vacancies [40-42], or even defects due to a non-passivated surface bond of the MoS<sub>2</sub> [43]. Otherwise, in case of traps generation during the stress process (as observed in some devices due to bias temperature instability), the device would present a permanent degradation and the current level will not be fully recovered after the reverse bias pulse. On the other hand, the initial time to reach the maximum inversion charge is not extensively observed. In our previous work, we carried out an initial study in this regard, attributing this phenomenon to substrate limitations to reach the inversion layer at the back interface ( $SiO_2/Si$ ) due to the low doping level [32]. This limitation could be mitigated by peripheral inversion, a coupling effect, which usually happens in semiconductor devices when leaving regions exposed to ambient conditions or when there are residual charge on oxide surfaces [44]. If the density of the residual charge is higher than the semiconductor charge associated with the maximum depletion width, this charge may result in the depletion of the semiconductor surface and the generation and recombination of minority carriers. Despite the fact that this phenomenon explains the initial delay to reach the inversion charge in the devices, extensive characterization under different environmental conditions will reveal how to mitigate or enhance this for sensing applications.

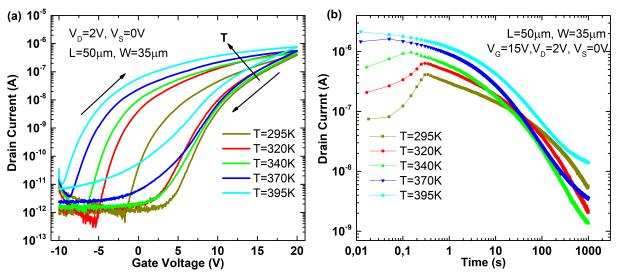

Figure 4 shows the transfer characteristic (Figure 4a) and the transient response (Figure 4b) of an MoS<sub>2</sub> device when increasing the temperature. Transfer characteristic reveals both a reduction of the threshold voltage and an increase of the hysteresis in the double sweep measurement. The threshold voltage shift can be explained by the higher thermal generation and the subsequent carrier density increase. Hysteresis signature can be derived from Figure 4b. On the one hand, the initial phenomenon implies an increase of the drain current to reach the maximum inversion charge, which then decreases at higher temperatures. This implies that the device can respond faster and points to carrier concentration limitations (lower concentration at lower temperature) as the origin of this initial phenomenon. On the other hand, the current decay, governed by carrier trapping phenomena and mobile ions, also increases with the temperature. This current degradation increasing with temperature is usually attributed to an enhancement of carrier trapping/detrapping events known as bias temperature instabilities (BTI) and is mainly attributed to process-related pre-existing defects or interface trap generation, whose time dynamics are described by the reaction–diffusion (RD) model [45,46].

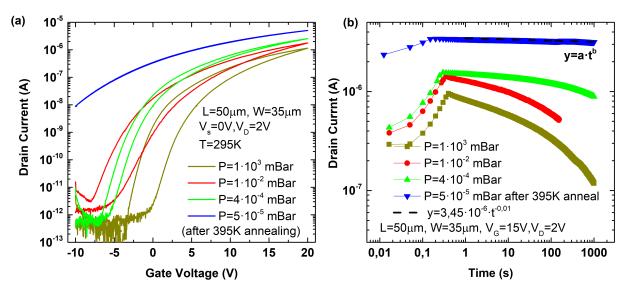

Figure 5 shows the transfer (Figure 5a) and transient (Figure 5b) characteristics of the device when different pressure conditions are set, from atmospheric pressure up to high vacuum. Lower pressure (higher vacuum) improves the behavior of the device, reducing the current decay, which also implies a narrower hysteresis. The increase of the current level at low pressures suggests a decrease of the threshold voltage and therefore a defect charge density diminution (less ions or charged defects). Especially relevant is the case

Micromachines **2021**, 12, 646 7 of 13

of high vacuum after an annealing period at high temperature (395 K)—marked by the blue symbols. The hysteresis (Figure 5a) and current degradation (Figure 5b) for this case are almost negligible. This result suggests that mobile ions and charges are mainly due to adsorbates and ambient contaminants, which can be removed at high temperature, when vacuum conditions limit their reappearance. After the removal of adsorbates, the current decay follows a power–law time dependence attributed to trapping/detrapping mechanisms in pre-existing traps (intrinsic traps) [45]. Note also that this result is in agreement with the higher degradation observed at high temperature and atmospheric conditions (Figure 4) due to the presence of contaminants together with the trapping/detrapping mechanisms enhanced by the bias temperature instability. However, the impact of the pressure on the initial time to reach the maximum current level is minimal when compared to the temperature correlation observed in Figure 4. This means that the initial time to reach the maximum inversion charge is independent of these contaminants and adsorbates.

**Figure 4.** (a) Transfer characteristic ( $I_D$ - $V_G$ ) of an MoS<sub>2</sub> device for different temperatures. (b) Transient response ( $I_D$ -t) for different temperatures when a positive voltage is applied at the back gate.

**Figure 5.** (a) Transfer characteristic ( $I_D$ - $V_G$ ) of an MoS<sub>2</sub> device for different pressure conditions. (b) Transient response ( $I_D$ -t) for different pressure conditions when a positive voltage is applied at the back gate.

Micromachines **2021**, 12, 646 8 of 13

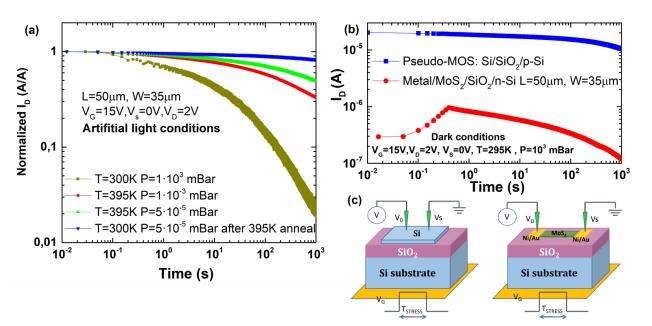

Contrarily to the previously observed, if an artificial light source (wide-spectrum controlled intensity lamp) is employed to illuminate the device during the characterization, it does not show the initial ramp to reach the maximum current, as Figure 6a shows. A change in light source could mean an increase of the carrier density; therefore, the current delay experience under dark conditions can be related to an initial carrier limitation. Different effects can be considered to explain this limitation. Considering that the silicon substrate is not highly doped ( $N_D \sim 10^{16} {

m cm}^{-3}$ ), inversion at the back interface depends on the thermal generation/recombination of minority carriers. This slow process at the back interface may suppose an initial lack of majority carriers at the front interface. Illumination (or high temperature) can accelerate the carrier generation (thermal generation) decreasing this delay time. Moreover, the minority carrier density at the back interface can also be affected by channel or surface pre-existent charges through peripheral inversion effect. Fixed charges in the channel or at interface can induce an opposite-sign charge at the back interface, facilitating or inhibiting the inversion layer formation (depending on the sign). Additionally, other effects can also contribute to the initial current delay. Due to the high Schottky barriers induced by the Fermi level pinning, holes carriers, i.e., minorities considering n-type semiconductor, cannot easily escape from the channel through the contacts. This charge can have a twofold effect. Positive charge at the front interface may induce a negative charge at the back interface by peripheral inversion, limiting the layer inversion and it may enhance the carrier recombination reducing the majority carrier density.

**Figure 6.** (a) Transient response ( $I_D$ -t) for different pressure conditions under artificial light conditions when a positive voltage is applied at the back gate. (b) Transient response ( $I_D$ -t) comparison between a silicon pseudo-MOS device and the MoS<sub>2</sub> back-gated transistor at atmospheric and dark conditions. (c) Scheme of the pseudo-MOS (**left**) and the MoS<sub>2</sub> device (**right**) measurement configuration.

To shed light on which of these mechanisms can have more influence on the origin of this initial current delay in the transient response, devices with a similar substrate structure, but different active layer technology, were tested. Figure 6b compares the transient response of the devices for two different technologies at room temperature and atmospheric conditions: (i) the one we characterized previously, a 55  $\mu$ m length and 35  $\mu$ m width MoS<sub>2</sub> device with two Ni/Au contacts as source and drain and a SiO<sub>2</sub>/low n-type doped silicon layer acting as back gate, with (ii) a pseudo-MOS transistor and a p-type active silicon layer on a SiO<sub>2</sub>/low p-type doped silicon layer acting as back gate. A scheme of the two different technologies is shown in Figure 6c. The main similarity between these

Micromachines **2021**, 12, 646 9 of 13

devices is the use of low doped layers as channel and back gate terminals, and the absence of a passivation layer in the device surface (bare devices). The main differences are: (i) the active layer material (MoS<sub>2</sub> vs. low doped Si) and (ii) the transport mechanism at the metal/semiconductor interface, which displays ohmic behavior due to tunneling from the needles to the channel in the case of the pseudo-MOS transistor[47] versus thermo-ionic emission due to Schottky barrier formation in MoS<sub>2</sub> devices [36]. As observed in Figure 6b, the pseudo-MOS device is not suffering from the initial delay to form the inversion charge. Despite the fact that this result cannot totally discard an isolated effect of the substrate as the origin of the initial instability (because the devices are quite technologically different), it points to an effect induced by the singular characteristics of the MoS<sub>2</sub> active layer more than an effect due to the low doped substrate structure. Possible explanations to this effect could be pre-existent intrinsic charges (charged defects or minority carriers) in the channel, which induce inversion limitations at the back interface (by peripheral inversion) or/and initial recombination of majority carriers in the channel (reducing the active carrier density) or/and current delay enhanced by the large Schottky barriers at the contacts.

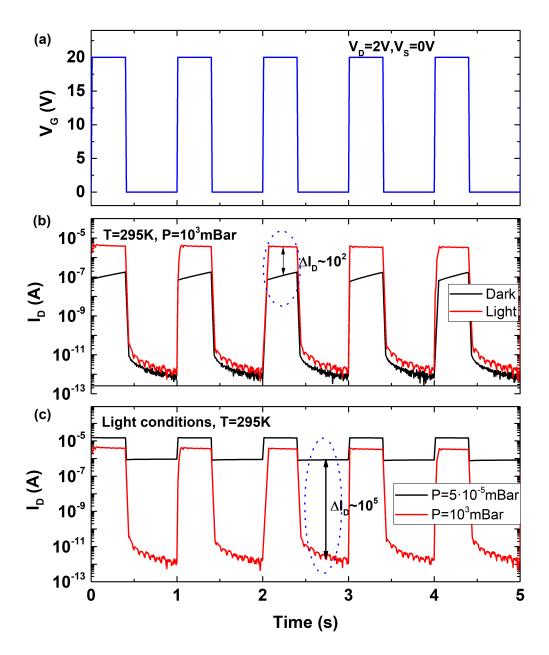

## 4. Discussion and Application

We determined the effect of the disturbing mechanisms on the transient response and the hysteresis of the MoS<sub>2</sub> devices so that they can be exploited for sensing applications. The slow initial response of the device seems to be due to the singular characteristics of the CVD-grown MoS<sub>2</sub> layer. Light or high temperature conditions alleviate it while mobile charge densities (due to adsorption) do not affect this initial limitation in the device response. This phenomenon can be exploited for light sensing as the device will present a slow response (temporally lower current) under dark conditions compared to light conditions. Figure 7 shows the device response to successive short gate voltage pulses. Figure 7a depicts the bias pattern. Figure 7b shows the response of the device under light and dark conditions. As highlighted by the dashed circle, the current operation at high voltage is around two orders of magnitude higher for the case of illuminated device. Note that this current difference is enhanced by the slow reaction of the device to dark conditions. As previously demonstrated, these devices also present a threshold voltage shift depending on pressure and temperature conditions. Absence of adsorbates and mobile ions reduces the drain current degradation reducing the threshold voltage as well. At fixed temperature, this effect can be exploited for pressure sensing. Figure 7c shows the response of the device under light conditions at room temperature under atmospheric pressure and high vacuum conditions. Due to the high carrier density induced by illumination, on-state current is similar for both pressures (fast response), however, the current decay and the threshold voltage are lower at vacuum conditions (less density of mobile ions), which means a much higher current level when the device is biased closer to  $V_G = 0$  V. This effect can be exploited to sense pressure by comparing the current level (dashed line). Another advantage is that, under controlled temperature conditions, both sensing capabilities, light and pressure can be simultaneously exploited. Comparing the current level at high gate voltages can determine the light/dark condition while differences at low gate bias can determine the pressure conditions. These results reflect that these devices can be employed as cheap light and pressure sensors without the need of complex passivation processes by just taking advantage of the inherit operational limitations.

Micromachines **2021**, 12, 646

**Figure 7.** (a) Successive back-gate pulsed biasing pattern. (b) Drain response of the device at atmospheric pressure and room temperature for illuminated and dark conditions. (c) Drain response at room temperature and light conditions for low and atmospheric pressure.

## 5. Conclusions

In this work, the electrical hysteresis and the transient response of as-synthesized  $MoS_2$  back-gated devices have been extensively analyzed. Hysteresis is governed by different degrading mechanisms. The transient response of the device determines that there is an initial delay to achieve the maximum inversion layer charge. This is mitigated at high temperature or under light conditions, pointing to lack of initial carriers as the possible origin. This effect can be exploited to design a light sensor detecting the drain current level differences. Additionally, the devices suffer from time-dependent current decay, which is induced mainly by mobile charges (adsorbates) and by carrier trapping/detrapping mechanisms. However, at low pressure conditions, the density of these mobile ions is reduced, decreasing the threshold voltage of the device and allowing for the easy detection

Micromachines **2021**, 12, 646

of pressure conditions by comparing the current level at low gate voltages. Interestingly, both sensing capabilities can be used simultaneously.

**Author Contributions:** The first authors, C.M. and N.S., conceived the framework of the article, the material fabrication, performed the experimental characterization and wrote the article; the third author, F.G. (Farzan Gity), processed the devices and performed the electrical characterization at Tyndall; the fourth author, J.C.G., fabricated the devices; the fifth author, C.N., performed and analyzed the experimental demonstration of the sensor capabilities; the sixth author, C.S., supported and funded the fabrication and structural characterization; the seventh author, P.K.H., led, supported and provided the resources for the investigation stage at Tyndall and proposed the peripheral inversion phenomenon to explain the singular results; the eighth author, E.Y.C., supported and supervised the research at ICST; the last author, F.G. (Francisco Gamiz), supervised the investigation at UGR by providing resources and analyzing the work results. All authors have read and agreed to the published version of the manuscript.

**Funding:** This project has received funding from the European Union's Horizon 2020 Research and Innovation Programme under the Marie Skłodowska-Curie grant agreement No 895322 and from the Spanish Government under Juan de la Cierva Formacion grant number FJC2018-038264-I. The Spanish Program (TEC2017-89800-R), ASCENT (EU Horizon 2020 GRANT 654384), Science Foundation Ireland through the AMBER 2 project (12/RC/2278-P2) and UGR-MADOC CEMIX 2D-EDEX project are also thanked for their financial support.

**Acknowledgments:** We thank Gioele Mirabelli, Enrico Caruso and Ray Duffy (Tyndall National Institute) for the invaluable support during project execution at Tyndall.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Frank, D.; Dennard, R.; Nowak, E.; Solomon, P.; Taur, Y.; Wong, H.-S.P. Device scaling limits of Si MOSFETs and their application dependencies. *Proc. IEEE* **2001**, *89*, 259–288. doi:10.1109/5.915374.

- 2. Rieger, M.L. Retrospective on VLSI value scaling and lithography. *J. Micro/Nanolithography MEMS MOEMS* **2019**, *18*, 1, doi:10.1117/1.jmm.18.4.040902.

- 3. Narayanan, V. High-k/Metal Gates- from research to reality. In Proceedings of the 2007 International Workshop on Physics of Semiconductor Devices, Mumbai, India, 16–20 December 2007; pp. 42–45, doi:10.1109/IWPSD.2007.4472451.

- 4. Maleville, C. Engineered substrates for Moore and more than Moore's law: Device scaling: Entering the substrate era. In Proceedings of the 2015 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference, S3S 2015, Rohnert Park, CA, USA, 5–8 October 2015; doi:10.1109/S3S.2015.7333494.

- 5. Samavedam, S.B.; Ryckaert, J.; Beyne, E.; Ronse, K.; Horiguchi, N.; Tokei, Z.; Radu, I.; Bardon, M.G.; Na, M.H.; Spessot, A.; et al. Future logic scaling: Towards atomic channels and deconstructed chips. In Proceedings of the Technical Digest—International Electron Devices Meeting, (IEDM 2020), San Francisco, CA, USA, 12–18 December 2020; pp. 1.1.1–1.1.10, doi:10.1109/IEDM13553.2020.9372023.

- 6. Del Alamo, J.A.; Antoniadis, D.A.; Lin, J.; Lu, W.; Vardi, A.; Zhao, X. III-V MOSFETs for Future CMOS. In Proceedings of the 2015 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS 2015), New Orleans, LA, USA, 11–14 October 2015; pp. 1–4, doi:10.1109/CSICS.2015.7314512.

- Heyns, M.; Tsai, W. Ultimate scaling of CMOS logic devices with Ge and III–V materials. MRS Bull. 2009, 34, 485–488, doi:10.1557/mrs2009.136.

- 8. Navarro, C.; Karg, S.; Marquez, C.; Navarro, S.; Convertino, C.; Zota, C.; Czornomaz, L.; Gamiz, F. Capacitor-less dynamic random access memory based on a III–V transistor with a gate length of 14 nm. *Nat. Electron.* **2019**, *2*, 412–419, doi:10.1038/s41928-019-0282-6.

- 9. Novoselov, K.S.; Geim, A.K.; Morozov, S.V.; Jiang, D.; Zhang, Y.; Dubonos, S.V.; Grigorieva, I.V.; Firsov, A.A. Electric Field Effect in Atomically Thin Carbon Films. *Science* **2004**, *306*, 666–669, doi:10.1126/science.1102896.

- 10. Novoselov, K.S.; Jiang, D.; Schedin, F.; Booth, T.J.; Khotkevich, V.V.; Morozov, S.V.; Geim, A.K. Two-dimensional atomic crystals. *Proc. Natl. Acad. Sci. USA* **2005**, *102*, 10451–10453, doi:10.1073/pnas.0502848102.

- 11. Salazar, N.; Marquez, C.; Gamiz, F. Synthesis of graphene and other two-dimensional materials. In 2D Materials for Nanophotonics; Elsevier: Amsterdam, The Netherlands, 2021; pp. 1–79, doi:10.1016/B978-0-12-818658-9.00006-5.

- 12. Chhowalla, M.; Jena, D.; Zhang, H. Two-dimensional semiconductors for transistors. *Nat. Rev. Mater.* **2016**, *1*, 1–15, doi:10.1038/natrevmats.2016.52.

- 13. Mitta, S.B.; Choi, M.S.; Nipane, A.; Ali, F.; Kim, C.; Teherani, J.T.; Hone, J.; Yoo, W.J. Electrical characterization of 2D materials-based field-effect transistors. 2D Materials 2021, 8, 012002, doi:10.1088/2053-1583/abc187.

Micromachines **2021**, 12, 646 12 of 13

14. Yu, Z.G.; Yakobson, B.I.; Zhang, Y.W. Realizing Indirect-to-Direct Band Gap Transition in Few-Layer Two-Dimensional MX2 (M = Mo, W; X = S, Se). ACS Appl. Energy Mater. 2018, 1, 4115–4121, doi:10.1021/acsaem.8b00774.

- 15. Yu, C. The 3rd dimension-More Life for Moore's Law. In Proceedings of the 2006 International Microsystems, Package, Assembly Conference Taiwan, Taipei, Taiwan, 18–20 October 2006; No. 8, pp. 1–6, doi:10.1109/IMPACT.2006.312181.

- 16. Banerjee, K.; Souri, S.J.; Kapur, P.; Saraswat, K.C. 3-D ICs: A novel chip design for improving deep-submieroraeter interconnect performance and systems-on-chip integration and systems-on-chip integration. *Proc. IEEE* **2001**, *89*, 602–632, doi:10.1109/5.929647.

- 17. Kang, J.; Cao, W.; Xie, X.; Sarkar, D.; Liu, W.; Banerjee, K. Graphene and beyond-graphene 2D crystals for next-generation green electronics. In Proceedings of the Micro- and Nanotechnology Sensors, Systems, and Applications VI, Baltimore, MD, USA, 5–9 May 2014; doi:10.1117/12.2051198.

- 18. Jiang, J.; Parto, K.; Cao, W.; Banerjee, K. Ultimate Monolithic-3D Integration With 2D Materials: Rationale, Prospects, and Challenges. *IEEE J. Electron Devices Soc.* **2019**, *7*, 878–887. doi:10.1109/jeds.2019.2925150.

- 19. Lo, C.L.; Helfrecht, B.A.; He, Y.; Guzman, D.M.; Onofrio, N.; Zhang, S.; Weinstein, D.; Strachan, A.; Chen, Z. Opportunities and challenges of 2D materials in back-end-of-line interconnect scaling. *J. Appl. Phys.* **2020**, *128*, 080903, doi:10.1063/5.0013737.

- Bhattacharjee, S.; Caruso, E.; McEvoy, N.; Ó Coileáin, C.; O'Neill, K.; Ansari, L.; Duesberg, G.S.; Nagle, R.; Cherkaoui, K.; Gity, F.; Hurley, P.K. Insights into Multilevel Resistive Switching in Monolayer MoS<sub>2</sub>. ACS Appl. Mater. Interfaces 2020, 12, 6022–6029, doi:10.1021/acsami.9b15677.

- 21. Samnakay, R.; Jiang, C.; Rumyantsev, S.L.; Shur, M.S.; Balandin, A.A. Selective chemical vapor sensing with few-layer MoS<sub>2</sub> thin-film transistors: Comparison with graphene devices. *Appl. Phys. Lett.* **2015**, *106*, 1–6, doi:10.1063/1.4905694.

- 22. Late, D.J.; Huang, Y.K.; Liu, B.; Acharya, J.; Shirodkar, S.N.; Luo, J.; Yan, A.; Charles, D.; Waghmare, U.V.; Dravid, V.P.; et al. Sensing behavior of atomically thin-layered MoS<sub>2</sub> transistors. *ACS Nano* **2013**, *7*, 4879–4891, doi:10.1021/nn400026u.

- 23. Huyghebaert, C.; Schram, T.; Smets, Q.; Kumar Agarwal, T.; Verreck, D.; Brems, S.; Phommahaxay, A.; Chiappe, D.; El Kazzi, S.; Lockhart de la Rosa, C.; et al. 2D materials: roadmap to CMOS integration. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; Volume 1, pp. 22.1.1–22.1.4, doi:10.1109/IEDM.2018.8614679.

- 24. Huang, J.K.; Pu, J.; Hsu, C.L.; Chiu, M.H.; Juang, Z.Y.; Chang, Y.H.; Chang, W.H.; Iwasa, Y.; Takenobu, T.; Li, L.J. Large-area synthesis of highly crystalline WSe<sub>2</sub> monolayers and device applications. *ACS Nano* **2014**, *8*, 923–930, doi:10.1021/nn405719x.

- 25. Wang, J.; Yao, Q.; Huang, C.W.; Zou, X.; Liao, L.; Chen, S.; Fan, Z.; Zhang, K.; Wu, W.; Xiao, X.; et al. High Mobility MoS<sub>2</sub> Transistor with Low Schottky Barrier Contact by Using Atomic Thick h-BN as a Tunneling Layer. *Adv. Mater.* **2016**, *28*, 8302–8308, doi:10.1002/adma.201602757.

- Illarionov, Y.Y.; Smithe, K.K.H.; Waltl, M.; Knobloch, T.; Pop, E.; Grasser, T. Improved Hysteresis and Reliability of MoS<sub>2</sub>

Transistors With High-Quality CVD Growth and Al<sub>2</sub>O<sub>3</sub> Encapsulation. *IEEE Electron Device Lett.* 2017, 38, 1763–1766, doi:10.1109/LED.2017.2768602.

- 27. Illarionov, Y.Y.; Banshchikov, A.G.; Polyushkin, D.K.; Wachter, S.; Knobloch, T.; Thesberg, M.; Mennel, L.; Paur, M.; Stöger-Pollach, M.; Steiger-Thirsfeld, A.; et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. *Nat. Electron.* **2019**, 2, 230–235, doi:10.1038/s41928-019-0256-8.

- 28. Bhattacharjee, S.; Ganapathi, K.L.; Nath, D.N.; Bhat, N. Surface State Engineering of Metal/MoS<sub>2</sub> Contacts Using Sulfur Treatment for Reduced Contact Resistance and Variability. *IEEE Trans. Electron Devices* **2016**, *63*, 2556–2562, doi:10.1109/TED.2016.2554149.

- 29. Han, X.; Lin, J.; Liu, J.; Wang, N.; Pan, D. Effects of Hexagonal Boron Nitride Encapsulation on the Electronic Structure of Few-Layer MoS 2. *J. Phys. Chem. C* **2019**, 123, 14797–14802, doi:10.1021/acs.jpcc.9b02549.

- 30. Liu, H.; Li, D.; Ma, C.; Zhang, X.; Sun, X.; Zhu, C.; Zheng, B.; Zou, Z.; Luo, Z.; Zhu, X.; et al. Van der Waals epitaxial growth of vertically stacked Sb<sub>2</sub>Te<sub>3</sub>/MoS<sub>2</sub> p–n heterojunctions for high performance optoelectronics. *Nano Energy* **2019**, *59*, 66–74, doi:10.1016/j.nanoen.2019.02.032.

- 31. McDonnell, S.; Addou, R.; Buie, C.; Wallace, R.M.; Hinkle, C.L. Defect-Dominated Doping and Contact Resistance in MoS 2. ACS Nano 2014, 8, 2880–2888, doi:10.1021/nn500044q.

- 32. Marquez, C.; Salazar, N.; Gity, F.; Navarro, C.; Mirabelli, G.; Galdon, J.C.; Duffy, R.; Navarro, S.; Hurley, P.K.; Gamiz, F. Investigating the transient response of Schottky barrier back-gated MoS<sub>2</sub> transistors. 2D Materials **2020**, 7, 025040, doi:10.1088/2053-1583/ab7628.

- 33. Li, H.; Zhang, Q.; Yap, C.C.R.; Tay, B.K.; Edwin, T.H.T.; Olivier, A.; Baillargeat, D. From Bulk to Monolayer MoS<sub>2</sub>: Evolution of Raman Scattering. *Adv. Funct. Mater.* **2012**, 22, 1385–1390, doi:10.1002/adfm.201102111.

- 34. Mishra, P.; Tangi, M.; Ng, T.K.; Hedhili, M.N.; Anjum, D.H.; Alias, M.S.; Tseng, C.C.; Li, L.J.; Ooi, B.S. Impact of N-plasma and Ga-irradiation on MoS<sub>2</sub> layer in molecular beam epitaxy. *Appl. Phys. Lett.* **2017**, *110*, 012101, doi:10.1063/1.4973371.

- 35. Chroboczek, J. Automatic, wafer-level, low frequency noise measurements for the interface slow trap density evaluation. In Proceedings of the International Conference on Microelectronic Test Structures, 2003, Monterey, CA, USA, 17–20 March 2003; pp. 95–98, doi:10.1109/ICMTS.2003.1197409.

- 36. Di Bartolomeo, A.; Genovese, L.; Foller, T.; Giubileo, F.; Luongo, G.; Croin, L.; Liang, S.J.; Ang, L.K.; Schleberger, M. Electrical transport and persistent photoconductivity in monolayer MoS<sub>2</sub> phototransistors. *Nanotechnology* **2017**, *28*, 214002, doi:10.1088/1361-6528/aa6d98.

- 37. Marquez, C.; Salazar, N.; Gity, F.; Navarro, C.; Mirabelli, G.; Duffy, R.; Galdon, J.; Navarro, S.; Hurley, P.K.; Gamiz, F. CVD-grown back-gated MoS 2 transistors. In Proceedings of the 2020 Joint International EUROSOI Workshop and International Conference

Micromachines **2021**, 12, 646

- on Ultimate Integration on Silicon (EUROSOI-ULIS), Caen, France, 1–30 September 2020; pp. 1–4, doi:10.1109/EUROSOI-ULIS49407.2020.9365295.

- 38. Di Bartolomeo, A.; Grillo, A.; Urban, F.; Iemmo, L.; Giubileo, F.; Luongo, G.; Amato, G.; Croin, L.; Sun, L.; Liang, S.J.; et al. Asymmetric Schottky Contacts in Bilayer MoS<sub>2</sub> Field Effect Transistors. *Adv. Funct. Mater.* **2018**, 28, 1800657, doi:10.1002/adfm.201800657.

- 39. Das, S.; Chen, H.Y.; Penumatcha, A.V.; Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano Lett.* **2013**, *13*, 100–105, doi:10.1021/nl303583v.

- 40. Qiu, H.; Pan, L.; Yao, Z.; Li, J.; Shi, Y.; Wang, X. Electrical characterization of back-gated bi-layer MoS<sub>2</sub> field-effect transistors and the effect of ambient on their performances. *Appl. Phys. Lett.* **2012**, *100*, 123104, doi:10.1063/1.3696045.

- 41. Illarionov, Y.Y.; Rzepa, G.; Waltl, M.; Knobloch, T.; Grill, A.; Furchi, M.M.; Mueller, T.; Grasser, T. The role of charge trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN field-effect transistors. *2D Materials* **2016**, *3*, 035004, doi:10.1088/2053-1583/3/3/035004.

- 42. Late, D.J.; Liu, B.; Matte, H.S.S.R.; Dravid, V.P.; Rao, C.N.R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. *ACS Nano* **2012**, *6*, 5635–5641, doi:10.1021/nn301572c.

- 43. Shu, J.; Wu, G.; Guo, Y.; Liu, B.; Wei, X.; Chen, Q. The intrinsic origin of hysteresis in MoS<sub>2</sub>field effect transistors. *Nanoscale* **2016**, 8, 3049–3056, doi:10.1039/c5nr07336g.

- O'Connor, É.; Cherkaoui, K.; Monaghan, S.; O'Connell, D.; Povey, I.; Casey, P.; Newcomb, S.B.; Gomeniuk, Y.Y.; Provenzano, G.; Crupi, F.; et al. Observation of peripheral charge induced low frequency capacitance-voltage behaviour in metal-oxide-semiconductor capacitors on Si and GaAs substrates. J. Appl. Phys. 2012, 111, 124104, doi:10.1063/1.4729331.

- 45. Mahapatra, S.; Goel, N.; Desai, S.; Gupta, S.; Jose, B.; Mukhopadhyay, S.; Joshi, K.; Jain, A.; Islam, A.E.; Alam, M.A. A comparative study of different physics-based NBTI models. *IEEE Trans. Electron Devices* **2013**, *60*, 901–916, doi:10.1109/TED.2013.2238237.

- 46. Marquez, C.; Rodriguez, N.; Fernandez, C.; Ohata, A.; Gamiz, F.; Allibert, F.; Cristoloveanu, S. In situ characterization of bias instability in bare SOI wafers by pseudo-MOSFET technique. *IEEE Trans. Device Mater. Reliab.* **2014**, *14*, 878–883, doi:10.1109/TDMR.2014.2332818.

- 47. Cristoloveanu, S.; Li, S.S. Electrical Characterization of Silicon-on-Insulator Materials and Devices; Springer: Boston, MA, USA, 1995; doi:10.1007/978-1-4615-2245-4.