# Reliability Study of Thin-Oxide Zero-Ionization, Zero-Swing FET 1T-DRAM Memory Cell

Santiago Navarro, Carlos Navarro, Carlos Marquez, Norberto Salazar, Philippe Galy, Sorin Cristoloveanu and Francisco Gamiz

Abstract—Experimental time-dependent dielectric breakdown and ON voltage reliability of advanced FD-SOI Z<sup>2</sup>-FET memory cells are characterized for the first time. The front-gate stress time is shown to significantly modulate the ON voltage, hence the memory window. The Weibull slope,  $\beta$ , indicating the device variability to breakdown and the time to soft breakdown,  $\alpha$ , present different trends depending on the cell geometry. This fact highlights the trade-off between variability and reliability to account for in Z<sup>2</sup>-FET designs.

*Index Terms*—Z<sup>2</sup>-FET, FD-SOI, PIN, DRAM, Reliability, Time Dependent Dielectric Breakdown, Weibull, Capacitor-less.

#### I. INTRODUCTION

**M**ODERN VLSI process is based upon aggresive dimension scaling and ultra low power consumption strategies. Several deteriorating effects arise from these approaches, being the electric field that the gate oxide supports one of the most important. Over the last CMOS technology generations this oxide field has increased by several MV/cm [1]. This implies a higher gate leakage current and oxide reliability issues which may even render a device unusable.

The Zero Subthreshold Swing and Zero Impact Ionization FET  $(Z^2$ -FET) [2] behaves as a 1-transistor DRAM (1T-DRAM) memory cell aimed to replace traditional 1-transistor, 1-capacitor DRAM cells due to its potentially smaller footprint and enhanced current ratio [3]. Unlike most other 1T-DRAM cells [4]-[6], the Z<sup>2</sup>-FET operation is not based on any degrading mechanism such as band-to-band tunneling or impact ionization, being outstanding in terms of reliability. Z<sup>2</sup>-FET reliability analysis is of primary importance when millions of memory cells are integrated within the same circuit and a cell failure could lead to data corruption. In this work, the  $Z^2$ -FET operation at high temperature is initially analyzed and reliability measurements are then carried out: i) the  $Z^2$ -FET ON voltage and ON current are measured after front-gate bias stress; ii) the front-gate time-dependent dielectric breakdown (TDDB) is characterized extracting both the Weibull slope,  $\beta$ , and time-to-breakdown,  $\alpha$ , for Z<sup>2</sup>-FET devices featuring different dimensions. The back-interface reliability is not as relevant for memory operation since the buried-oxide (BOX, Fig. 1) thickness is approximately 25 nm, thus the vertical electric field is much weaker than at the front-gate oxide. Note

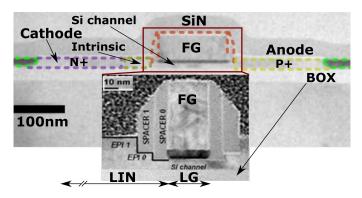

Fig. 1. Cross-section TEM image illustrating the Z<sup>2</sup>-FET structure. The inset shows a closer gate-stack picture of a different Z<sup>2</sup>-FET featuring distinct geometry.  $t_{Epi0} + t_{Epi1} \simeq 15 \ nm, t_{Si} \simeq 7 \ nm, t_{BOX} \simeq 25 \ nm.$

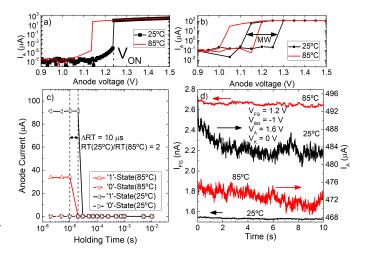

Fig. 2. a)  $I_A$ - $V_A$  sweep indicating the point where  $V_A$  is equal to  $V_{ON}$  for room temperature (25°*C*) and 85°*C*. b) MW shift to lower voltage as temperature increases. c) RT for both temperatures indicating the time penalty and '1'-state instability under mentioned conditions. d) Front-gate tunnel SILC: initially the SILC decreases until it stabilizes.  $V_{FG} = 1.2 V$ ,  $V_{BG} = -1 V$  and  $V_K = 0 V$  in all experiments unless otherwise noted. W = 1000 *nm*,  $L_G = 200 nm$ ,  $L_{IN} = 200 nm$ .

that the common back-gate voltage is fixed to -1 V or even less negative (closer to 0 V) [7].

### II. CHARACTERIZATION SETUP

Devices under test have been fabricated by ST-Microelectronics [8]. Advanced 28 nm node FD-SOI Z<sup>2</sup>-FETs featuring a metal Silicide/Poly/TiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stack with approximately 3.1 nm of thickness (EOT  $\simeq 1.5$  nm) are studied. No oxide corner rounding, enhancing the

S. Navarro, C. Navarro, C. Marquez, N. Salazar and F. Gamiz are with the CITIC-UGR and the Department of Electronics, University of Granada, Spain (e-mail: navarromoral@ugr.es).

P. Galy is with STMicroelectronics, France.

S. Cristoloveanu is with IMEP-LAHC, Grenoble INP Minatec, France. H2020 REMINDER project (grant agreement No 687931) and TEC2017-89800-R are thanked for financial support.

electric field, has been observed based on lithography mask simulations. The Z<sup>2</sup>-FET cell resembles a conventional PIN diode, Fig. 1, in which the intrinsic region is partially covered by a front gate (FG), defining the gated and ungated intrinsic regions whose lengths are  $L_G$  and  $L_{IN}$ , respectively. The FG is adjacent to the forward-biased anode (A) contact, while the cathode (K) contact lies at the other side. A bottom back gate (BG) covers the whole PIN structure. Thanks to complementary top and back gate bias ( $V_{FG} > 0 V \& V_{BG}$ < 0 V) a virtual NPNP structure is emulated: the gated region and the cathode behave as N-type and the ungated region and the anode as P-type semiconductors. Two distinct current levels (I<sub>1</sub> and I<sub>0</sub>, associated to each logic state) are achieved based on the stored charge under the gate. The  $Z^2$ -FET operation as memory cell can be found in [7], [9].

# III. RESULTS

## A. Memory parameter dependence on temperature

Fig. 2a demonstrates the typical  $Z^2$ -FET operation exhibiting the characteristic sharp current switch. The ON voltage  $(V_{ON})$ , defined as the anode bias at which the current onset arises [10], Fig. 2a) is reduced by increasing the temperature as previously reported [11] due to carrier energy increase, which enables them to surmount the potential barriers from cathode and anode to channel. A similar shift to lower anode bias is observed for the memory window (MW, defined as the  $V_{ON}$ difference between the '1' and '0'-programmed state), Fig. 2b. Nor the memory window or the current margin  $(I_1-I_0)$ are affected by the high operation temperature. A lower  $V_{ON}$ is useful for power consumption reduction with no current level penalty. Nevertheless, the retention time (RT, the time a certain logic state is held) is reduced to 10  $\mu s$  when the temperature increases to  $85^{\circ}C$  (Fig. 2c), as occurs for most DRAM cells [12]. The front-gate tunnel leakage current is primary responsible of the RT penalty together with Shockley-Read-Hall (SRH) recombination [13] and trapping/detrapping events. Fig. 2d shows a gate-leakage current increase of about 50% when the temperature is increased.

# B. V<sub>ON</sub> & I<sub>ON</sub> evolution under stress conditions

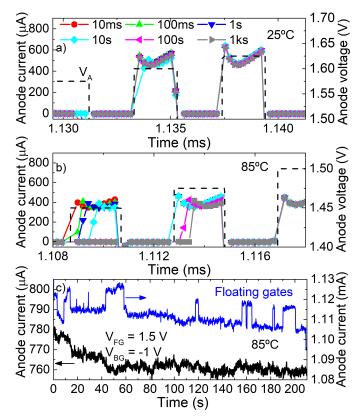

The Z<sup>2</sup>-FET device is stressed by applying a constant voltage stress (CVS) at the front gate ( $V_{FG_ST} = 1.5 V$ ) for a fixed time.  $V_{FG_ST}$  is set to exceed the operating bias intended for 1T-DRAM usage while  $V_A$  is set to 1.6 V to ensure the device is not in OFF state.  $V_{ON}$  is monitored by pulsing the anode voltage (increasing the pulse height by 25 mV every cycle and maintaining the same  $V_{FG}$ ) immediately after stressing to avoid relaxation. Fig. 3a-b show the transient anode current  $I_A$  at room and high temperatures for different stress times. The sudden current onset indicates the minimum  $V_A$  to overcome the energy barriers, i.e.  $V_{ON}$ . At room temperature  $I_A$  sharply rises at the same point (the second shown pulse in Fig. 3a) for all stress times, proving it is independent of stress conditions.

In contrast, at 85°C (Fig. 3b) the Z<sup>2</sup>-FET triggering arises earlier for shorter stress times. The longer the stress time, the larger the  $V_{ON}$  shift. Variations of 50 mV or even larger

Fig. 3.  $V_{ON}$  evolution at a) room and b) high temperature for different stress times. Distinct time scales have been used for a) and b) since  $V_{ON}$  changes as a function of temperature. c)  $I_{ON}$  with (upper curve) and without (lower curve) floating gates at 85°*C*.  $V_{FG}$  = 1.5 *V*,  $V_{BG}$  = -1 *V*,  $V_A$  = 1.6 *V*. W = 1000 nm,  $L_G$  = 150 nm,  $L_{IN}$  = 200 nm.

are observed for stress times longer than 10 s, after which the  $V_{ON}$  increase seems to saturate, Fig. 3b. Both the  $V_{ON}$ independence at room temperature and the  $V_{ON}$  increase at high temperature with the stress time trends have the same origin: at room temperature the electron reservoir under the front gate is not depleted even with the longest stress time. On the contrary, at 85°*C*, the longer the stress, the more electrons tunnel through the front gate increasing  $V_{ON}$ .

The lower curve in Fig. 3c shows the on-the-fly current, namely  $I_{ON}$  when  $V_A > V_{ON}$ , as a function of the stress time for the same  $V_A$  and  $V_{FG_ST}$  values as mentioned above. The initial decay indicates bias temperature instability (BTI) degradation by two possible mechanisms [14]: i) interface states, acceptor-like presumably, are created by charged H ions as predicted by the Reaction & Difussion model [15] in which carriers are trapped; ii) possitive oxide charge (screening the  $V_{FG}$ - $V_{BG}$  induced electric field) is built up as a consequence of charge interaction among oxide species [14]. BTI scenario is verified by repeating the experiment with both gates left floating, Fig. 3c upper curve. As observed the current does not present any BTI degradation and only reveals typical random telegraph noise (RTN) fluctuations. A higher current level is measured when the gates are floating due to the absence of gate-induced energy barriers blocking carrier injection.

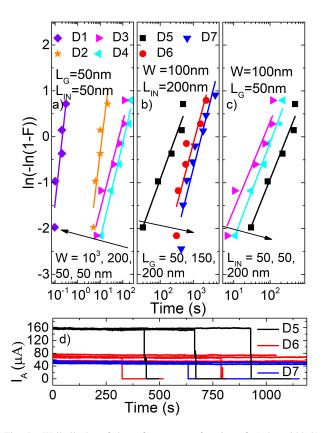

Fig. 4. Weibull plot of the soft  $t_{BD}$  as a function of a) the width b)  $L_G$  c)  $L_{IN}$ . a) Illustrates a high Weibull  $\beta$  for W = 1 and W = 0.2  $\mu m$  and a medium slope factor for W = 100 nm. b)  $\beta$  slightly increases as the gate length is made larger. c)  $\beta$  slopes are almost parallel. d) anode current,  $I_A$ , for D5 (160  $\mu A$ ), D6 (75  $\mu A$ ) and D7 (55  $\mu A$ ).  $V_{FG}$  = 3 V,  $V_A$  = 1.5 V,  $V_{BG}$  = 0 V,  $t_{OX}$  = 3.1 nm.

## C. Front-gate Time Dependent Dielectric Breakdown

The cell dimensions of devices employed in this work are reported in Table I. The Z<sup>2</sup>-FET TDDB was measured at high temperature (85°C, typical in DRAM cells) and high frontgate voltage (3 V) to cause operation failure at reasonable times for all Z<sup>2</sup>-FET geometries. As indicated in [16], constant voltage stress is more appropriate than constant current stress for ultra-thin oxides due to the ballistic interaction of electrons with the dielectric. The random nature of oxide breakdown is generally described by the Weibull distribution [17]  $F(t) = 1 - exp(-(t/\alpha)^{\beta})$  where F is the cumulative distribution function (CDF) representing the cumulative fraction of breakdown/wornout devices, t is the stress time,  $\alpha$  is the characteristic life and  $\beta$  is the Weibull slope.

Measurements report an initial decrease of stress-induced

TABLE I DIMENSIONS(nm) and obtained Weibull  $\beta(-)$  and  $\alpha(s)$  of reported devices in this work.

| Dev.     | D1   | D2   | D3   | D4    | D5    | D6     | D7     |

|----------|------|------|------|-------|-------|--------|--------|

| W        | 1000 | 200  | 100  | 100   | 100   | 100    | 100    |

| $L_G$    | 50   | 50   | 50   | 50    | 50    | 150    | 200    |

| $L_{IN}$ | 50   | 50   | 50   | 50    | 200   | 200    | 200    |

| β        | 1.95 | 1.74 | 0.92 | 0.83  | 0.86  | 1.17   | 1.24   |

| $\alpha$ | 0.21 | 12.2 | 68.7 | 117.5 | 290.7 | 1130.7 | 1752.4 |

leakage current (SILC) (Fig. 2d shows the same trend for a different bias) when increasing the stress time which suggests that electrons are trapped in the dielectric [18]. After some time, the SILC becomes constant, which is key for 1T-DRAM memory cells since it is related to the retention time. Fig. 4 represents the Weibull cumulative distribution as a function of the time to soft breakdown ( $t_{BD}$ ), obtained by varying one cell dimension parameter at a time.  $t_{BD}$  is measured when an instantaneous current increase of 5% occurs after the front-gate current has settled down.

Fig. 4a shows the dependence of the Weibull parameters on the cell width (note that D3 and D4 feature the same dimensions). As expected  $t_{BD}$  increases in narrow devices since the dielectric area is smaller, in accordance with the percolation model [17]. The wider cells (D1, D2) feature higher  $\beta$  than their W = 100 nm counterparts, see Table 1. A trade-off arises then between the breakdown variability,  $\beta$ (the higher the less deviation among devices), and the time to breakdown,  $\alpha$  (the longer the more robust), preventing the optimization of both parameters simultaneously. According to the cell-based model [19], the reduction of  $\beta$  with the device width scaling suggests either a greater lattice constant or a lower defect generation rate. Fig. 4b illustrates the dependence on  $L_G$ , where all curves exhibit similar slopes. Interestingly,  $t_{BD}$  increases as  $L_G$  is made longer (i.e. more dielectric area). The reason is the higher anode current measured for shorter  $L_G$  cells (Fig. 4d, D5 anode current, doubles that of D6 and D7). The larger the anode current, the more degradation the dielectric suffers (as happened when  $V_{ON}$  is reduced, not shown). Fig. 4c depicts the impact of  $L_{IN}$  where the Weibull slopes are almost parallel suggesting similar variability to breakdown: the intrinsic region does not significantly impact the oxide properties.

## IV. CONCLUSION

The Z<sup>2</sup>-FET ON voltage, memory window, and retention time have been experimentally studied at 85°C.  $V_{ON}$  is insensitive to the applied front-gate stress at room temperature, while at 85°C a 50 mV increase is observed for stress times longer than 10 s. The ON current is affected by BTI degradation and RTN fluctuations produced by interface and oxide trapping effects. The TDDB analysis shows lower breakdown variability for wider cells but shortest time to breakdown evidencing a trade-off between reliability and variability. The time to breakdown is also shown to be more affected by the lateral electric field than by the dielectric area. The reported results highlight the design strategy towards more robust Z<sup>2</sup>-FET memory matrices in terms of footprint and reliability.

# REFERENCES

- R. Degraeve, B. Kaczer, and G. Groeseneken, "Degradation and breakdown in thin oxide layers: mechanisms, models and reliability prediction," *Springer Tracts in Modern Physics*, vol. 274, pp. 3–22, 1999. DOI: 10.1007/978-3-319-63577-4\_1

- [2] J. Wan, C. Le Royer, A. Zaslavsky, and S. Cristoloveanu, "A compact capacitor-less high-speed DRAM using field effect-controlled charge regeneration," *IEEE Electron Device Letters*, vol. 33, no. 2, pp. 179–181, 2012. DOI: 10.1109/LED.2011.2176908

- [3] C. Navarro, M. Duan, M. S. Parihar, F. Adamu-Lema, S. Coseman, J. Lacord, K. Lee, C. Sampedro, B. Cheng, H. El Dirani, J. C. Barbe, P. Fonteneau, S. I. Kim, S. Cristoloveanu, M. Bawedin, C. Millar, P. Galy, C. Le Royer, S. Karg, H. Riel, P. Wells, Y. T. Kim, A. Asenov, and F. Gamiz, "Z2-FET as Capacitor-Less eDRAM Cell for High-Density Integration," *IEEE Transactions on Electron Devices*, vol. 64, no. 12, pp. 4904–4909, 2017. DOI: 10.1109/TED.2017.2759308

- [4] S. Okhonin, M. Nagoga, J. Sallese, and P. Fazan, "A SOI capacitor-less 1T-DRAM concept," in 2001 IEEE International SOI Conference. Proceedings (Cat. No.01CH37207). IEEE, 2002, pp. 153–154. DOI: 10.1109/soic.2001.958032

- [5] M. Bawedin, S. Cristoloveanu, and D. Flandre, "A capacitorless 1T-DRAM on SOI based on dynamic coupling and double-gate operation," *IEEE Electron Device Letters*, vol. 29, no. 7, pp. 795–798, 2008. DOI: 10.1109/LED.2008.2000601

- [6] N. Rodriguez, C. Navarro, F. Gamiz, F. Andrieu, O. Faynot, and S. Cristoloveanu, "Experimental demonstration of capacitorless A2RAM cells on silicon-on-insulator," *IEEE Electron Device Letters*, vol. 33, no. 12, pp. 1717–1719, 2012. DOI: 10.1109/LED.2012.2221074

- [7] C. Navarro, J. Lacord, M. S. Parihar, F. Adamu-Lema, M. Duan, N. Rodriguez, B. Cheng, H. El Dirani, J. C. Barbe, P. Fonteneau, M. Bawedin, C. Millar, P. Galy, C. Le Royer, S. Karg, P. Wells, Y. T. Kim, A. Asenov, S. Cristoloveanu, and F. Gamiz, "Extended Analysis of the Z2-FET: Operation as Capacitorless eDRAM," *IEEE Transactions on Electron Devices*, vol. 64, no. 11, pp. 4486–4491, 2017. DOI: 10.1109/TED.2017.2751141

- [8] N. Planes, O. Weber, V. Barral, S. Haendler, D. Noblet, D. Croain, M. Bocat, P. O. Sassoulas, X. Federspiel, A. Cros, A. Bajolet, E. Richard, B. Dumont, P. Perreau, D. Petit, D. Golanski, C. Fenouillet-Béranger, N. Guillot, M. Rafik, V. Huard, S. Puget, X. Montagner, M. A. Jaud, O. Rozeau, O. Saxod, F. Wacquant, F. Monsieur, D. Barge, L. Pinzelli, M. Mellier, F. Boeuf, F. Arnaud, and M. Haond, "28nm FDSOI technology platform for high-speed low-voltage digital applications," *Digest of Technical Papers - Symposium on VLSI Technology*, vol. 33, no. 4, pp. 133–134, 2012. DOI: 10.1109/VLSIT.2012.6242497

- [9] S. Cristoloveanu, K. Lee, M. Parihar, H. El Dirani, J. Lacord, S. Martinie, C. Le Royer, J.-C. Barbe, X. Mescot, P. Fonteneau, P. Galy, F. Gamiz, C. Navarro, B. Cheng, M. Duan, F. Adamu-Lema, A. Asenov, Y. Taur, Y. Xu, Y.-T. Kim, J. Wan, and M. Bawedin, "A review of the Z 2 -FET 1T-DRAM memory: Operation mechanisms and key parameters," *Solid-State Electronics*, no. xxxx, 2017. DOI: 10.1016/j.sse.2017.11.012

- [10] S. Navarro, K. H. Lee, C. Marquez, C. Navarro, M. Parihar, H. Park, P. Galy, M. Bawedin, F. Gamiz, and S. Cristoloveanu, "Evaluation of thin-oxide Z2-FET DRAM cell," 2018 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, EUROSOI-ULIS 2018, vol. 2018-Janua, pp. 1–4, 2018. DOI: 10.1109/ULIS.2018.8354342

- [11] H. El Dirani, Y. Solaro, P. Fonteneau, P. Ferrari, and S. Cristoloveanu, "Solid-State Electronics Properties and mechanisms of Z 2 -FET at variable temperature," *Solid State Electronics*, vol. 115, pp. 201–206, 2016. DOI: 10.1016/j.sse.2015.08.015

- [12] J. Liu, B. Jaiyen, Y. Kim, C. Wilkerson, and O. Mutlu, "An experimental study of data retention behavior in modern DRAM devices," *Proceedings of the 40th Annual International Symposium on Computer Architecture - ISCA '13*, vol. 41, no. 3, p. 60, 2013. DOI: 10.1145/2485922.2485928

- [13] M. Duan, C. Navarro, B. Cheng, F. Adamu-Lema, X. Wang, V. P. Georgiev, F. Gamiz, C. Millar, and A. Asenov, "Thorough Understanding of Retention Time of Z2FET Memory Operation," *IEEE Transactions on Electron Devices*, vol. 66, no. 1, pp. 383–388, 2019. DOI: 10.1109/TED.2018.2877977

- [14] D. K. Schroder, "Negative bias temperature instability: What do we understand?" vol. 47, pp. 841–852, 2007. DOI: 10.1016/j.microrel. 2006.10.006

- [15] K. O. Jeppson and C. M. Svensson, "devices Negative bias stress of MOS devices at high electric fields and degradation of MNOS devices," vol. 2004, no. 1977, 2004. DOI: 10.1063/1.323909

- [16] T. Nigam, R. Degraeve, and H. E. Maes, "Constant current charge-tobreakdown," 1998 IEEE International Reliability Physics Symposium Proceedings. 36th Annual (Cat. No.98CH36173), Reno, NV, USA, pp. 62–69, 1998. DOI: 10.1109/RELPHY.1998.670444

- [17] J. H. Stathis, "Percolation models for gate oxide breakdown," *Journal of Applied Physics*, vol. 86, no. 10, pp. 5757–5766, 1999. DOI: 10.1063/1.371590

- [18] C.-H. Hsu, M.-T. Wang, and J. Y.-M. Lee, "Electrical characteristics and reliability properties of metal-oxide-semiconductor capacitors with HfZrLaO gate dielectrics," *Microelectronics Reliability*, vol. 50, no. 5, pp. 599–602, 2006. DOI: 10.1016/j.microrel.2010.01.014

- [19] J. Suñé, "New physics-based analytic approach to the thin-oxide breakdown statistics," *IEEE Electron Device Letters*, vol. 22, no. 6, pp. 296–298, 2001. DOI: 10.1109/55.924847