#### UNIVERSIDAD DE GRANADA

DEPARTAMENTO DE ELECTRÓNICA Y TECNOLOGÍA DE COMPUTADORES

#### TESIS DOCTORAL

### Study and Simulation of Advanced Si–based Nanodevices: Schottky–Barrier MOSFETs and Tunnel FETs

JOSÉ LUIS PADILLA DE LA TORRE Granada, 2012

Editor: Universidad de Granada. Tesis Doctorales Autor: José Luis Padilla de la Torre ISBN: 978-84-9125-826-1 URI: http://hdl.handle.net/10481/43553 A todos los que la presente vieren y entendieren: sabed  $[\ldots]$

FRANCISCO JESÚS GÁMIZ PÉREZ y ANDRÉS GODOY MEDINA, Catedráticos de Universidad del Área de Electrónica de la Universidad de Granada,

AUTORIZAN

La presentación de la memoria de investigación titulada "Study and Simulation of Advanced Si-based Nanodevices: Schottky-Barrier MOS-FETs and Tunnel FETs" realizada por **D. José Luis Padilla de la Torre** para optar al TÍTULO DE DOCTOR CON MENCIÓN INTER-NACIONAL por la Universidad de Granada, y que ha sido desarrollada en su totalidad bajo su dirección en el Grupo de Investigación en Nanoelectrónica (TIC-216) del Departamento de Electrónica y Tecnología de Computadores de la Universidad de Granada.

Granada, trece de julio del dos mil doce

Francisco Jesús Gámiz Pérez Catedrático de Universidad Universidad de Granada Andrés Godoy Medina Catedrático de Universidad Universidad de Granada

TESIS DOCTORAL: Study and Simulation of Advanced Si-based Nanodevices: Schottky-Barrier MOSFETs and Tunnel FETs

AUTOR: D. José Luis Padilla de la Torre Licenciado en Física

DIRECTORES: D. Francisco Jesús Gámiz Pérez Doctor en Física Catedrático de Universidad

D. Andrés Godoy Medina Doctor en Física Catedrático de Universidad

DEPARTAMENTO: Electrónica y Tecnología de Computadores Universidad de Granada

El Tribunal de Calificación queda compuesto por:

PRESIDENTE: VOCAL SECRETARIO: VOCALES:

Celebrado el acto de defensa y lectura de la Tesis en Granada a día ..... de ..... del año ..... en la Facultad de Ciencias de la Universidad de Granada.

El tribunal acuerda otorgarle la calificación de:

A quienes se fueron, a quienes lo son todo, a quienes están por llegar.

Resistir sin esperanza es la suprema dignidad del ser humano. José Saramago

## Agradecimientos

A lo largo del complejo camino de maduración personal y profesional que supone la elaboración de una tesis, hay personas que resultan determinantes y sin las cuales el mosaico final que conforma la imagen global del conjunto sería irremediablemente diferente. El reconocimiento y la gratitud que estas líneas pretenden atestiguar sólo suponen una pequeña parte de todo lo que ha significado compartir esta etapa vital con quienes han formado parte de ella.

En primer lugar, a mis directores. Verdaderos guías que me han ido mostrando el camino e inestimables compañeros de viaje a lo largo de él. Francisco Gámiz, referente permanente y espejo en el que encontrar siempre el reflejo de una concepción de la ciencia basada en el trabajo duro y bien hecho. Por mostrarme que la perseverancia fruto de la convicción en lo que hacemos acaba siendo reconocida y valorada. Siempre me sentí respaldado por ti y apoyado especialmente en los momentos menos gratos. Gracias por confiar en mí. Andrés Godoy, un ejemplo constante del gusto por la perfección. Siempre enseñándome y planteándome la pregunta adecuada en el momento justo. Haciéndome dudar, y haciéndome sentir que siempre era posible mejorar. Contigo compartí —y espero seguir haciéndolo— el gusto por correr. Nunca conseguí ganarte, pero incluso en eso, me sirves permanentemente de modelo.

A Isabel Tienda, porque nunca olvidaré a través de quién tuve la oportunidad de conocer y vincularme al grupo de nanoelectrónica. Estuviste en el origen de esta travesía que ahora llega a puerto, y por ello mi gratitud va mucho más allá de lo que pueden expresar estas palabras. Has conocido la historia desde sus orígenes y comprenderás el lugar destacado que para mi ocupas formando parte de todo esto.

A Pablo Sánchez, compañero, amigo y partícipe de innumerables correrías académicas, personales... e incluso cinematográficas. Permanentemente con una perspectiva sincera, y con una palabra de ánimo lista en la recámara. Me siento afortunado de tenerte cerca y agradecido por dejarme compartir tu visión de la vida.

A Elena Ocaña. Por tantísimos momentos, por tantísimo cariño, por tu amistad inquebrantable. Porque estuvieras donde estuvieras, por lejos que fuera, siempre te he sentido a mi lado. Hemos reído juntos, llorado juntos, y compartido infinidad de cosas con las que atesoro en mí una pequeña parte de tu humanidad.

A Rosalía, por tu contrapunto de entrañable excentricidad con la que siempre supiste poner buena cara a la adversidad. Tu enorme capacidad y afán de superación te harán salir adelante frente a cualquier obstáculo. Fue un honor compartir contigo el inicio del camino. A Consuelo, por tus ideas e integridad. A Dani Guirado, por demostrar que el listón de la locura siempre se puede poner un poco más allá. A Dani Partal, Isa y Juanito, la entrañable familia que se encarga de poner el toque de cordura en los viajes.

A Antonio Palomares, por tu ejemplo de integridad y dedicación docente, por tu visión pragmática a la hora de enfrentar cualquier problema, por saber escuchar, por indignarte conmigo, por echar una mano siempre que hiciera falta, por las infinitas cenas viendo House... y por mil y un motivos que nunca terminaría de enumerar.

A Jorge de Blas, por la camaradería que compartimos y por tu enorme bondad. Llegarás muy lejos porque cuando la luz brilla en la oscuridad, la oscuridad desaparece. A Mari Carmen Carmona, por tu ejemplo de trabajo metódico y porque no soy capaz de recordar una sola vez en que no sonrieras, pasara lo que pasara.

A Pedro y Laura, por vuestra hospitalidad, espontaneidad, y por dejar siempre para otro día el visitar la catedral de Málaga. A Laura y Pablo, que desde la distancia también forman parte del grupo que aunque en otra rama de la ciencia— compartió la aventura de embarcarse en una tesis. A Ian, por ser el contrapunto matemático en medio de tanto biólogo y por hacerme sentir en casa cada vez que estoy en Málaga. A Vero, porque sabes todo lo que me has dado y porque haces que intente estar a tu altura siquiera para expresarte la enorme gratitud que supone encontrar a alguien tan especial como tú. Confío en que seamos compañeros atravesando la ignota senda que se abre ante nosotros tras la tesis.

A Enrique, compañero de despacho en espíritu desde tu destierro en el otro pasillo. A Abraham, defenderemos nuestras tesis con un pequeño intervalo entre ambas y, por eso mismo, me he sentido reflejado en ti y animado por tu ejemplo todo este tiempo compartido. A Pilar, por no rendirte y por tu enorme capacidad de trabajo. A Karam, por el contrapeso cultural que das al despacho. A Trinidad, porque los puntos de vista diferentes enriquecen y porque los nuestros no han impedido que fragüemos una sólida y sincera amistad. A Celso, prohombre bastetano, por esa especial conexión que da compartir un sentido del humor como el nuestro, que hace memorables las incontables horas juntos. Siempre decías que habías llegado al grupo de casualidad, ojalá las casualidades trajeran siempre a gente como tú. Y a Nika, sencillamente por aparecer... por haber llegado a formar parte tan importante de todo. Por nuestra especialísima complicidad, por tu franqueza, por tu confianza, por hacerme reír con la tontería más impensable, por sentirte al lado en cualquier situación y por compartir los mejores y los peores momentos.

A Fran y Luca, fuisteis mis primeros compañeros de despacho cuando empecé y difícilmente se puede tener más suerte por ello. A Carlos, por estar ahí siempre que necesité tu ayuda o pedirte cualquier cosa. A Noel, por ser y dar un gran ejemplo a quienes te rodean. Y a todos los miembros del Departamento de Electrónica con los que, de una manera u otra, he compartido parte de estos años.

Finalmente, a mis hermanos y mis padres. Es para vosotros la más emocionada expresión de mi gratitud, admiración y sentimientos, que siento no ser capaz de expresar con palabras. Siempre resultarían insuficientes y nunca contendrían todo lo que querría poner en ellas. Os reservo el espacio íntimo donde las emociones se comparten y donde todo se sabe sin ser dicho. Lo sois todo y lo seguiréis siendo cuando ya nada sea.

### Abstract

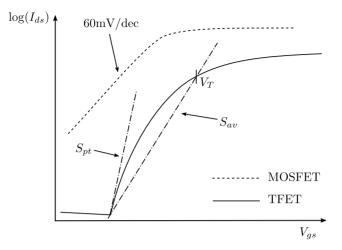

The aim of the work herein presented in this thesis is to deepen the simulation study of devices based of new injection mechanisms, which are currently regarded as potentially interesting to replace conventional MOSFETs and overcome their fundamental subthreshold swing limitation of 60mV/dec. The physical impossibility of breaking this limit fosters most of the ongoing research precisely in the direction of exploring novel devices such as those considered in this work: the Tunneling Field–Effect Transistors (TFETs) and the Schottky Barrier MOSFETs (SB–MOSFETs). For each one of the considered devices, and assuming the existing State–of–the–Art as starting point, we have structured and organized the performed work according to the following roadmap:

- (i) Exposition of the physical phenomena and mechanisms to be studied for a precise understanding and description of the devices.

- (ii) Identification of the existing limitations, incompatibilities and problems that arise during simulation processes. In our case, using Silvaco ATLAS.

- (iii) Development of simple simulation algorithms that allow to overcome the encountered difficulties and keep using this widely employed commercial simulator.

- (iv) Presentation of simulation results obtained from the application of these proposed simulating approaches.

The scope and orientation of the work in the case of SB–MOSFETs was set by the fact that before performing it, we had experimental results

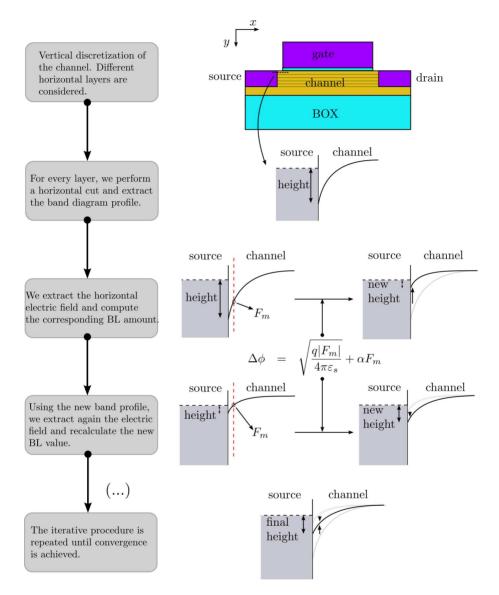

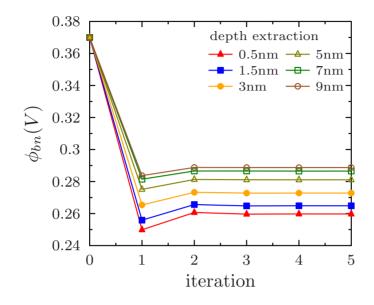

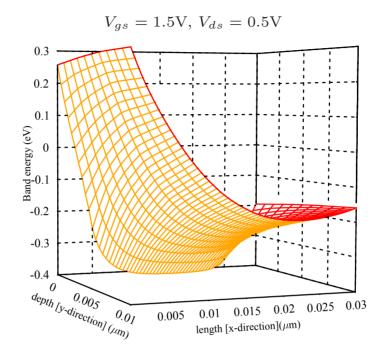

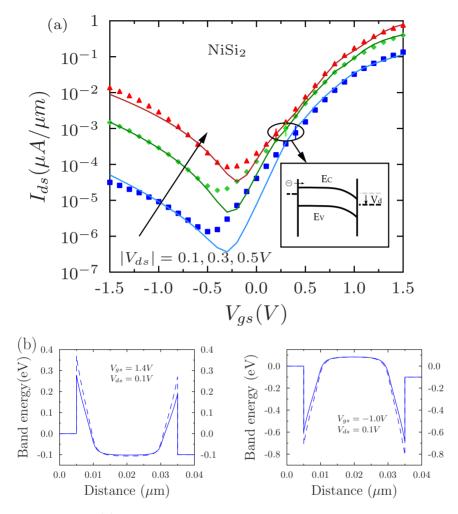

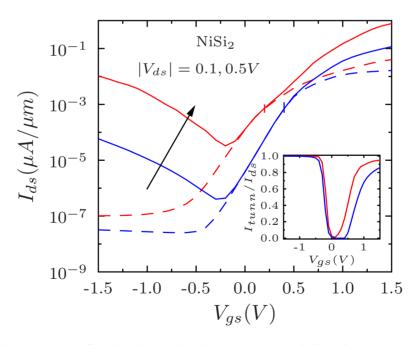

that appropriately aimed our efforts at fitting them. The main problem that we found studying these devices was that barrier lowering processes were not completely implemented in ATLAS when applied to carrier injection mechanisms involving tunneling (field emission and thermionic field emission). Considering the relevant impact that small variations in barrier heights may have on the total current, and taking into account that depending on the bias conditions the relative importance of the different injection mechanisms changes, it becomes essential to suitably include those barrier lowering processes in our simulations. For that purpose, in this work we developed an iterative procedure inside ATLAS to account for barrier lowering (which also applies for tunneling processes), making it vertically dependent on the depth inside the channel. Very accurate fits between experimental results and simulations have been obtained especially for those regions where tunneling processes proved to be dominant. In addition, some short channel effects like the observed current reduction when decreasing the channel length due to the overlap of the potential profiles of the Schottky barriers are also satisfactorily reproduced.

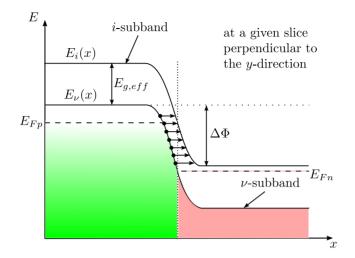

In the case of TFETs, as most of the existing research on them still involves semiclassical approaches and considering their progressive reduction in size, we wanted to take a step forward by somehow performing a more complete treatment which needed to include the effect of quantum confinement. The necessity of such an approach was obvious regarding that whenever the presence of confinement is significant, the existence of a discrete sprectum of energy levels replacing the formerly continuous conduction and valence bands should be greatly affecting the so-called band-to-band tunneling injection of carriers. In that context, the work developed in this thesis lies between those semiclassical models not accounting for the effects of confinement, and the more recent approaches involving rigorous quantum mechanical treatments. The inclusion of confinement made us realize that the numerical solvers employed by ATLAS when using the non-local band-to-band tunneling model (to inject carriers), and the self consistent Schrödinger–Poisson model (to account for subband quantization) were not compatible. At that stage, we decided to exploit the capabilities of the simulator by designing an iterative approach that reasonably allowed to account for confinement in a way that offers great possibilities for researchers that may be potentially interested in the study of these devices. Thanks to the development of this approach we have been able to analyze the impact that confinement indeed has over the underlying physics in TFETs, and how it modifies their total current levels or affects the global trends of electrical parameters of utmost importance for their characterization (threshold voltages and subthreshold swings).

## Contents

| Ι        | $\mathbf{E}\mathbf{x}$ | tendeo  | l Abstract in Spanish                                 | xxvii  |

|----------|------------------------|---------|-------------------------------------------------------|--------|

|          | I.1                    | Introd  | lucción                                               | xxix   |

|          | I.2                    | Plante  | eamiento general                                      | xxxi   |

|          | I.3                    | Schott  | ky barrier MOSFETs                                    | xxxiii |

|          |                        | I.3.1   | Principales ventajas y limitaciones                   | xxxiii |

|          |                        | I.3.2   | Procesos de transporte e inyección de portadore       | 5      |

|          |                        |         | a través de barreras Schottky                         | XXXV   |

|          |                        | I.3.3   | Regímenes de operación de los SB–MOSFETs .            | xxxvii |

|          |                        | I.3.4   | Mecanismos de bajada de barrera                       | xxxix  |

|          |                        | I.3.5   | Estructura de dispositivo y datos experimentales      | . xli  |

|          |                        | I.3.6   | Resultados de las simulaciones $\ldots \ldots \ldots$ | xliii  |

|          | I.4                    | Tunne   | el FETs                                               | xlvi   |

|          |                        | I.4.1   | Regímenes de operación de los TFETs $\ . \ . \ .$     | xlvii  |

|          |                        | I.4.2   | Principios de funcionamiento                          | xlix   |

|          |                        | I.4.3   | Inclusión del confinamiento cuántico $\ . \ . \ .$    | lii    |

|          |                        | I.4.4   | Estructura de dispositivo                             | liv    |

|          |                        | I.4.5   | Resultados de las simulaciones                        | liv    |

|          |                        |         |                                                       |        |

| Π        | Μ                      | ain D   | ocument                                               | lxiii  |

| 1        | Intr                   | roducti | ion                                                   | 1      |

| <b>2</b> | $\mathbf{Sch}$         | ottky [ | Barrier MOSFETs (SB–MOSFETs)                          | 7      |

|          | 2.1                    | Main    | benefits                                              | 7      |

|          | 2.2                    | Limita  | ations and improvements                               | 9      |

|   | 2.3 | Histor | ical overview                                                           | 10 |

|---|-----|--------|-------------------------------------------------------------------------|----|

|   | 2.4 | Metal- | -semiconductor junction                                                 | 11 |

|   |     | 2.4.1  | Formation of the Schottky Barrier                                       | 11 |

|   |     | 2.4.2  | Carrier transport                                                       | 19 |

|   | 2.5 | The M  | IOS capacitor                                                           | 26 |

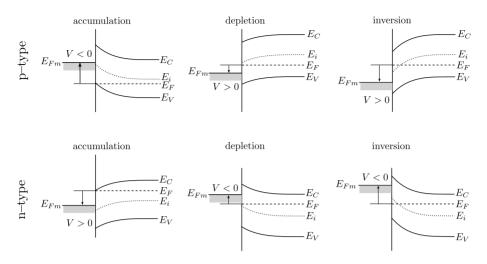

|   | 2.6 | SB-M   | OSFETs operating regimes                                                | 29 |

|   | 2.7 | Bulk a | and SOI SB–MOSFETs                                                      | 31 |

| 3 | Imp | lemen  | tation of Barrier Lowering in SB–MOSFETs                                | 35 |

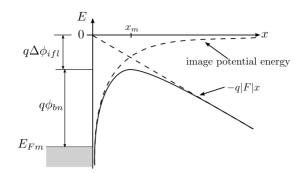

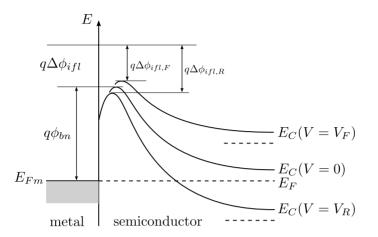

|   | 3.1 | Image  | force lowering                                                          | 36 |

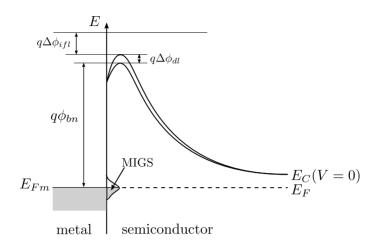

|   | 3.2 | Dipole | e lowering                                                              | 38 |

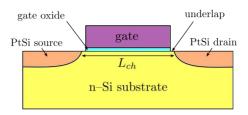

|   | 3.3 | Device | estructure                                                              | 40 |

|   | 3.4 | Experi | imental data                                                            | 42 |

|   | 3.5 | Simula | ation scheme and methodology $\ldots \ldots \ldots \ldots \ldots$       | 45 |

|   |     | 3.5.1  | Existing framework and limitations                                      | 45 |

|   |     | 3.5.2  | Proposed simulation approach $\ldots \ldots \ldots \ldots$              | 46 |

|   | 3.6 | Simula | ation results and experimental data $\ldots$ $\ldots$ $\ldots$          | 49 |

|   |     | 3.6.1  | Transfer characteristics for $L_g = 20$ nm                              | 49 |

|   |     | 3.6.2  | Short channel effects (SCE)                                             | 56 |

|   |     | 3.6.3  | Underlap variation                                                      | 59 |

| 4 | Tun | neling | Field Effect Transistors (TFETs)                                        | 61 |

|   | 4.1 | Origin | s and history                                                           | 62 |

|   | 4.2 | Struct | ure and operation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 63 |

|   |     | 4.2.1  | Tunnel diodes                                                           | 64 |

|   |     | 4.2.2  | Operating regimes of the TFET                                           | 66 |

|   | 4.3 | Worki  | ng principles                                                           | 69 |

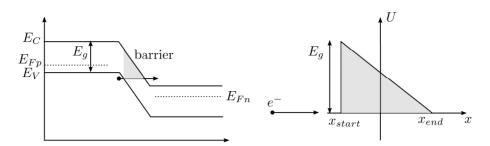

|   |     | 4.3.1  | Band–to–band tunneling current                                          | 69 |

|   |     | 4.3.2  | Modeling the transmission probability $\ . \ . \ . \ .$                 | 71 |

|   |     | 4.3.3  | Direct and indirect tunneling $\ldots \ldots \ldots \ldots$             | 75 |

|   |     | 4.3.4  | Inversion layer formation in TFETs                                      | 76 |

|   |     | 4.3.5  | Subthreshold swing in TFETs                                             | 78 |

| <b>5</b> | Sen | niclassi | cal and quantum simulations in TFETs                               | 81        |

|----------|-----|----------|--------------------------------------------------------------------|-----------|

|          | 5.1 | Band-    | to-band tunneling models                                           | 82        |

|          |     | 5.1.1    | Local BTBT models                                                  | 82        |

|          |     | 5.1.2    | Non–local BTBT model                                               | 86        |

|          | 5.2 | Quant    | um effects modeling                                                | 90        |

|          |     | 5.2.1    | Density Gradient model $\ldots \ldots \ldots \ldots \ldots \ldots$ | 90        |

|          |     | 5.2.2    | Self–Consistent Coupled Schrödinger–Poisson model                  | 91        |

|          | 5.3 | Limita   | ations, incompatibilities and solutions                            | 93        |

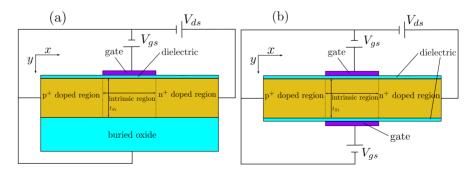

|          | 5.4 | Device   | e structure and operation                                          | 95        |

|          | 5.5 | Simula   | ation results                                                      | 96        |

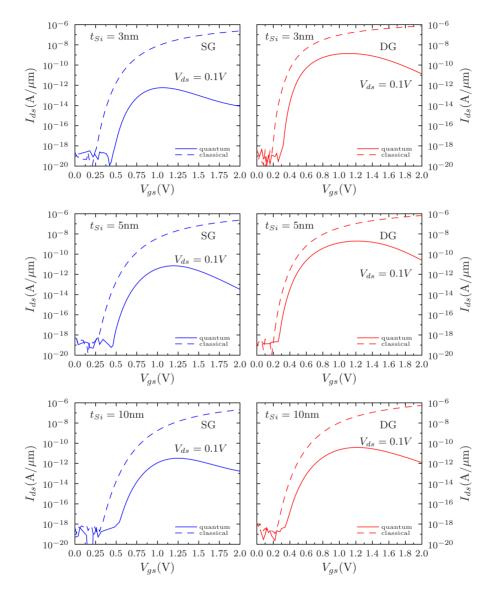

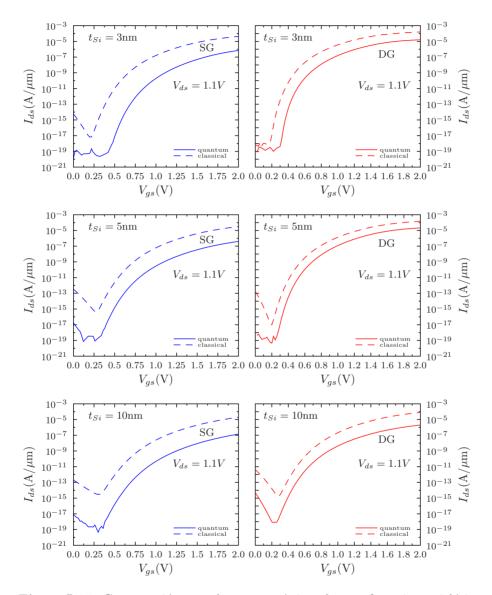

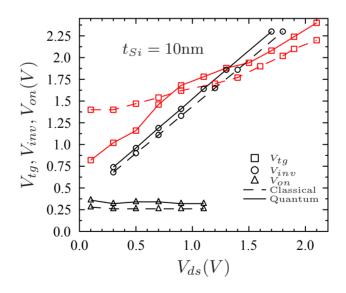

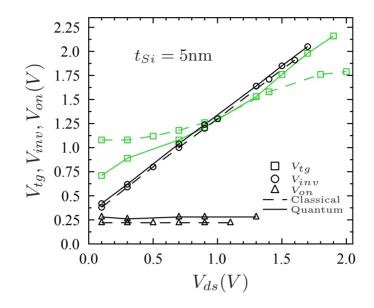

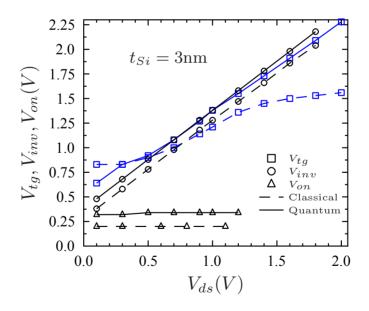

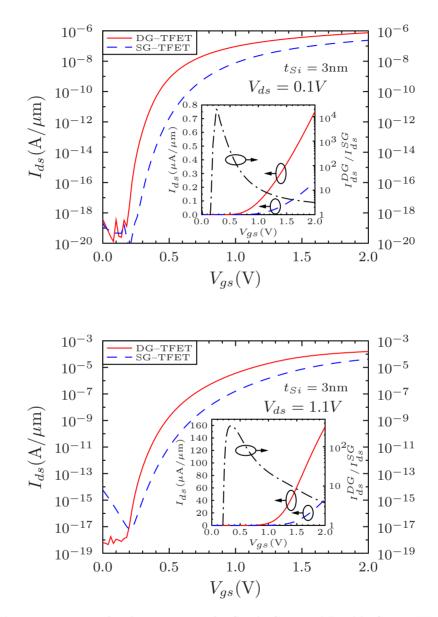

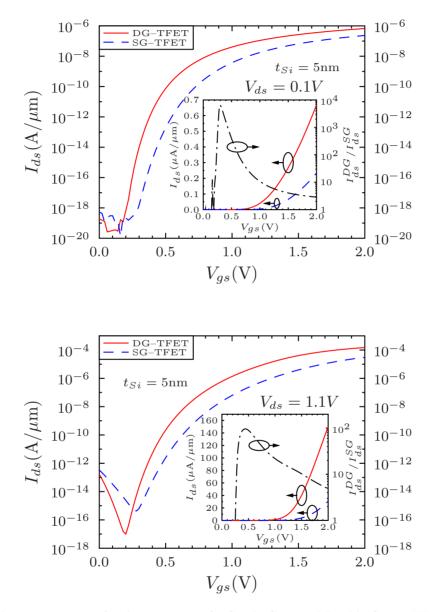

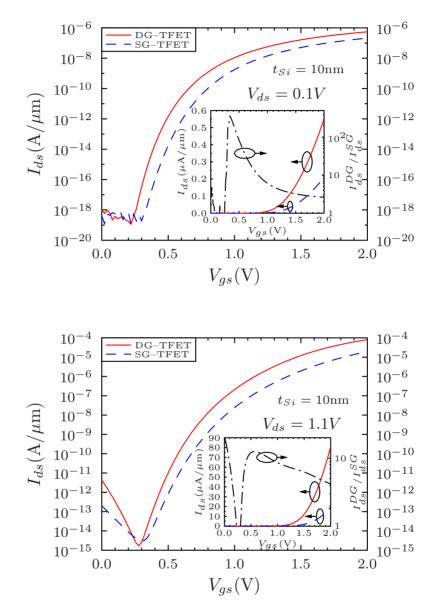

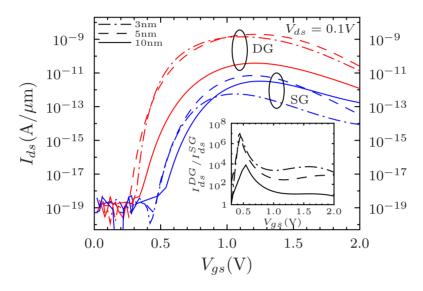

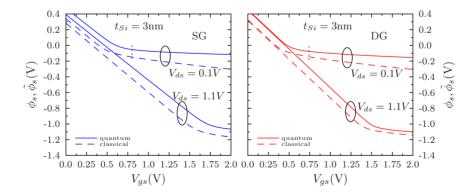

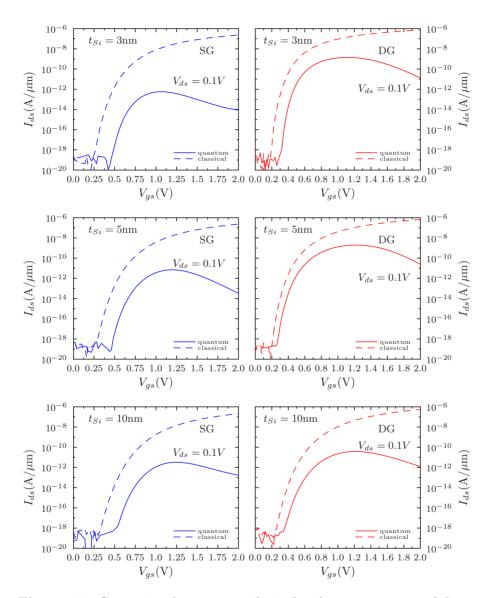

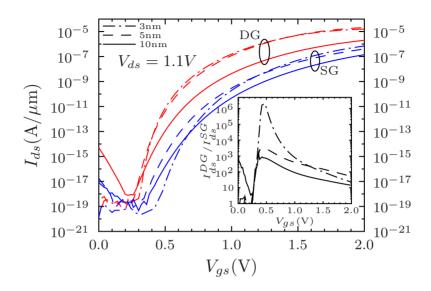

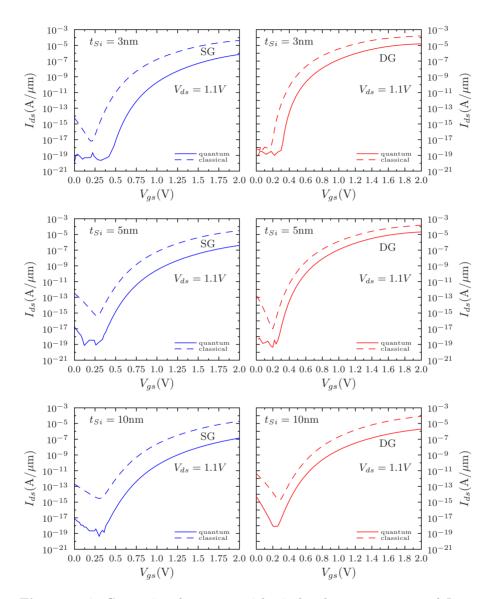

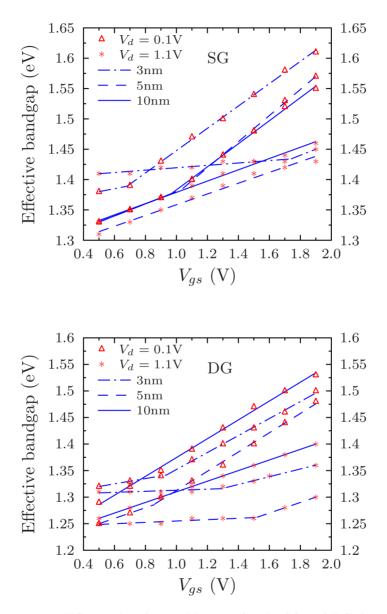

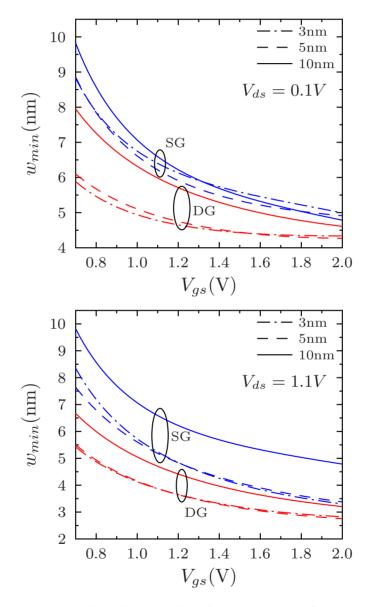

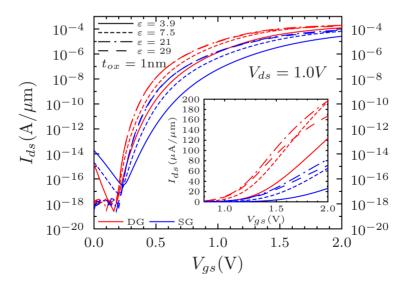

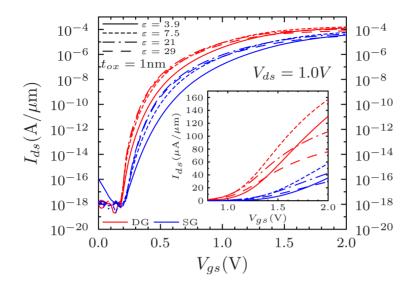

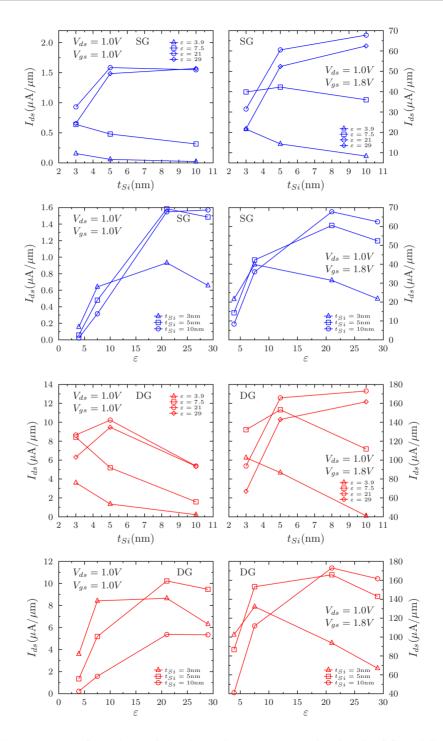

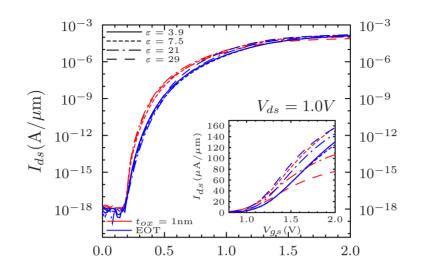

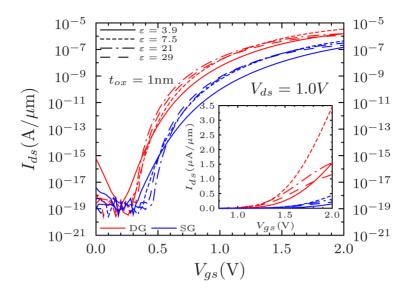

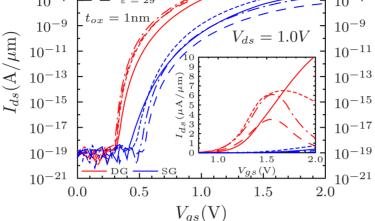

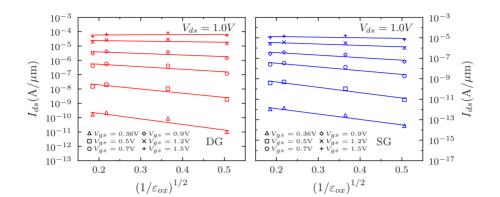

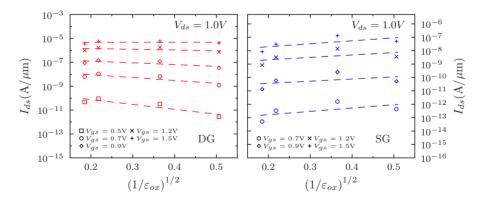

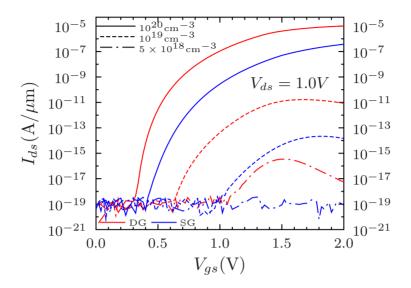

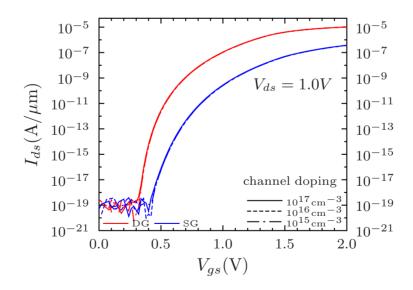

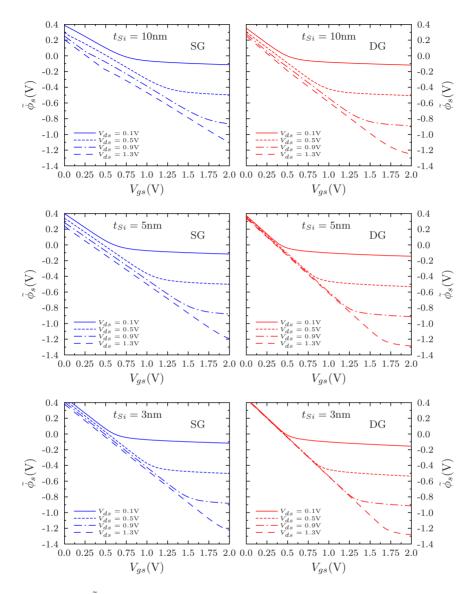

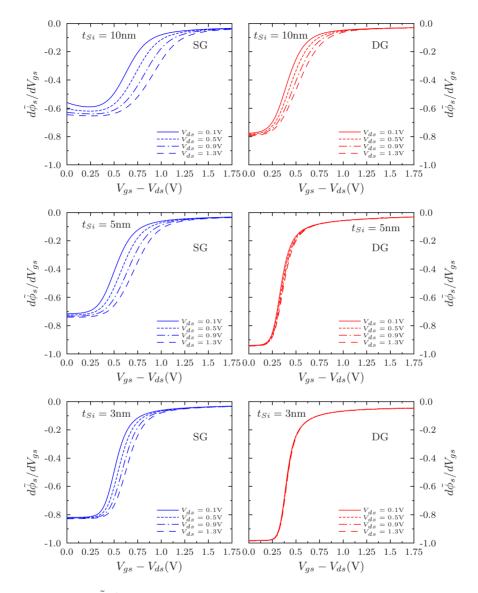

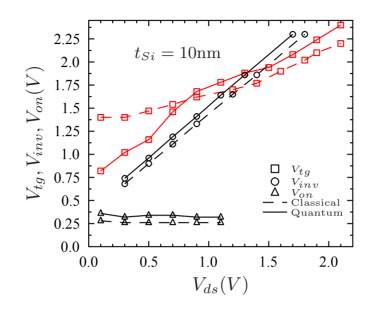

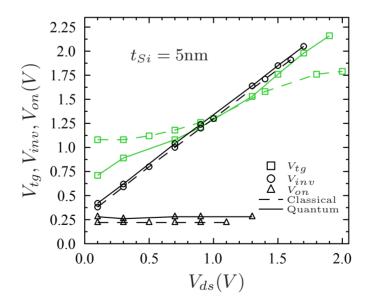

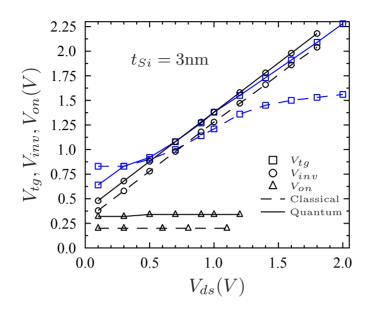

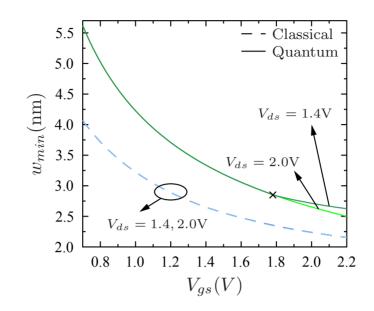

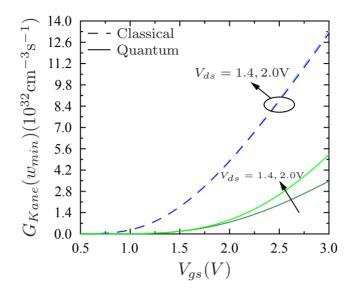

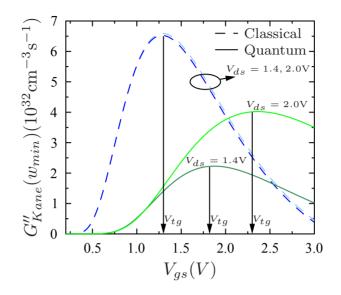

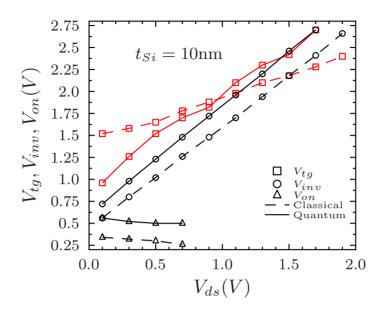

|          |     | 5.5.1    | Effect of body thickness variation                                 | 96        |

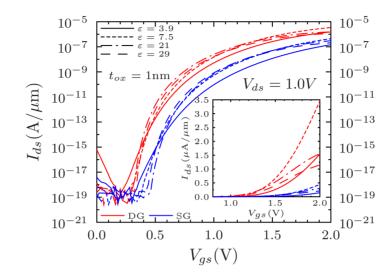

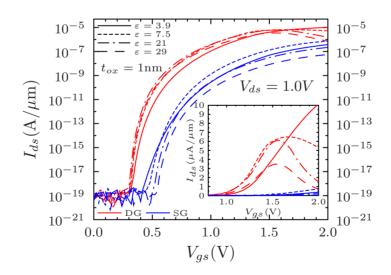

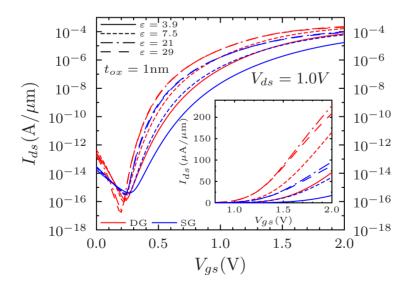

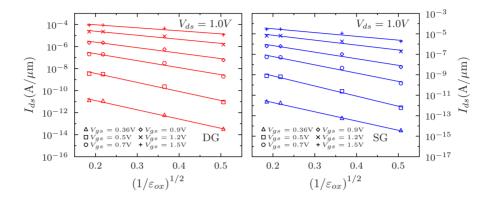

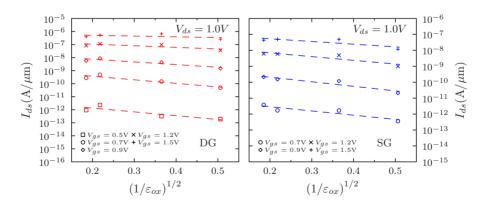

|          |     | 5.5.2    | Effect of high– $\kappa$ dielectric                                | 108       |

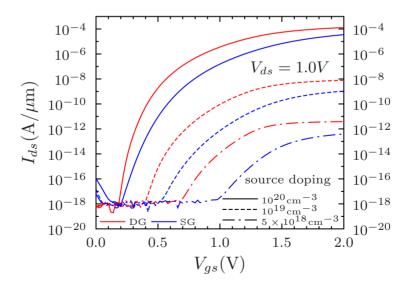

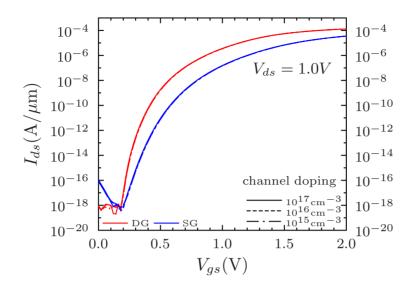

|          |     | 5.5.3    | Effect of doping variation                                         | 117       |

| 6        | Qua | antum    | effects on threshold voltages and SS in TFETs1                     | <b>21</b> |

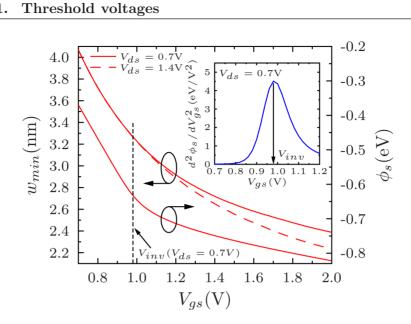

|          | 6.1 | Thres    | hold voltages                                                      | 121       |

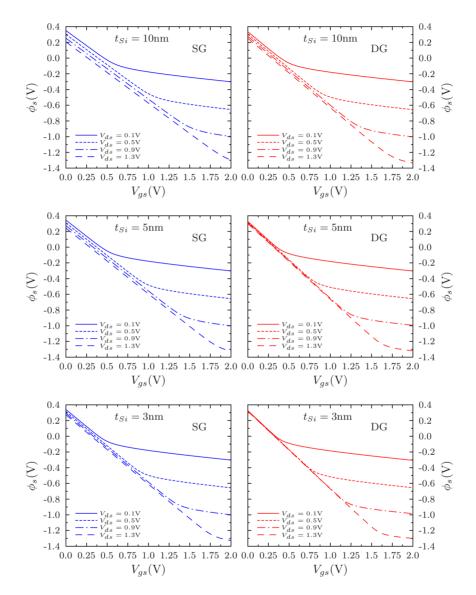

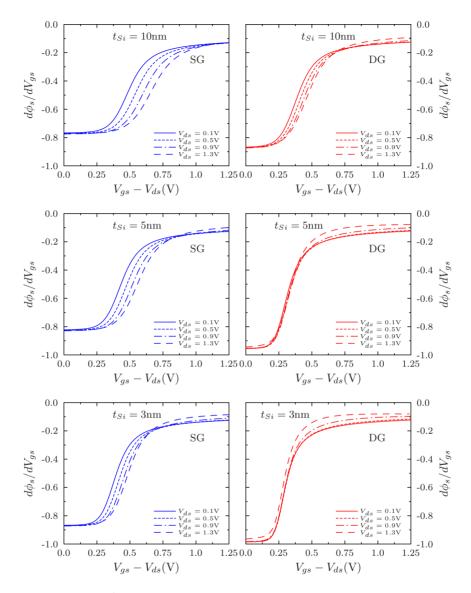

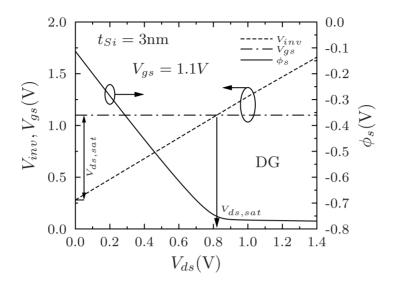

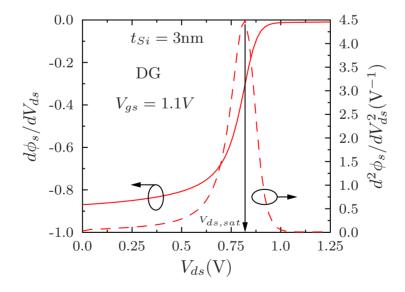

|          |     | 6.1.1    | The role of the inversion layer                                    | 122       |

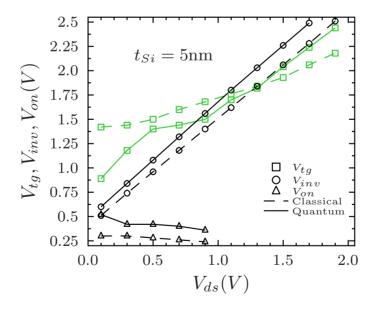

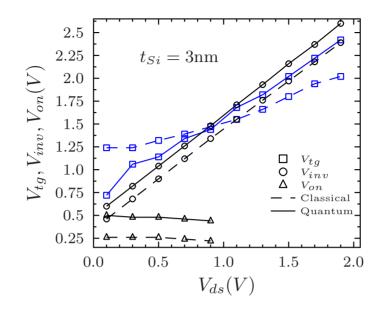

|          |     | 6.1.2    | Gate threshold voltage, $V_{tg}$                                   | 130       |

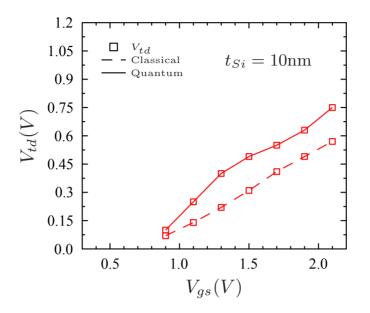

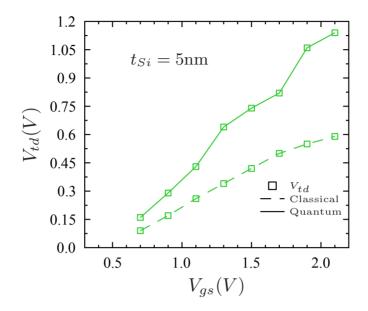

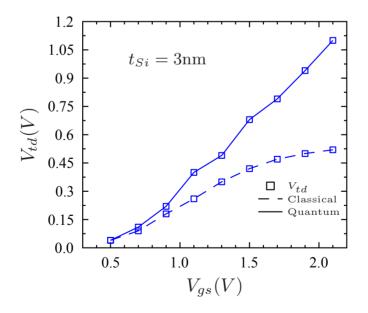

|          |     | 6.1.3    | Drain threshold voltage, $V_{td}$                                  | 139       |

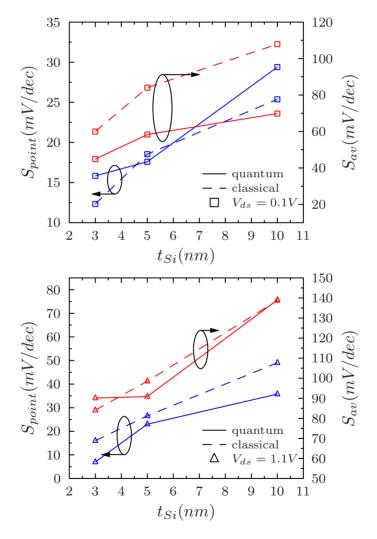

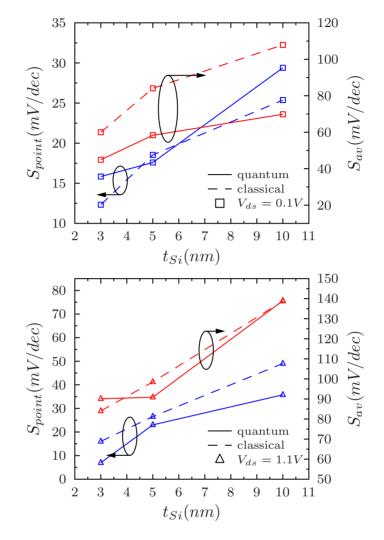

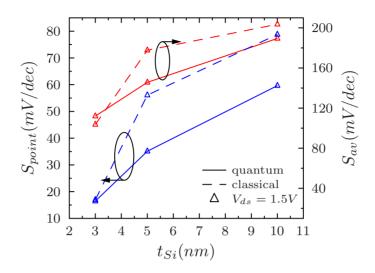

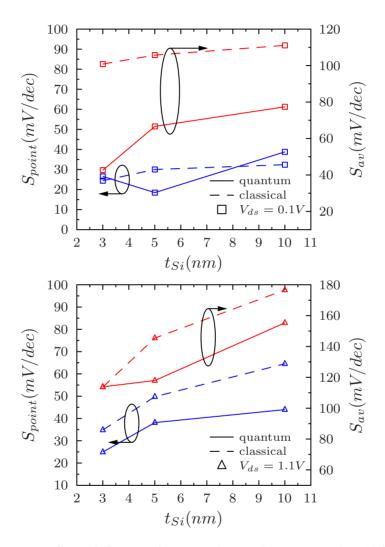

|          | 6.2 | Subth    | reshold Swings (SS)                                                | 142       |

|          |     | 6.2.1    | DG-TFET                                                            | 142       |

|          |     | 6.2.2    | SG-TFET                                                            | 144       |

| 7        | Con | clusio   | ns, future work and publications                                   | 47        |

|          | 7.1 | Conclu   | usions                                                             | 147       |

|          |     | 7.1.1    | Schottky Barrier MOSFETs                                           | 147       |

|          |     | 7.1.2    | Tunneling Field–Effect Transistors                                 | 148       |

|          | 7.2 | Future   | e work                                                             | 150       |

|          | 7.3 |          | eations                                                            |           |

|          |     | 7.3.1    | Journals                                                           | 151       |

|          |     | 7.3.2    | International Conferences                                          | 151       |

| A        | ATI | LAS si   | mulator 1                                                          | 153       |

|          | A.1 | Descri   | ption                                                              | 153       |

|          | A.2 | Simula   | ation process structure                                            | 154       |

| A.3 ATLAS input files      | 155 |

|----------------------------|-----|

| III Conclusions in Spanish | 157 |

| Bibliography               | 163 |

# List of Abbreviations and Symbols

### Abbreviations

| ATM       | Airy-transfer-matrix                              |

|-----------|---------------------------------------------------|

| BL        | Barrier lowering                                  |

| BOX       | Buried oxide (isolation layer of a SOI structure) |

| BTBT      | Band–to–band tunneling                            |

| CMOS      | Complementary MOS technology                      |

| CNT       | Carbon nanotube                                   |

| DG        | Double gate                                       |

| DIBL      | Drain induced barrier lowering                    |

| DL        | Dipole lowering                                   |

| FET       | Field–effect transistor                           |

| GIDL      | Gate induced drain leakage                        |

| IFL       | Image force lowering                              |

| MIGS      | Metal induced gap states                          |

| MOS       | Metal-oxide-semiconductor                         |

| MOSFET    | Metal–oxide–semiconductor field–effect transistor |

| PMOS      | p–channel MOSFET                                  |

| RTA       | Rapid Thermal Annealing                           |

| SB        | Schottky barrier                                  |

| SBH       | Schottky barrier height                           |

| SB-MOSFET | Schottky barrier MOSFET                           |

| SB-NMOS   | n–channel SB–MOSFET                               |

| SCE           | Short Channel Effects                            |

|---------------|--------------------------------------------------|

| SDE           | Source/drain extension                           |

| SEM           | Scanning electron microscopy                     |

| SG            | Single gate                                      |

| S/D           | Source/drain                                     |

| SOI           | Silicon on insulator                             |

| $\mathbf{SS}$ | Subthreshold swing                               |

| TCAD          | Technology computer aided design                 |

| TFET          | Tunneling field–effect transistor                |

| UST           | Universal Schottky tunneling                     |

| UTB           | Ultra–thin body                                  |

| WKB           | Wenzel–Kramers–Brillouin approximation           |

| XTEM          | Cross–sectional transmission electron microscopy |

|               |                                                  |

### Symbols

| $C_{ox}$ Oxide capacitance $C_q$ Quantum capacitance (semiconductor capacitance) $dn$ Electron density in an incremental energy range $\delta$ Interfacial layer length $\Delta$ Potential drop across the interfacial layer $\Delta\phi$ Barrier lowering potential $\Delta\phi_{dl}$ DL Barrier lowering potential $\Delta\phi_{dl}$ Interface trap density $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_F$ Fermi level energy $E_F$ Fermi level energy $E_F$ Fermi level energy $E_F$ Semini level energy $E_F$ Phonon energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_f$ Semiconduction band energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_r$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_V$ Valence band energy $E_v$ Semiconductor permittivity $\epsilon_s$ Semiconductor permittivity $\epsilon_s$ Semiconductor permittivity $\epsilon_i$ Interfacial layer permittivity $\epsilon_i$ Interfacial layer permittivity $\epsilon_i$ Interfacial layer permittivity $\epsilon_i$ Interfacial layer permittivity $\epsilon_i$ Interfacial laye | $A^*$               | Richardson's constant                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------|

| $d_n$ Electron density in an incremental energy range $\delta$ Interfacial layer length $\Delta$ Potential drop across the interfacial layer $\Delta \phi$ Barrier lowering potential $\Delta \phi_{dl}$ DL Barrier lowering potential $\Delta \phi_{ifl}$ IFL Barrier lowering potential $\Delta \Phi$ Available energy range for BTBT $D_{it}$ Interface trap density $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_{i}$ Intrinsic Fermi level energy $E_F$ Fermi level energy $E_F$ Fermi level energy $E_F_m$ Fermi level energy $E_{Fm}$ Fermi level energy $E_p$ Onduction band bound energy $E_q$ Bandgap energy $E_p$ Phonon energy $E_p$ Phonon energy $E_p$ Valence band bound energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_{Vn(p)}$ n(p)-side valence band energy $E_o$ Vacuum permittivity $E_a$ Semiconductor permittivity $E_s$ Semiconductor permittivity                                                                                                                                                  | $C_{ox}$            | Oxide capacitance                                       |

| $\delta$ Interfacial layer length $\Delta$ Potential drop across the interfacial layer $\Delta \phi$ Barrier lowering potential $\Delta \phi_{dl}$ DL Barrier lowering potential $\Delta \phi_{ifl}$ IFL Barrier lowering potential $\Delta \Phi$ Available energy range for BTBT $D_{it}$ Interface trap density $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_{i}$ Intrinsic Fermi level energy $E_F$ Fermi level energy $E_Fm$ Fermi level energy $E_Fm$ Fermi level energy $E_F$ Reduced energy $E_p$ Nonon energy $E_q$ Bandgap energy $E_p$ Phonon energy $E_p$ Valence band bound energy $E_V$ Valence band bound energy $E_p$ Phonon energy $E_q$ Sendical energy $E_r$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band edge energy $E_0$ Vacuum permittivity $\epsilon_{ax}$ Oxide permittivity $\epsilon_{ax}$ Semiconductor permittivity                                                                                                                                                                                                                                                                                                         | $C_q$               | Quantum capacitance (semiconductor capacitance)         |

| $\Delta$ Potential drop across the interfacial layer $\Delta\phi$ Barrier lowering potential $\Delta\phi_{dl}$ DL Barrier lowering potential $\Delta\phi_{ifl}$ IFL Barrier lowering potential $\Delta\Phi$ Available energy range for BTBT $D_{it}$ Interface trap density $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_{rn(p)}$ n(p)-side conduction band energy $E_i$ Intrinsic Fermi level energy $E_Fm$ Fermi level energy $E_Fm$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_p$ Bandgap energy $E_p$ Phonon energy $E_p$ Reduced energy $E_p$ Valence band bound energy $E_T$ Transverse energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_r$ Graitudinal energy $E_r$ Semiconductor permittivity $\epsilon_ax$ Oxide permittivity $\epsilon_s$ Semiconductor permittivity                                                                                                                                                                                                                                                                                                                            | dn                  | Electron density in an incremental energy range         |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | δ                   | Interfacial layer length                                |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\Delta$            | Potential drop across the interfacial layer             |

| $\Delta \phi_{ifl}$ IFL Barrier lowering potential $\Delta \Phi$ Available energy range for BTBT $D_{it}$ Interface trap density $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_{Cn(p)}$ n(p)-side conduction band energy $E_i$ Intrinsic Fermi level energy $E_F$ Fermi level energy $E_Fm$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_{\mu}$ Valence band bound energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_T$ Transverse energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_{\eta}$ Longitudinal energy $E_{\eta}$ Ongitudinal energy $E_{\eta}$ Valence band edge energy $E_{\eta}$ Oxide permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_s$ Semiconductor permittivity                                                                                                                                                                                                                                                                                                                                                                                           | $\Delta \phi$       | Barrier lowering potential                              |

| $\Delta \Phi$ Available energy range for BTBT $D_{it}$ Interface trap density $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_C$ Conduction band energy $E_{Cn(p)}$ n(p)-side conduction band energy $E_r$ Fermi level energy $E_F$ Fermi level energy $E_Fm$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_{\mu}$ Valence band bound energy $E_g$ Bandgap energy $E_q$ Reduced energy $E_p$ Valence band bound energy $E_p$ Valence band bound energy $E_q$ Reduced energy $E_{\mu}$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_v(p)$ n(p)-side valence band energy $E_v(p)$ n(p)-side valence band energy $E_v(p)$ N(p)-side valence band energy $\varepsilon_{\alphax}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_s$ Semiconductor permittivity                                                                                                                                                                                                                                                                                                                                    | $\Delta \phi_{dl}$  | DL Barrier lowering potential                           |

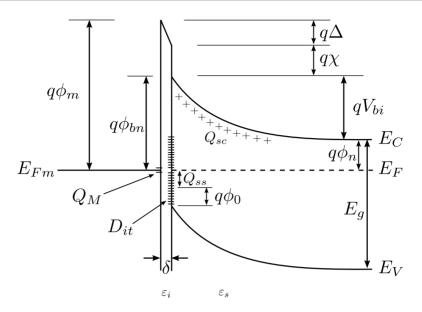

| $D_{it}$ Interface trap density $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_C$ Conduction band edge energy $E_{Cn(p)}$ $n(p)$ -side conduction band energy $E_i$ Intrinsic Fermi level energy $E_F$ Fermi level energy $E_Fm$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_Fm$ Fermi level energy $E_Fm$ Fermi level energy $E_{p}$ Phonon energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_00$ Reduced energy $E_T$ Transverse energy $E_T$ Valence band edge energy $E_V$ Valence band energy $E_V$ Valence band energy $E_r$ Genicular energy $E_r$ Semiconductor permittivity $\epsilon_{ox}$ Oxide permittivity $\epsilon_s$ Semiconductor permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\Delta \phi_{ifl}$ | IFL Barrier lowering potential                          |

| $E_m$ Energy level above $E_F$ at which thermionic emission<br>is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_C$ Conduction band energy $E_{Cn(p)}$ n(p)-side conduction band energy $E_i$ Intrinsic Fermi level energy $E_F$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_Fm$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_p$ Phonon energy $E_g$ Bandgap energy $E_00$ Reduced energy $E_00$ Reduced energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_0$ Vacuum permittivity $\epsilon_{ox}$ Oxide permittivity $\epsilon_{ox}$ Semiconductor permittivity $\epsilon_s$ Semiconductor permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\Delta \Phi$       | Available energy range for BTBT                         |

| is maximum $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_C$ Conduction band edge energy $E_{Cn(p)}$ $n(p)$ -side conduction band energy $E_i$ Intrinsic Fermi level energy $E_F$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_Fm$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_p$ Valence band bound energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_0$ Reduced energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_r$ Oxide permittivity $\epsilon_{ox}$ Oxide permittivity $\epsilon_s$ Semiconductor permittivity $\epsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $D_{it}$            | Interface trap density                                  |

| $D_n$ Diffusion coefficient $E_C$ Conduction band edge energy $E_C$ Conduction band energy $E_{Cn(p)}$ n(p)-side conduction band energy $E_i$ Intrinsic Fermi level energy $E_F$ Fermi level energy $E_{Fm}$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_{\mu}$ Valence band bound energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_0$ Reduced energy $E_T$ Transverse energy $E_T$ Valence band edge energy $E_V$ Valence band energy $E_V$ Valence band energy $E_{T}$ Origitudinal energy $E_T$ Ongitudinal energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_V$ Oxide permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_{ox}$ Semiconductor permittivity $\varepsilon_s$ Semiconductor permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $E_m$               | Energy level above $E_F$ at which thermionic emission   |

| $E_C$ Conduction band edge energy $E_Cn(p)$ $n(p)$ -side conduction band energy $E_i$ $n(r)$ -side conduction band energy $E_i$ $Intrinsic Fermi level energyE_FmFermi level energy in the metalE_iConduction band bound energyE_\muValence band bound energyE_gBandgap energyE_pPhonon energyE_{p}Phonon energyE_{00}Reduced energyE_TTransverse energyE_VValence band edge energyE_VValence band edge energyE_{T}Transverse energyE_VValence band edge energyE_VValence band edge energyE_VValence band edge energyE_VValence band edge energyE_{Vn(p)}n(p)-side valence band energy\varepsilon_{ox}Oxide permittivity\varepsilon_{ox}Semiconductor permittivity\varepsilon_sSemiconductor permittivity$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     | is maximum                                              |

| $E_{Cn(p)}$ n(p)-side conduction band energy $E_i$ Intrinsic Fermi level energy $E_F$ Fermi level energy $E_{Fm}$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_{\mu}$ Valence band bound energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_{00}$ Reduced energy $E_{m}$ Iongitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_V$ Oxide permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_{s}$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $D_n$               | Diffusion coefficient                                   |

| $E_i$ Intrinsic Fermi level energy $E_F$ Fermi level energy $E_F$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_i$ Valence band bound energy $E_{\nu}$ Valence band bound energy $E_g$ Bandgap energy $E_g$ Phonon energy $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{1 }$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $\epsilon_0$ Nacuum permittivity $\epsilon_{ox}$ Oxide permittivity $\epsilon_s$ Semiconductor permittivity $\epsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $E_C$               | Conduction band edge energy                             |

| $E_F$ Fermi level energy $E_{Fm}$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_i$ Conduction band bound energy $E_{\nu}$ Valence band bound energy $E_g$ Bandgap energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_{00}$ Reduced energy $E_{1 }$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_{ox}$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $E_{Cn(p)}$         | n(p)–side conduction band energy                        |

| $E_{Fm}$ Fermi level energy in the metal $E_i$ Conduction band bound energy $E_{i}$ Valence band bound energy $E_{g}$ Bandgap energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{1 }$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_{vn(p)}$ n(p)-side valence band energy $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_{ox}$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $E_i$               | Intrinsic Fermi level energy                            |

| $E_i$ Conduction band bound energy $E_i$ Conduction band bound energy $E_{p}$ Valence band bound energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{II}$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_{ox}$ Semiconductor permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $E_F$               | Fermi level energy                                      |

| $E_{\nu}$ Valence band bound energy $E_g$ Bandgap energy $E_g$ Bandgap energy $E_p$ Phonon energy $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{\parallel}$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_V$ Valence band energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_{0}$ Oxide permittivity $\varepsilon_{ox}$ Semiconductor permittivity $\varepsilon_s$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $E_{Fm}$            | Fermi level energy in the metal                         |

| $E_g$ Bandgap energy $E_p$ Phonon energy $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{1}$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_{0}$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $E_i$               | Conduction band bound energy                            |

| $E_p$ Phonon energy $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{\parallel}$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_0$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $E_{\nu}$           | Valence band bound energy                               |

| $E_{00}$ Reduced energy $E_{00}$ Reduced energy $E_{\parallel}$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_0$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $E_g$               | Bandgap energy                                          |

| $E_{\parallel}$ Longitudinal energy $E_T$ Transverse energy $E_V$ Valence band edge energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_0$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $E_p$               | Phonon energy                                           |

| $E_T$ Transverse energy $E_V$ Valence band edge energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_0$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $E_{00}$            | Reduced energy                                          |

| $E_V$ Valence band edge energy $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_0$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $E_{\parallel}$     | Longitudinal energy                                     |

| $E_{Vn(p)}$ n(p)-side valence band energy $\varepsilon_0$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $E_T$               | Transverse energy                                       |

| $\varepsilon_0$ Vacuum permittivity $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $E_V$               | Valence band edge energy                                |

| $\varepsilon_{ox}$ Oxide permittivity $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $E_{Vn(p)}$         | n(p)–side valence band energy                           |

| $\varepsilon_s$ Semiconductor permittivity $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\varepsilon_0$     | Vacuum permittivity                                     |

| $\varepsilon_i$ Interfacial layer permittivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\varepsilon_{ox}$  | Oxide permittivity                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\varepsilon_s$     | Semiconductor permittivity                              |

| $f_{s(m)}$ Fermi distribution function in the semiconductor(metal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $f_{s(m)}$          | Fermi distribution function in the semiconductor(metal) |

| F                   | Electric field                                       |

|---------------------|------------------------------------------------------|

| $F_m$               | Electric field maximum                               |

| G                   | Generation rate function per unit volume             |

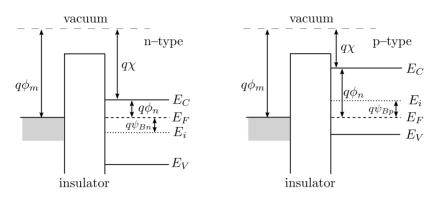

| $\phi_m$            | Metal workfunction                                   |

| $\phi_n$            | Potential difference between $E_C$ and $E_F$         |

| $\phi_p$            | Potential difference between $E_V$ and $E_F$         |

| $\phi_{bn}$         | Schottky barrier for electrons                       |

| $\phi_{bp}$         | Schottky barrier for holes                           |

| $\phi_0$            | Neutral energy level above $E_V$                     |

| $\phi_s$            | Surface channel potential in TFETs                   |

| $	ilde{\phi}_s$     | Quantum surface channel potential in TFETs           |

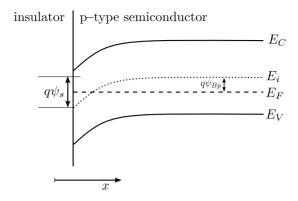

| $\psi_{Bn(p)}$      | Potential difference for n(p)–type semiconductors    |

|                     | inside the bulk between the Fermi level and the      |

|                     | midgap                                               |

| $\psi_{n(p)}(x)$    | Position dependent potential accounting for band     |

|                     | bending inside the semiconductor                     |

| $\psi_s$            | Surface potential in SB–MOSFETs $(\psi_{n(p)}(x=0))$ |

| h                   | Planck constant ( $\hbar$ : Reduced Planck constant) |

| $J_{btbt}$          | BTBT current density                                 |

| $J_{s(m) \to m(s)}$ | Current density from the semiconductor(metal)        |

|                     | into the metal(semiconductor)                        |

| $J_{TE}$            | Thermionic emission saturation current               |

| $J_D$               | Diffusion saturation current                         |

| $J_{n,te}$          | Thermionic emission current density for electrons    |

| $J_{n,tfe}$         | Thermionic field–emission current density for        |

|                     | electrons                                            |

| $J_{n,fe}$          | Field–emission current density for electrons         |

| $J_{n,d}$           | Diffusion current density for electrons              |

| $\kappa$            | Dielectric constant                                  |

| k                   | Boltzmann's constant                                 |

| k(x,y)              | Carrier wave vector                                  |

| $\lambda$           | Screening length                                     |

| $\lambda_H$         | Heine tail length                                    |

| $\Lambda$           | Correction potential in the Density Gradient model   |

| $L_g$        | Gate length                                                |

|--------------|------------------------------------------------------------|

| $m^*$        | Carrier effective mass                                     |

| $\mu_n$      | Electron mobility                                          |

| n            | Electron concentration                                     |

| $n_{ie}$     | Effective intrinsic concentration                          |

| $N_A$        | Acceptor–type doping concentration                         |

| $N_{C(V)}$   | Density of states in the conduction(valence) band          |

| $N_D$        | Donor-type doping concentration                            |

| p            | Hole concentration                                         |

| q            | Carrier charge                                             |

| $Q_M$        | Surface charge on the metal                                |

| $Q_{sc}$     | Space charge                                               |

| $Q_{ss}$     | Charge at the semiconductor surface                        |

| ρ            | Charge density                                             |

| $\rho(E_T)$  | 2D density of states                                       |

| $S_{av}$     | Average swing                                              |

| $S_{pt}$     | Point swing                                                |

| T            | Temperature                                                |

| T(E)         | Tunneling probability at a given energy $E$                |

| $t_{ox}$     | Oxide thickness                                            |

| $t_{Si}$     | Silicon thickness                                          |

| U            | Potential energy                                           |

| $v_x$        | Carrier velocity in the $x$ -direction                     |

| V            | Applied bias                                               |

| $V_{bi}$     | Built–in potential                                         |

| $V_{DD}$     | Supply voltage                                             |

| $V_{ds}$     | Drain–to–source voltage                                    |

| $V_{ds,sat}$ | Drain voltage at which the output characteristic saturates |

| $V_{fb}$     | Flat–band voltage                                          |

| $V_{gs}$     | Gate–to–source voltage                                     |

| $V_{inv}$    | Gate voltage at which inversion layer is formed            |

| $V_{on}$     | Gate voltage at which BTBT starts                          |

| $V_F$        | Forward bias                                               |

| $V_R$        | Reverse bias                                               |

| $V_t$       | Threshold voltage             |

|-------------|-------------------------------|

| $V_{tg(d)}$ | Gate(drain) threshold voltage |

| W           | Depletion width (also $W_D$ ) |

| w           | BTBT barrier width            |

| $w_{min}$   | Minimum BTBT barrier width    |

| $\chi$      | Electron affinity             |

# List of Figures

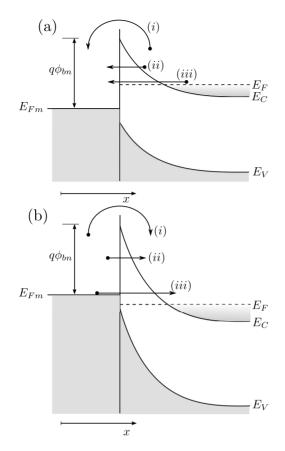

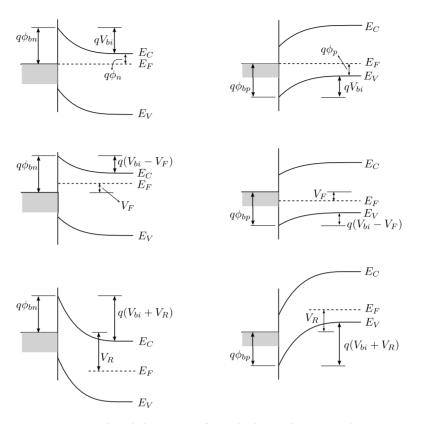

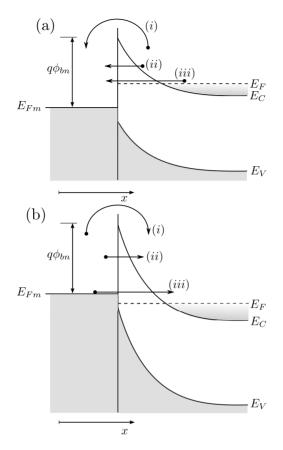

| Principales procesos de inyección de electrones del semi-      |

|----------------------------------------------------------------|

| conductor al metal en una unión metal-semiconductor            |

| (degenerado de tipo n) polarizada en directa (a), y del        |

| metal al semiconductor al polarizar en inversa (b). Los        |

| procesos mostrados son: emisión termoiónica (i), emisión       |

| de campo termoiónica (ii), y emisión de campo desde el         |

| nivel de Fermi (iii)                                           |

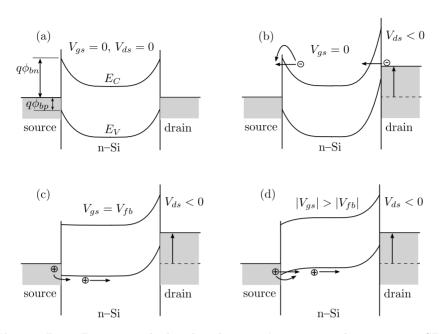

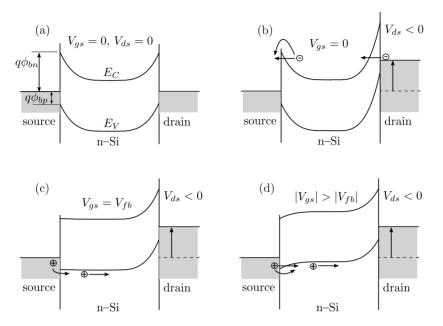

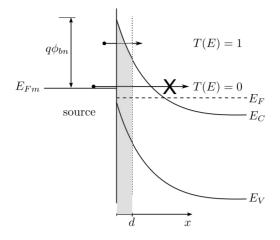

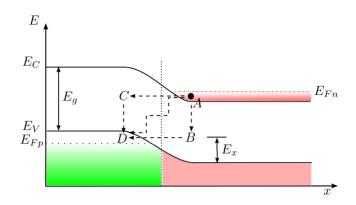

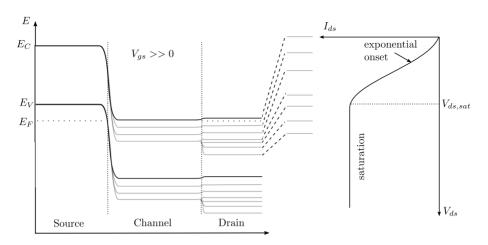

| Diagrama de bandas de energía correspondientes a un            |

| SB–MOSFET de canal p donde se muestran cuatro con-             |

| figuraciones distintas de operación: (a) estado OFF, sin       |

| tensión de drenador; (b) estado OFF, con tensión de            |

| drenador; (c) condición de banda plana (hasta este punto       |

| y viniendo de las situaciones anteriores sólo existe emisión   |

| termoiónica); (d) estado ON donde la inyección por efecto      |

| túnel está presente                                            |

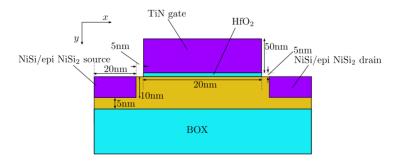

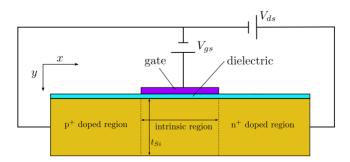

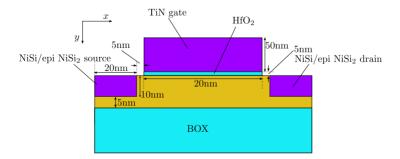

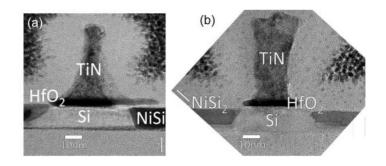

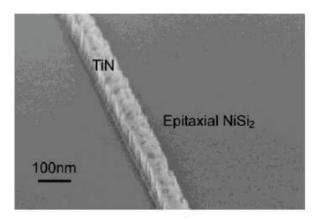

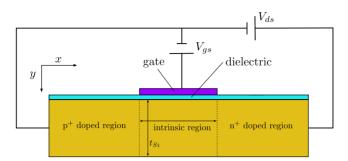

| Sección transversal y dimensiones (no representadas a es-      |

| cala) de los SB–MOSFETs con fuente y drenador de NiSi          |

| y NiSi <sub>2</sub> estudiados en esta tesis xli               |

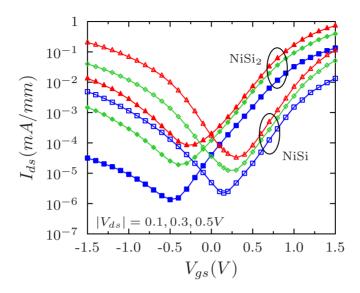

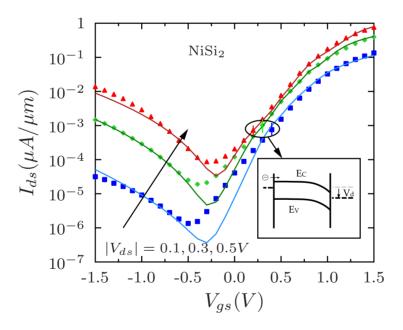

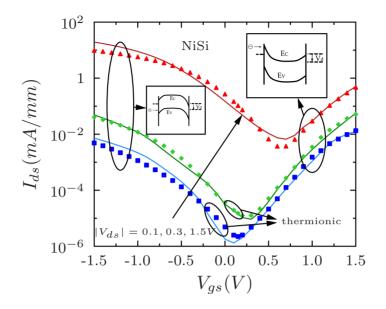

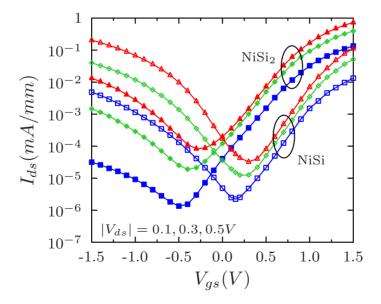

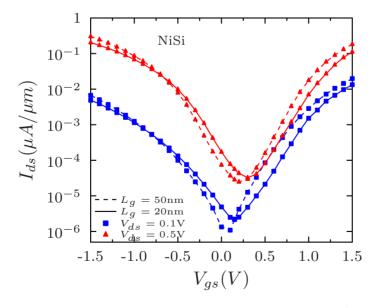

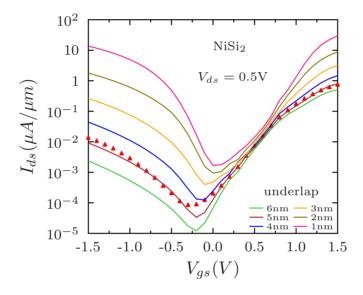

| Características de transferencia experimentales correspon-     |

| dientes a los SB–MOSFETs con NiSi y NiSi $_2$ epitaxial        |

| para una longitud de puerta de $L_g = 20$ nm. $V_{ds} = 0.1$ , |

| 0.3 y 0.5V                                                     |

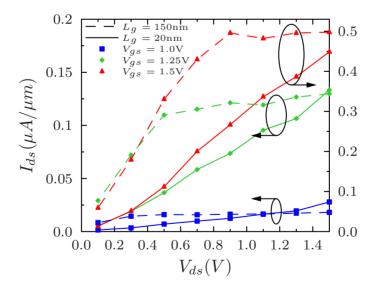

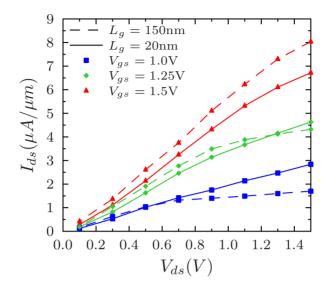

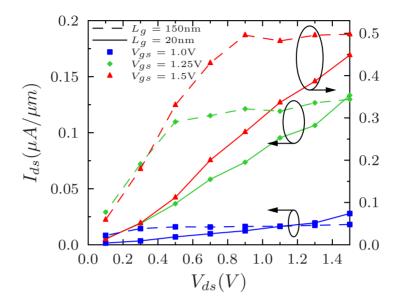

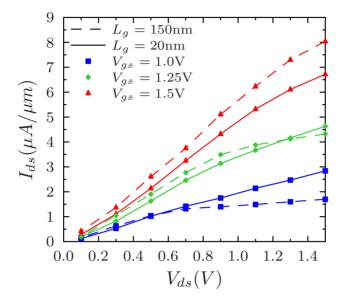

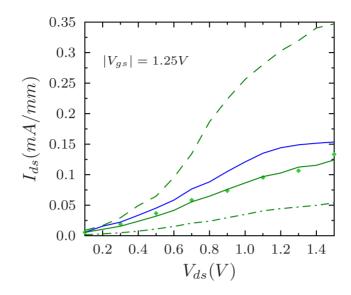

| Características de salida experimentales de los SB–MOSFETs     |

| con NiSi para longitudes de puerta $L_g = 20$ y 150nm.         |

| $V_{gs}=1.0,\ 1.25$ y 1.5V                                     |

|                                                                |

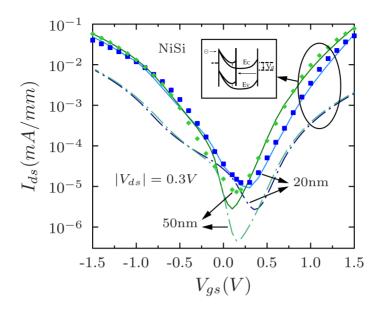

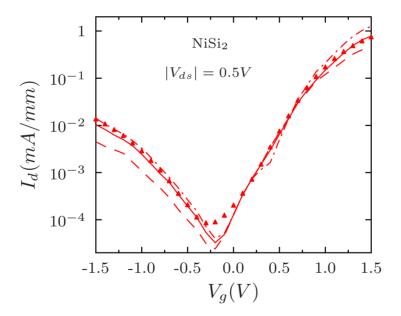

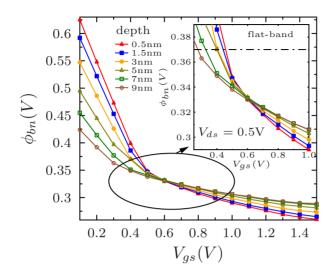

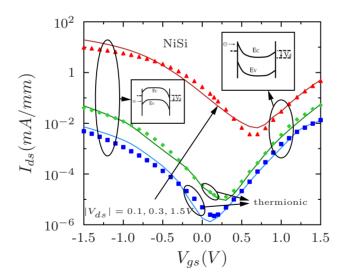

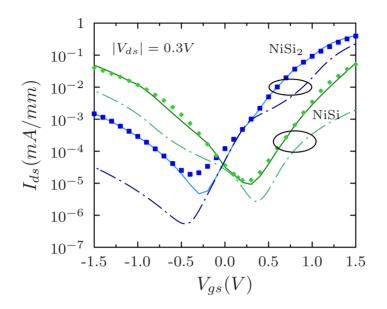

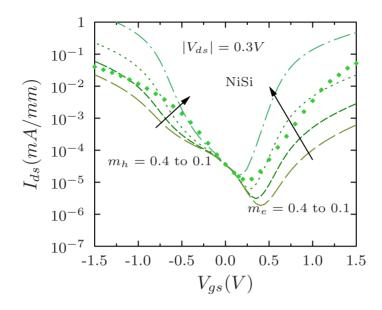

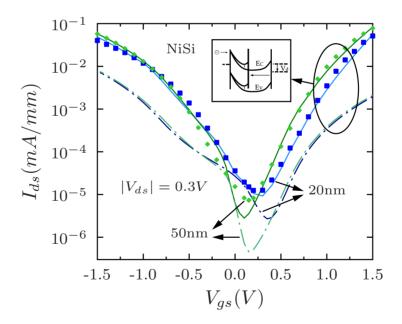

- I.8 Curvas  $I_{ds} V_{gs}$  correspondientes al SB-MOSFET con NiSi para  $V_d = 0.1, 0.3 \text{ y} 1.5V$ . Los símbolos marcan valores experimentales; las líneas continuas, los simulados. En este caso,  $m_h = 0.8 \text{ y} m_e = 0.4. \ldots \text{ xlv}$

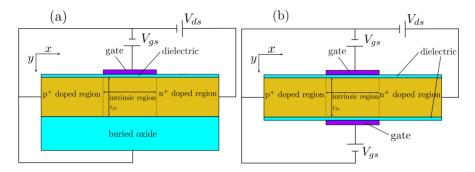

- I.10 TFET de puerta única. La región p<sup>+</sup> actúa como fuente mientras que la n<sup>+</sup> actúa como drenador.  $\ldots \ldots \ldots$  xlvii

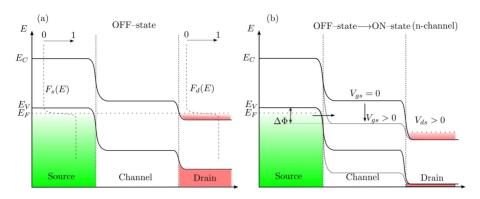

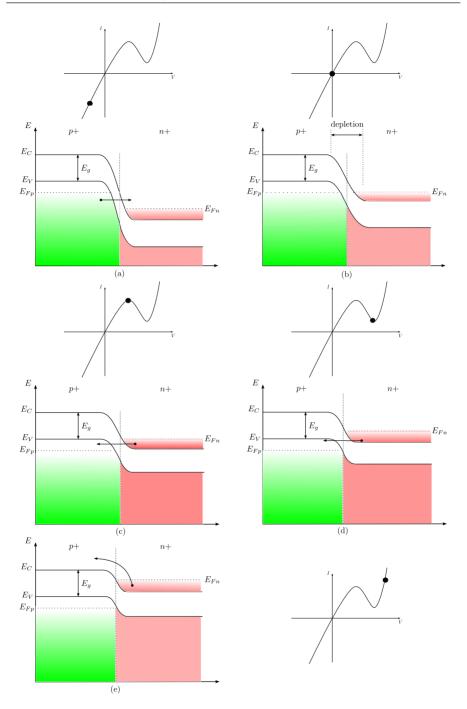

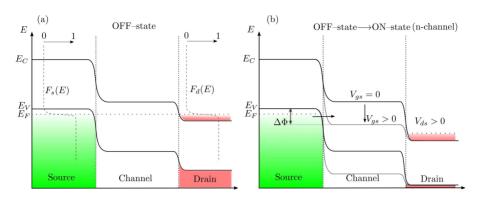

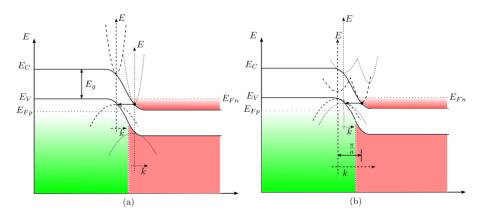

| I.11 | Diagrama de bandas de energía del TFET correspondi-                 |

|------|---------------------------------------------------------------------|

|      | ente a un corte horizontal a lo largo del canal y próximo           |

|      | al aislante de puerta. (a) Estado OFF asociado a la                 |

|      | situación de equilibrio donde no hay ninguna tensión apli-          |

|      | cada en la puerta ni en el drenador. (b) Combinación de             |

|      | estados ON y OFF. Al aplicar una tensión de drenador,               |

|      | si no se aplica tensión alguna en la puerta, el efecto túnel        |